## 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 설계

Design of Partial Predistortion Balanced Power Amplifier

2006年 8月22日

全北大學校大學院 情報通信工學科

鄭熙永

## 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 설계

Design of Partial Predistortion Balanced Power Amplifier

2006 年 8月 22日

全北大學校大學院 情報通信學工科 鄭 熙 永

# 부분적인 전치왜곡 선형화기를 적용한 평 형 전력증폭기의 설계

## 指導教授 鄭龍 采

이 論文을 工學 碩士 學位 論文으로 提出함.

2006年5月15日

## 鄭熙永의 碩士 學位 論文을 認准함

主審 全北大學校 丁恒根 印

委員全北大學校 高榮浩 印

委員 全北大學校 鄭龍 采 印

2006年 6月 19日

全北大學校大學院

### 차 례

| Abstract                                       |   |

|------------------------------------------------|---|

| 제 1 장 서 론                                      | 1 |

| 제 2 장 대전력 중폭기의 비선형 특성                          |   |

| 제 1 절 진폭 왜곡(AM-to-AM) 특성 분석                    | 4 |

| 제 2 절 위상 왜곡(AM-to-PM) 특성 분석 ·····              | 9 |

| 제 3 장 대전력 증폭기의 선형화 방식                          |   |

| 제 1 절 입력 전력 Back-off 방식1                       | 5 |

| 제 2 절 궤환(Feedback) 방식 ······1                  | 6 |

| 제 3 절 피드포워드(Feedforward) 방식 ······1            | 7 |

| 제 4 절 전치왜곡(Predistortion) 방식 ·····2            | О |

| 제 4 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기             |   |

| 제 1 절 전체 회로 구성 및 동작 원리2                        | 1 |

| 제 2 절 루프 별 동작 원리2                              | 4 |

| 제 5 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 구성 회로 설계   | 1 |

| 제 1 절 90° 하이브리드(hybrid) 회로 ·····3              | 1 |

| 제 2 절 가변 위상 변환기3                               | 3 |

| 제 3 절 저 위상 가변 감쇠기4                             | 1 |

| 제 4 절 동위상 전력 분배기/합성기4                          | 8 |

| 제 5 절 신호 상쇄 이론5                                | 3 |

| 제 6 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 성능 측정 및 분석 |   |

| 제 1 절 주 전력증폭기 및 전치왜곡 전력증폭기5                    | 6 |

| 제 2 절 주 신호 제거 루프5                              | 9 |

| 제 3 젘 폇혓 전력증폭기 루프6                             | 1 |

| 제 4 절 측정 결과 및 분석 | 64 |

|------------------|----|

| 제 7 장 결 론        | 71 |

| 참고문헌             | 73 |

## 그 림 차 례

| 그림 | 2.1 | 전력증폭기의 AM-to-AM 특성 ······6          |

|----|-----|-------------------------------------|

| 그림 | 2.2 | 1-tone 신호에 대한비선형 주파수 응답 특성6         |

| 그림 | 2.3 | 2-tone 신호 입력 시 비선형 주파수 응답 특성9       |

| 그림 | 2.4 | 대전력 증폭기의 비선형 모델10                   |

| 그림 | 2.5 | 전력증폭기의 비선형 특성11                     |

| 그림 | 3.1 | 입력 전력 Back-off와 동작점 ·····15         |

| 그림 | 3.2 | 궤환 방식 선형화기의 기본 회로도17                |

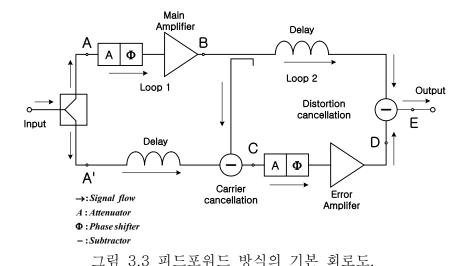

| 그림 | 3.3 | 피드포워드 방식의 기본 회로도19                  |

| 그림 | 3.4 | 피드포워드 방식의 동작 원리19                   |

| 그림 | 3.5 | 전치왜곡 방식 선형화기 동작 원리20                |

| 그림 | 4.1 | 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 전체 블  |

|    |     | 록도23                                |

| 그림 | 4.2 | 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 동작 원리 |

|    |     | 25                                  |

| 그림 | 4.3 | 주 신호 제거 루프의 동작 원리27                 |

| 그림 | 4.4 | 평형 전력증폭기 루프의 동작 원리28                |

| 그림 | 4.5 | 오차 신호 주입 루프의 동작 원리29                |

| 그림 | 5.1 | 90° 하이브리드 회로32                      |

| 그림 | 5.2 | S03B2150N3의 동작 특성 ······33          |

| 그림 | 5.3 | 바렉터 다이오드의 등가회로35                    |

| 그림 | 5.4 | 가변 위상 변환기에 사용된 결합기36                |

| 그림 | 5.5 | 가변 위상 변환기의 반사계수 산출36                |

| 그림 | 5.6 | 90° 하이브리드를 이용한 반사형 가변 위상 변환기 회로38   |

| 그림 | 5.7 가변 위상 변환기 측정 결과39                         |

|----|-----------------------------------------------|

| 그림 | 5.8 반사형 감쇠기의 등가회로41                           |

| 그림 | 5.9 PIN 다이오드의 접합저항 변화에 따른 반사계수 크기 특성42        |

| 그림 | 5.10 PIN 다이오드의 접합저항 변화에 따른 반사계수 위상 특성 …43     |

| 그림 | 5.11 반사형 저 위상 가변 감쇠기44                        |

| 그림 | 5.12 저 위상 가변 감쇠기의 측정 결과46                     |

| 그림 | 5.13 Wilkinson 전력 분배기 ······48                |

| 그림 | 5.14 Wilkinson 전력 합성기의 우, 기 모드 여기 모델49        |

| 그림 | 5.15 변화된 Wilkinson 전력 합성기의 우, 기 모드 여기 모델50    |

| 그림 | 5.16 Wilkinson 출력 단자 1, 2 특성 ······53         |

| 그림 | 5.17 경로간 진폭/이득 불일치에 따른 신호 상쇄도55               |

| 그림 | 6.1 MA와 PDMA의 이득 측정 결과 ······57               |

| 그림 | 6.2 MA와 PDMA의 ACPR 특성 측정 결과 ·····58           |

| 그림 | 6.3 주 신호 제거 루프의 블록도59                         |

| 그림 | 6.4 주 신호 제거 루프의 측정 결과60                       |

| 그림 | 6.5 평형 전력증폭기 루프62                             |

| 그림 | 6.6 평형 전력증폭기의 측정 결과63                         |

| 그림 | 6.7 선형화 개선 특성 측정을 위한 블록도64                    |

| 그림 | 6.8 제안된 PPBA의 혼변조 왜곡 특성(@Pout=40dBm) ······65 |

| 그림 | 6.9 제안된 PPBA의 혼변조 왜곡 특성(@Pout=41dBm) ······66 |

| 그림 | 6.10 동적 출력 전력 레벨에 따라 ACPR 개선 특성 ······70      |

# 표 차 례

| 표 | 2.1 | 전력증폭기의 비선형 출력 주파수 성분8                 |

|---|-----|---------------------------------------|

| 丑 | 5.1 | 3dB 하이브리드 결합기 (S03B2150N3)의 사양32      |

| 丑 | 5.2 | 가변 위상 변환기 측정 결과40                     |

| 丑 | 5.3 | 제작된 저 위상 가변 감쇠기의 측정 결과47              |

| 丑 | 5.4 | Wilkinson 전력 분배기의 측정 결과 ·····52       |

| 丑 | 6.1 | 제안된 PPBA의 동적 전력 레벨에 따른 개선 전 ACPR 특성67 |

| 丑 | 6.2 | 제안된 PPBA의 동적 전력 레벨에 따른 개선 후 ACPR 특성68 |

| 표 | 6.1 | 제안된 PPBA의 동적 전력 레벨에 따른 ACPR 개선량69     |

### Design of Partial Predistortion Balanced Power Amplifier

Jeong Hee Young

Department of Information and Communication Engineering

Chonbuk National University

#### Abstract

In this thesis, a method and apparatus for reducing distortion in the output port of a balanced power amplifier samples the error signal of the main power amplifier (MA) output. A circuit that can provide these features measures the difference between the output from one of the balanced power amplifiers and a sample of the amplifier input. This difference signal, which represents the amplifier distortion, can then be combined at the input to another portion of the balanced power amplifier. The amplitude and phase of the difference signal can be adjusted such that the distortion produced from the respective portions of the balanced power amplifier are cancelled when the respective outputs are combined to produce the balanced power amplifier output. The proposed technique uses one portion of the balanced power amplifier to amplify the difference signal to the desired level and thereby does not require an error amplifier. Also, because the difference signal is injected into the input signal in front of the predistortion main power amplifier (PDMA), this technique does not require additional couplers following the MA output. For a forward link 4-FA

WCDMA signal, measured ACPR improvements were 23.01dB at 12.5MHz offset from center frequency for the output power 40dBm.

### 제 1 장 서론

고도의 정보화 시대가 급속히 도래함에 따라 통신 분야의 눈부신 발전이 이 루어지고 있으며, 정보통신의 수요가 급격히 증가하고 시·공간의 제약을 받지 않는 이동통신 및 위성통신 등의 무선을 이용한 개인 통신의 수요 또한 점점 확대되어 가고 있다. 한편 한국 통신이 2006년 중 후반에 실시할 계획인 Wibro 상용 서비스에 모바일 RFID 서비스도 포함시킬 것이라고 전망되고 있 다. 이와 같이 이동통신 서비스의 다양화 및 데이터의 증가로 인한 광대역화 및 고품질화가 절실히 요구되고 있으며, 이러한 통신기술의 진화에 발 맞추어 다양한 통신 방식의 연구가 진행되고 있으며, 그 일환으로 단말기의 성능 및 무선 기지국 시스템의 성능을 극대화시키기 위한 연구가 활발히 이루어지고 있 다. 이동통신 기기의 성능은 기기에 사용되는 고주파 소자들에 의해서 상당 부 분 결정되므로 고주파 소자들에 대한 기술 개발이 절실히 요구된다. 특히 이동 통신용 고주파 소자는 기기의 성능을 좌우하는 핵심부품으로 고효율화 및 선형 성 향상 측면에서 다양한 연구가 이루어지고 있고, 급격히 증가하는 이동통신 이용자들을 한정된 주파수 자원으로 원활히 수용하기 위하여 우수한 선형성 및 고효율 특성이 요구되는 선형 전력증폭기는 이동통신 시스템의 필수 요소로 현 재까지 통신 산업에서 중요한 연구 대상이 되어왔다[1]. 전력증폭기 개발에서 기술의 핵심은 현재 보편화되고 있는 WCDMA 방식의 경우에서처럼 소자의 비선형성에 의한 혼변조 왜곡으로 인한 통신의 방해 요소들을 최소화하여 통신 의 성능을 저하시키는 요인을 충분히 제거하고자 하는 것이다. 일반적으로 전 력증폭기는 진폭 및 위상의 비선형 특성이 고려되어야 하는데, 선형 전력증폭 기에서 입력 반송파를 증폭했을 때, 선형성에 직접적으로 영향을 미치는 진폭의 왜곡(AM-to-AM)과 위상의 왜곡(AM-to-PM)을 말한다<sup>[2]</sup>. 이러한 왜곡은 다중신호 전송 시, 여러 개의 반송파 신호를 동시에 보내는 것과 같이 전력세기가 시간에 대하여 일정하지 않고 변하는 경우에는 입력 신호의 비선형성외에도 혼변조 왜곡 성분(IMD: <u>Inter-M</u>odulation <u>D</u>istortion)이 발생하여 출력 신호를 왜곡시킬 뿐만 아니라, 스펙트럼 재성장(spectral regrowth)에 의한인접 채널 간섭을 일으키는 원인이 된다. 따라서 이러한 왜곡 성분들을 최소화하고 선형적인 영역을 최대로 확장하는 선형화 기법들에 대한 연구가 활발히진행되고 있다.

현재까지 알려진 전력증폭기의 선형화 방안에는 Back-off 방식, 궤환 (Feedback)방식, 아날로그 및 디지털 전치왜곡(Predistortion) 방식, 그리고 피드포워드(Feedforward) 방식 등이 있다<sup>[3][4]</sup>. 여기서 고출력 전력 증폭기에 대해 수 dB Back-off하여 선형 영역에서 동작되도록 하면 혼변조 잡음은 줄일 수 있으나, 출력 전력 레벨이 낮아지며, 출력 전력 레벨을 단일 반송파만 사용할 때와 같은 크기로 키우기 위해서는 여러 개의 전력증폭기를 병렬로 접속해야 하므로 용적이 커지고 효율이 낮아지며 큰 용량의 전원 공급기가 요구되는 단점을 가지고 있다<sup>[5]</sup>. 그리고 아날로그 전치왜곡 방식은 소형 경량으로 구현이 가능하다는 측면에서 많이 응용되고 있지만, 비선형성 개선 효과는 피드포워드 방식에 미치지 못하며, 넓은 주파수 대역 및 동작영역(dynamic range)에서 선형화 개선 효과를 얻기가 어렵다는 단점을 가지고 있다. 궤환 방식은 동작 대역폭의 한계와 발진의 가능성으로 그 적용 범위의 한계성을 지니고 있다. 디지털 전치왜곡 방식은 기저대역의 신호에 전치왜곡을 함으로 RF 회로에다. 디지털 전치왜곡 방식은 기저대역의 신호에 전치왜곡을 함으로 RF 회로에다.

서의 비선형성을 보상하는 것으로 부궤환 지연시간과 RF 전력증폭기의 기억효과(memory effect) 때문에 비교적 협대역에서만 양호한 동작 특성을 나타내고 있다. 반면에 피드포워드 방식은 이론적으로 모든 왜곡 신호들에 대해 탁월한 선형성 개선 특성과 넓은 주파수 대역에서도 적용가능하기 때문에 상당히 매력적이며, 특히 다른 기술들에 비해 동적인 채널 할당에 더욱 적합하다는 장점이 있어 이동통신 기지국 및 위성통신 시스템용 전력증폭기에 응용되어 왔지만 일반적으로 낮은 전력효율을 가지고 있기 때문에 피드포워드 선형화 방식은 크게 선형성과 전력 효율적인 측면에서 추가적인 연구의 필요성이 요구되고 있다 다[6]. 따라서 본 연구에서는 이러한 피드포워드 선형화 방식에서의 장점을 이용하되 새로운 구조의 부분적인 전치왜곡 선형화 기법을 적용한 평형 전력증폭기를 제안하였다.

본 논문에서는 부분적인 전치왜곡 선형화 기법을 적용한 평형 전력증폭기 성능 규명을 중심으로 분석할 것이다. 서론에 이어 제2장에서는 진폭 및 위상 왜곡 특성을 가지는 대전력 증폭기의 비선형 특성을 분석하는 방법을 제시할 것이다. 제3장에서는 대표적인 몇 가지 선형화 방식의 동작원리에 대해 언급을하고, 제4장에서는 본 논문에서 제안하고자 하는 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 전체 회로 및 루프 별 동작원리에 대해 알아볼 것이다. 제5장에서 그 구성 회로 설계에 대한 설계 이론 및 측정결과에 대해설명할 것이다. 이러한 이론적 배경을 토대로 각 동작 루프 별 측정 결과와 전체 회로의 선형화 측정 결과를 통해 성능 규명이 이루어지며, IMT-2000 4FA 신호를 인가하여 인접채널 전력비의 개선 정도를 측정하였다.

### 제 2 장 대전력 증폭기의 비선형 특성

#### 제 1 절 진폭 왜곡(AM-to-AM) 특성 분석

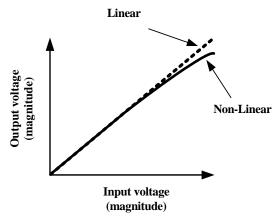

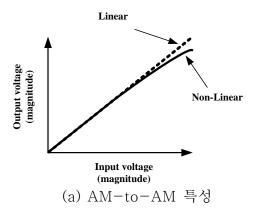

대전력 증폭기의 비선형 전달 특성으로 인해 입력 전력 레벨의 증가에 따라 출력의 상대이득이 감소하는 현상이 있으며, 입력 전압의 크기에 대한 함수로 나타낼 수 있다.

2단자 망이 기억성이 없다면 출력 특성은 입력에 대해서 동시성을 갖는다고 가정을 할 수가 있고 이것은 입력 전압  $v_i(t)$ 와 출력 전압  $v_o(t)$ 의 관계식으로 나타낼 수 있다. 만약 2단자 망이 완전한 선형 전달 특성을 가진다면 입력과 출력의 관계는 아래와 같은 관계식으로 나타낼 수 있으며 출력 전압은 입력 전압의 상수 k배로 표현할 수 있다 [7][8]

$$v_o = kv_i \tag{2.1}$$

2단자 망이 비선형 전달 특성을 갖는다면 출력 전압  $v_o(t)$ 은 입력 전압의 멱급수(power series)로 표현될 수 있다.

$$v_o = k_1 v_i + k_2 v_i^2 + k_3 v_i^3 + \dots + k_n v_i^n$$

(2.2)

식 (2.1)과 식(2.2)은 입력에 따라 출력에서 위상변화를 일으키는 2단자 망의 위상 왜곡 특성을 무시한 것이다. 비선형 전달 특성 분석을 할 때 강한 비선형 특성을 요구하는 2단자 망이 아닌 경우는 식

(2.3)과 같이 세 번째 항만으로도 충분히 비선형 전달 특성을 표현 할수 있다.

$$v_o = k_1 v_i + k_2 v_i^2 + k_3 v_i^3 (2.3)$$

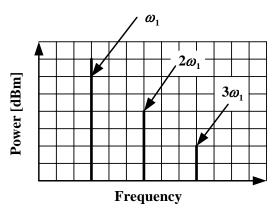

입력 신호 전압이  $v_i = A\cos\omega_i t$  라면 출력 전압 특성은 식 (2.4)와 같이 나타낼 수 있으며 출력 신호의 구성을 살펴보면 기본 주파수  $\omega_i$  과 dc,  $2\omega_i$ ,  $3\omega_i$ 의 스퓨리어스(spurious) 신호가 동반됨을 알수가 있다.

$$\begin{aligned} v_o &= k_1 A \cos \omega_1 t + k_2 A^2 \cos^2 \omega_1 t + k_3 A^3 \cos^3 \omega_1 t \\ &= k_1 A \cos \omega_1 t + k_2 A^2 (\frac{1}{2} + \frac{1}{2} \cos 2\omega_1 t) + k_3 A^3 (\frac{3}{4} \cos \omega_1 t + \frac{1}{4} \cos 3\omega_1 t) \\ &= \frac{1}{2} k_2 A^2 + (k_1 A + \frac{3}{4} k_3 A^3) \cos \omega_1 t + \frac{1}{2} k_2 A^2 \cos 2\omega_1 t + \frac{1}{4} k_3 A^3 \cos 3\omega_1 t \end{aligned} \tag{2.4}$$

식 (2.4)에서 기본 주파수  $\omega_1$ 의 출력 신호 진폭을 보면  $k_1A+(3/4)k_3$   $A^3$ 인데  $k_3<0$  이면  $k_1A>k_1A+(3/4)k_3A^3$ 이 되므로 가상 선형 출력 신호  $(k_1A\cos\omega_1t)$ 의 진폭보다 작게 된다. 이것을 이득의 감소(gain compression) 또는 AM-to-AM 변화 특성이라고 한다.

입력 신호가 작을 때는 신호의 왜곡이 비교적 적은 선형 영역에서 동작 하지만 입력 신호의 크기가 커지면 비선형 전달 특성을 일으키는 신호의 진폭 왜곡이 심해진다. 그림 2.1은 대전력 증폭기의 비선형 전달 특성 중에 진폭 왜곡(AM-to-AM) 특성을 나타내고 있다. 입력 신호 전압이  $v_i = A\cos\omega_i t$ 일 때 즉, 1-tone 신호를 비선형 전달 특성

을 가지는 2단자 망에 인가했을 때 비선형 주파수 응답 특성은 그림 2.2에 나타내고 있다.

그림 2.1 전력증폭기의 AM-to-AM 특성.

Fig. 2.1 AM-to-AM characteristic of power amplifiers.

그림 2.2 1-tone 신호에 대한 비선형 주파수 응답 특성.

Figure 2.2 Nonlinear frequency response for one-tone signal.

주파수는  $\omega_1, \omega_2$  이면서 동일 진폭을 갖는 정현파  $v_i = A(\cos \omega_1 t + \cos \omega_2 t)$ 가 입력되면 출력은 다음과 같다<sup>[9]</sup>.

$$v_{o} = k_{1}A(\cos\omega_{1}t + \cos\omega_{2}t) + k_{2}A^{2}(\cos\omega_{1}t + \cos\omega_{2}t)^{2} + k_{3}A^{3}(\cos\omega_{1}t + \cos\omega_{2}t)^{3}$$

$$= k_{2}A^{2} + k_{2}A^{2}\cos(\omega_{1} - \omega_{2})t + (k_{1}A + \frac{9}{4}k_{3}A^{3})\cos\omega_{1}t + (k_{1}A + \frac{9}{4}k_{3}A^{3})\cos\omega_{2}t + \frac{3}{4}k_{3}A^{3}\cos(2\omega_{1} - \omega_{2})t$$

$$+ \frac{3}{4}k_{3}A^{3}\cos(2\omega_{2} - \omega_{1})t + k_{2}A^{2}\cos(\omega_{1} + \omega_{2})t + \frac{1}{2}k_{2}A^{2}\cos2\omega_{1}t + \frac{1}{2}k_{2}A^{2}\cos2\omega_{2}t + \frac{3}{4}k_{3}A^{3}\cos(2\omega_{1} + \omega_{2})t + \frac{3}{4}k_{3}A^{3}\cos(2\omega_{2} + \omega_{1})t + \frac{1}{4}k_{3}A^{3}\cos3\omega_{1}t + \frac{1}{4}k_{3}A^{3}\cos3\omega_{2}t$$

$$(2.5)$$

기본 주파수가  $\omega_1$ ,  $\omega_2$  인 입력 신호에 대해 출력 단에서는 기본 주파수  $\omega_1$ ,  $\omega_2$  외에 dc, 제2차 고조파 주파수  $2\omega_1$ ,  $2\omega_2$  와 제3차 고조파 주파수  $3\omega_1$ ,  $3\omega_2$  와 제2차 혼변조 주파수  $\omega_1 \pm \omega_2$  와 제3차 혼변조 주파수  $2\omega_1 \pm \omega_2$ ,  $2\omega_2 \pm \omega_1$  인 출력 신호가 얻어진다. 보통 증폭기의 동작 주파수 대역은 octave 대역보다 작으므로 스퓨리어스 신호 중 dc,  $\omega_1 \pm \omega_2$ ,  $2\omega_1$ ,  $2\omega_2$ ,  $2\omega_1 + \omega_2$ ,  $2\omega_2 + \omega_1$ ,  $3\omega_1$ ,  $3\omega_2$  인 주파수 성분은 동작 주파수 대역의 외부에 위치하므로 적당한 여파기를 쓰면 제거할 수 있으나, 제3차 혼변조 신호는 기본 주파수  $\omega_1$ ,  $\omega_2$ 에 인접해서 있으므로 기본 주파수에 왜곡을 주게 된다. 이러한 왜곡을 여파기를 사용하여 제거가 어렵기 때문에 선형화기를 반드시 사용해서 통신 시스템의 성능을 향상 시켜야 한다. 그림 2.3은 비선형

2단자 망에 2-tone 신호를 인가 시 출력 스펙트럼(spectrum)을 나타내고 있다<sup>[10]</sup>.

표 2.1 전력증폭기의 비선형 출력 주파수 성분.

Table 2.1 Nonlinear output frequency components of amplifier.

| DC term               | $k_2A^2$                                                                                                                                                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fundament             | $k_1 A \left(1 + \frac{9k_3 A^2}{4k_1}\right) \left(\cos \omega_1 t + \cos \omega_2 t\right)$                                                                                                                                |

| 2 <sup>nd</sup> order | $\frac{k_2 A^2}{2} (\cos 2\omega_1 t + \cos 2\omega_2 t) \cdots + k_2 A^2 (\cos(\omega_1 + \omega_2)t + \cos(\omega_1 - \omega_2)t)$                                                                                         |

| 3 <sup>rd</sup> order | $\frac{k_3 A^3}{4} (\cos 3\omega_1 + \cos 3\omega_2)t + \frac{3k_3 A^3}{4} (\cos(2\omega_1 + \omega_2)t + \cos(2\omega_1 - \omega_2)) \cdots \frac{3k_3 A^3}{4} (\cos(2\omega_2 + \omega_1)t + \cos(2\omega_2 - \omega_1)t)$ |

그림 2.3 2-tone 신호 입력 시 비선형 주파수 응답 특성. Figure 2.3 Nonlinear frequency response in case of 2-tone signals input.

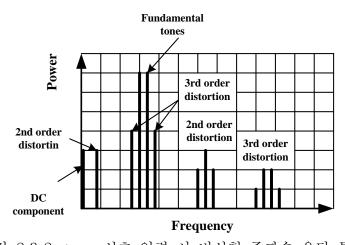

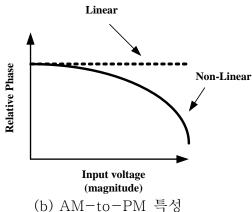

#### 제 2 절 위상 왜곡(AM-to-PM) 특성 분석

앞 절에서 분석 하였던 멱급수(power series)는 신호의 진폭에 따라 위상의 변화를 가져오는 위상왜곡(AM-to-PM) 특성을 표현할 수없다. 신호왜곡에 대한 멱급수 표현식들은 위상왜곡(AM-to-PM) 특성을 무시할 수 있을 때만 적당하다. 일반적인 대전력 증폭기에서는 진폭과 위상의 비선형성이 모두 기억성을 가지고 존재하며, 이것은 등가적으로 왜곡을 가지는 시스템이 주파수 의존적임을 나타내고 있다. 비교적 약하게 비선형성이 나타나는 영역에서 혼변조의 특성을 해석하기 위하여 Volterra-series 분석법이 종종 사용된다[26].

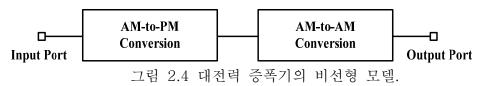

대전력 증폭기의 위상왜곡(AM-to-PM) 특성의 변화를 고려하여 비선형 전력증폭기는 그림 2.4와 같이 캐스캐이드(cascade)로 연결된 비선형 소자들로 모델화 될 수 있다.

Figure 2.4 Nonlinear model of high power amplifier.

그림 2.4에서와 같이 대전력 증폭기의 비선형 전달 함수는 위상의 왜곡 특성을 초래하는 AM-to-PM 변환 소자와 진폭의 왜곡 특성을 초래하는 AM-to-AM 변환 소자들의 구성으로 모델화하여 분석할 수 있다. 그림 2.5(a)는 비선형 전달 특성 중에 진폭왜곡(AM-to-AM) 특성을 나타내고 있고, 그림 2.5(b)는 위상왜곡(AM-to-PM)의 일반적인 특성을 나타내고 있다.

(a) AM-to-AM characteristics

(b) AM-to-PM 특성 (b) AM-to-PM characteristics

그림 2.5 전력증폭기의 비선형 특성. Figure 2.5 Nonlinear characteristics of power amplifier.

이 비선형 전달 특성을 가진 대전력 증폭기의 입력 단자에  $v_i=A\cos\omega t$ 의 입력 신호를 인가하면 그림 2.4의 블록도에서 위상왜곡(AM-to-PM) 특성에 기인하여 출력 전압은 다음과 같은 식으로 표현할 수 있다.

$$v_{im} = A\cos\left[\omega t + \phi\left(\frac{A^2}{2}\right)\right] \tag{2.6}$$

여기서  $\phi(A^2/2)$ 는 진폭변조에 의한 위상의 변화된 값을 의미한다. 또한 Volterra-series를 이용하여 식 (2.6)과 같은 결과 식에 진폭 왜곡(AM-to-AM) 특성을 적용하면 대전력 증폭기의 출력 전압은 다음과 같은 식으로 구할 수 있다.

$$v_{out} = \sum_{n=1}^{\infty} a_n v_{im}^n = \sum_{n=1}^{\infty} a_n A^n \cos^n \left[ \omega t + \phi \left( \frac{A^2}{2} \right) \right]$$

(2.7)

주파수는  $\omega_1$ ,  $\omega_2$ 이면서 동일 진폭을 갖는 입력 전압은

$$v_{i} = A'(\cos \omega_{1} t + \cos \omega_{2} t)$$

$$= 2A'\cos \frac{\omega_{1} - \omega_{2}}{2} t \cdot \cos \frac{\omega_{1} + \omega_{2}}{2} t$$

$$= e(t)\cos \frac{\omega_{1} + \omega_{2}}{2} t$$

(2.8)

여기서 e(t) 는  $2A'\cos\frac{\omega_1-\omega_2}{2}t$  이고, 수학적인 편의를 위하여 단일 입력 신호  $v_iA\cos\omega t$  와 비교하면 다음과 같이 표현할 수 있다.

$$A = e(t) = 2A\cos\frac{\omega_1 - \omega_2}{2}t, \quad \omega = \frac{\omega_1 + \omega_2}{2}$$

(2.9)

여기서 식 (2.9)을 식 (2.7)에 대입하여 두 입력 신호에 대한 대전력 증폭기의 비선형 출력 전압을 다음과 같이 얻을 수 있다.

$$\begin{aligned} v_{out} &= \sum_{n=1}^{\infty} a_n \left( e(t) \cos \left\{ \frac{\omega_1 + \omega_2}{2} t + \phi \left[ \frac{e(t)^2}{2} \right] \right\} \right)^n \\ &= a_1 A' \left( \cos \left\{ \omega_1 t + \phi \left[ \frac{e(t)^2}{2} \right] \right\} + \cos \left\{ \omega_2 t + \phi \left[ \frac{e(t)^2}{2} \right] \right\} \right) \\ &= a_2 A'^2 \left( \frac{1}{2} \cos \left\{ 2\omega_1 t + 2\phi \left[ \frac{e(t)^2}{2} \right] \right\} + \frac{1}{2} \cos \left\{ 2\omega_2 t + 2\phi \left[ \frac{e(t)^2}{2} \right] \right\} \right) \\ &+ \cos \left\{ (\omega_1 + \omega_2) t + 2\phi \left[ \frac{e(t)^2}{2} \right] \right\} + \cos \left[ (\omega_1 - \omega_2) t \right] + 1 \end{aligned}$$

$$\left(\frac{1}{4}\cos\left\{3\omega_{1}t+3\phi\left[\frac{e(t)^{2}}{2}\right]\right\}+\frac{1}{4}\cos\left\{3\omega_{2}t+3\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{3}{4}\cos\left\{(2\omega_{1}+\omega_{2})t+3\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{3}{4}\cos\left\{(2\omega_{2}+\omega_{1})t+3\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{9}{4}\cos\left\{(2\omega_{1}+\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{9}{4}\cos\left\{(2\omega_{1}+\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{3}{4}\cos\left\{(2\omega_{2}-\omega_{1})t+\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \frac{3}{4}\cos\left\{(2\omega_{2}-\omega_{1})t+\phi\left[\frac{e(t)^{2}}{2}\right]\right\} + \cdots$$

(2.10)

$v_{out}$ 의 성분이  $\omega = \omega_x$ 로 정의되어,  $v_{out}\Big|_{\omega = \omega_x}$ 일 때 기본 주파수 성분  $\omega_1$ 과 제 3차 혼변조 주파수  $2\omega_2 - \omega_1$ 은 식 (2.10)에서 유도할 수 있다. 즉, 출력 전압의 기본 주파수 성분은 다음과 같이 표현할 수 있다.

$$v_{out}\Big|_{\omega=\omega_1} = (a_1 A' + \frac{9}{4} a_3 A'^3 + \cdots) \cdot \cos\left\{\omega_1 t + \phi \left[\frac{e(t)^2}{2}\right]\right\}$$

(2.11)

그리고 제 3차 혼변조 주파수  $2\omega_2-\omega_1$  성분은 식 (2.12)과 같이 정리할 수 있다.

$$v_{out}\Big|_{\omega=2\omega_2-\omega_1} = (\frac{3}{4}a_3A'^3 + \cdots) \cdot \cos\left\{(2\omega_2 - \omega_1)t + \phi\left[\frac{e(t)^2}{2}\right]\right\}$$

(2.12)

만약 AM-to-PM 변환에 의한 상호 변조 왜곡 생성이 무시될 수 있다고 가정한다면,  $\cos\left\{\omega_x t + \phi \left[\frac{e(t)^2}{2}\right]\right\}$  항은 어떤 상호 변조적 왜곡 성분도 생성하지 않을 것이다.

따라서 식 (2.11)와 식 (2.12)은 AM-to-PM 변환에 의해서 생성되는 제3차 혼변조 주파수 성분의 생성이 AM-to-AM 변환에 의해서 생성되는 것과 비교하여 무시할 정도로 작을 때 기본주파수와 제3차 혼변조 주파수는 입력 전력 e(t)/2에 대한 동일한 상대적인 위상변환 특성을 갖는다.

### 제 3 장 대전력 증폭기의 선형화 방식

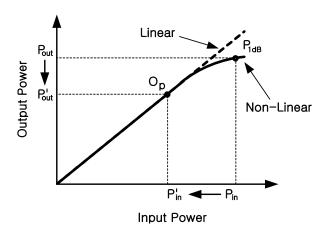

#### 제 1 절 입력 전력 Back-off 방식

입력 신호 전력을 포화 영역(1-dB compression point)때의 입력 레벨보다 적게 Back-off하여 포화 영역 보다 비교적 선형 영역에서 동작시키는 선형화 방식을 입력 전력 Back-off 방식이라고 한다. 그림 3.1은 대전력 증폭기가 최대 입력 신호 전력을 포화 영역(1-dB compression point)때의 입력 레벨보다 적게 입력 Back-off하여 포화영역 보다 비교적 선형 영역에서 동작시키는 선형화 방식을 입력 전력 Back-off 방식이라고 한다<sup>[12]</sup>.

그림 3.1 입력 전력 Back-off와 동작점.

Figure 3.1 Input power back-off and operation point.

그림 3.1은 대전력 증폭기가 최대 출력을 낼 수 있는 비선형  $P_{1dB}$ 점과 입력 전력을 Back-off 시켜 선형영역 동작을 하는 동작점 $(O_p)$ 과의 관계를 나타내고 있다. 이러한 방법은 대전력 증폭기에 입력 전력을 적게 인가했으므로 출력 전력도 마찬가지로 적게 출력이 된다.  $P_{1dB}$ 영역까지 대전력 증폭기를 사용할 때 보다 대전력 증폭기의 출력 전력이 감소하므로 동일한 출력을 만들려면 대전력 증폭기를 병렬 접속해야 한다. 이럴 경우 전체 전력 증폭기의 부피가 증가하고 전력 효율의 감소에 따른 방열 문제와 더 큰 용량의 전원 공급기가 필요해지는 단점이 있다.

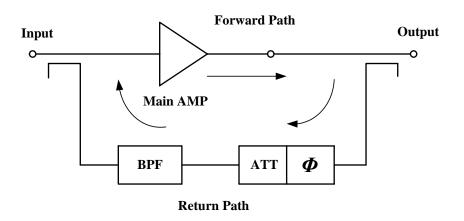

#### 제 2 절 궤환(Feedback) 방식

제환 방식은 출력의 일부를 입력으로 보내고 순수한 입력과 결합해서 최종 출력 단에서는 대전력 증폭기의 출력이 선형성을 갖도록 하는 방식이다. 기본적으로 부궤환(negative feedback) 방법을 이용하는 방식이고 전송 대역폭이 협대역인 경우에 국한하여 사용할 수 있는 방식이다. 기본적인 동작 원리는 입력으로 인가된 반송파는 순방향 경로로진행을 하고 대전력 증폭기 단을 거치면 혼변조 왜곡 신호들을 발생시킨다. 대전력 증폭기의 비선형 특성에 의해서 발생한 혼변조 왜곡 신호의 일부를 추출해서 궤환 경로로 보내고, 이 신호의 크기와 위상을가변 감쇠기와 가변 위상 변환기를 이용해서 조정하고 대전력 증폭기의 입력단에 다시 인가 함으로써 결국 전력증폭기의 출력 단에서는 혼변조 왜곡 신호들을 감소시키게 된다. 이 방식의 단점은 출력 전력의

일부를 부궤환 시킴으로써 이득이 감소하고 발진 가능성이 항상 존재하여 안정도에 문제가 있고 반드시 발진 방지용 대역통과 여파기가 필요하다<sup>[13]</sup>.

그림 3.2 궤환 방식 선형화기의 기본 회로도. Figure 3.2 Basic block diagram of Feedback linearizer amplifiers.

### 제 3 절 피드포워드(Feedforward) 방식

현재 이동 통신 기지국들에 사용되는 전력증폭기들은 고출력, 높은 선형성, 광대역 특성들이 요구되고 있고 이러한 요구 조건을 만족하는 대표적인 선형화 방식은 피드포워드 방식이다. 이 방식은 타 선형화 방법에 비해 개선 효과는 뛰어나지만 큰 용적과 용량을 필요로 하고 회로가 복잡하며 선형화기에서 어느 정도의 신호 전력의 손실이 발생 하는 단점이 있다.

피드포워드 선형화 방식의 구조는 크게 주신호 제거부와 왜곡 신호 제거부로 나눌 수 있는데 그림 3.3 은 이 방식의 간략한 기본 회로도 를 나타내고 있고, 동작 원리는 다음과 같다. 입력으로 인가된 두 개의 반송파는 전력 분배기에 의해 주 경로와 보조 경로로 분배되고 두 경 로로 분배된 신호들은 그림 3.4(a)와 같이 신호의 크기와 위상이 동일 하게 나누어 진다. 주 경로로 분배된 반송파는 전력증폭기에 의해 그 림 3.4(b)와 같이 원하는 크기의 출력 레벨까지 증폭되면서 불필요한 혼변조 왜곡 신호들도 동시에 발생시킨다. 증폭된 신호에 일부를 추출 해서 주신호 빼기 회로에 인가하고 동시에 보조 경로를 통해서 전달된 순수한 반송파를 주신호 빼기 회로에 함께 인가한다. 주신호 빼기회로 출력은 주신호가 제거된 혼변조 왜곡 신호만을 출력하게 된다. 이렇게 얻어진 신호는 가변 감쇠기와 가변 위상기 그리고 오차 증폭기를 거쳐 서 주 경로 신호와 합해져서 최종 출력에서는 주 신호에 비해 혼변조 왜곡 신호들이 최소가 되도록 하는 선형화 방식이다. 혼변조 왜곡 신 호 제거부에서 사용된 가변 감쇠기와 가변 위상기는 주 경로를 통해서 전달되는 혼변조 왜곡 신호와 크기는 같고 위상은 역 위상이 되도록 미세 조정을 하기 위한 것이다. 피드포워드 선형화 방식의 최종 출력 특성은 이상적으로는 그림 3.4(e)와 같이 혼변조 신호 성분들은 완전 히 제거된 순수한 반송파만이 나타난다[14][15].

Figure 3.3 Basic block diagram of Feedforward method.

그림 3.4 피드포워드 방식의 동작 원리.

Figure 3.4 Operation principle of Feedforward method.

#### 제 4 절 전치왜곡(Predistortion) 방식

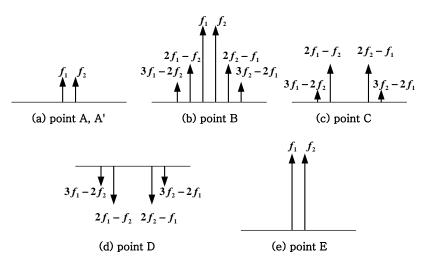

전치왜곡 방식의 선형화기는 입력 RF 신호가 주 증폭기에서 만들 왜곡 성분을 고려하여 이것과 역의 왜곡 특성을 갖는 회로를 미리 대전력 증폭기의 앞 단에 부가하여 대전력 증폭기의 왜곡 성분을 상쇄시키는 방식이다. 광대역폭과 넓은 동작 범위를 갖는 특성이 있으며, 회로 구성이 간단하여 경량, 소형으로 구현할 수 있으나 개선 효과는 피드포워드 방식보다 좋지 않다. 그림 3.5는 전치왜곡 선형화 방식의 동작 원리이다.

Figure 3.5 Operation principle of LPA using predistortion method.

### 제 4 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기

본 장에서는 제안하고자 하는 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 동작 원리에 대한 설명에 앞서 전체 회로 구성 및 간략한 동작 원리에 대해 언급을 있고, 다음으로 각 루프 별 동작 원리에 대해 구체적인 분석이 이루어 질 것이다. 또한 전체 시스템의 구성회로에 대한 설계 이론 및 측정결과는 제 5 장에서 설명할 것이다.

#### 제 1 절 전체 회로 구성 및 동작 원리

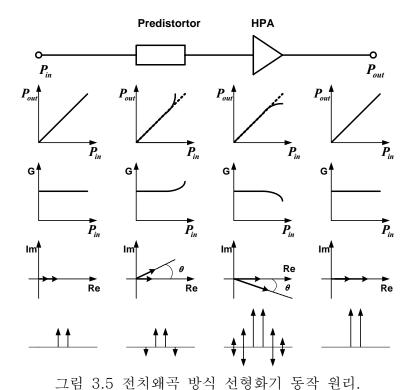

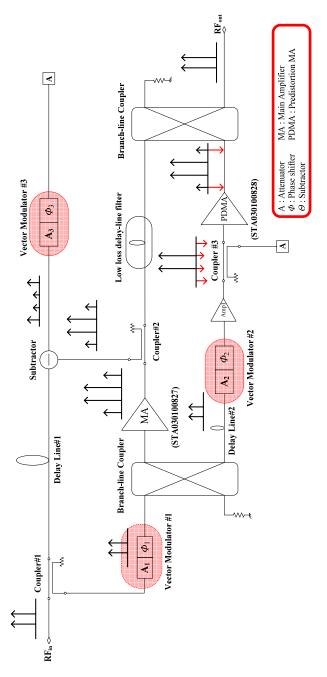

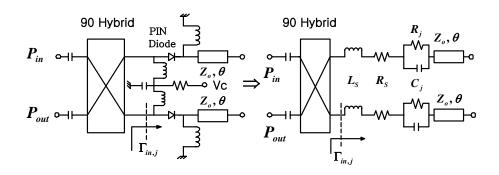

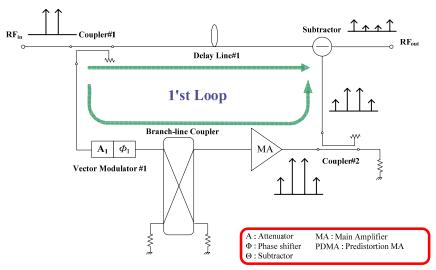

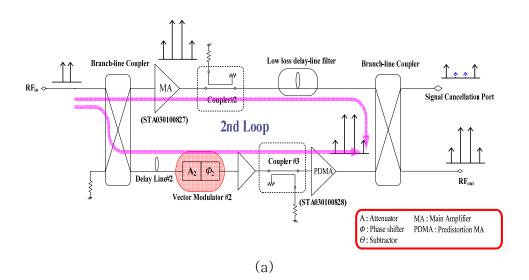

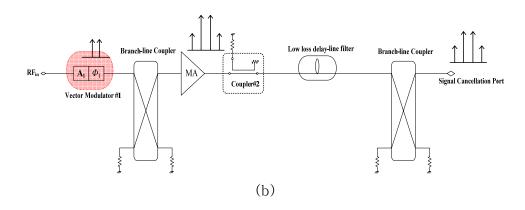

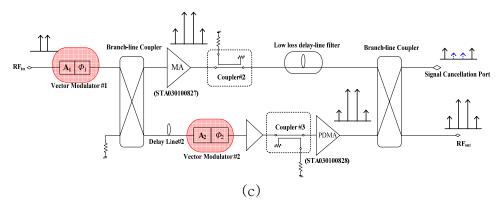

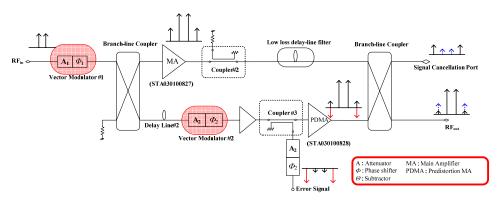

그림 4.1은 본 논문에서 제안하는 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기(Partial Predistortion Balanced Power Amplifier: PPBA)의 블록도를 보여주고 있다. 먼저 주 신호 제거 루프에서는 입력 신호를 평형 전력증폭기의 입력과 지연 선로(Delay Line#1)로 분기하는 10dB 방향성 결합기(1), 저 위상 가변 감쇠기와위상 천이기로 구성된 벡터 변조기(Vector Modulator#1)(3), 주 전력 증폭기(Main Power Amplifier: MA)(4), 20dB 방향성 결합기(5), 빼기 회로(2)로 이루어져 있다. 평형 증폭기 루프는 3dB 브랜치 라인결합기, 주 전력증폭기(MA)(4), 방향성 결합기(5), 저손실 군속도 지연 여파기(6)와 지연 선로(Delay Line#2), 신호의 진폭과 위상을 제어하기 위한 벡터 변조기(Vector Modulator#2)(7), 부족한 이득 특성을 보충하기 위한 선형 구동 전력증폭기(8), 방향성 결합기(9), 전치 왜곡 전력증폭기(Pre-Distortion Main Power Amplifier:

PDMA)(10), 그리고 3dB 브랜치 라인 결합기로 구성된다. 그리고 오차 신호 주입 루프는 3dB 브랜치 라인 결합기, 주 전력증폭기 (MA)(4), 방향성 결합기(5), 빼기 회로(2), 벡터 변조기(Vector Modulator#3)(11)와 지연 선로(Delay Line#2), 벡터 변조기 (Vector Modulator#2)(7), 구동 전력증폭기(8) 그리고 10dB 방향성 결합기#3(9)로 구성되어 있다.

그림 4.1에서와 같이 구성된 전체 회로는 3개의 루프로 구성되어 있다. 먼저 지연 선로 경로와 주 신호 증폭 경로로 구성된 주 신호 제거 루프, 본 논문에서 제안하는 선형화 대상 전력증폭기인 평형 전력 증폭기 루프 그리고 오차 신호 경로와 전치왜곡 전력증폭 경로로 이루어진 오차 신호 주입 루프로 구성되어 있다. 첫째, 주 신호 제거 루프는 주 신호는 제거되고 혼변조 신호만을 발생시키는 동작을 하고 있다. 둘째, 평형 전력증폭기 루프는 본 논문에서 제안하는 선형화 동작을 확인하는 대상 시료 전력 증폭기로써 효과적인 선형화 동작을 유도하기 위해 선형성 정도에 차이를 두고 있는 두 개의 전력 증폭기로 구성되어 있다. 셋째, 오차 신호 주입 루프는 주 신호 제거 루프에서 만들어진 혼변조 신호를 PDMA 경로의 같은 크기의 진폭, 역 위상의 조건을 만들어 PDMA 경로의 신호와 결합하여 원하는 전치왜곡 신호를 발생 시킨다. 다음절에서는 루프별 세부적인 분석이 이루어 질 것이다.

그림 4.1 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 전체 블록도. Figure 4.1 Block diagram of partial predistortion balanced power amplifier.

#### 제 2 절 루프 별 동작 원리

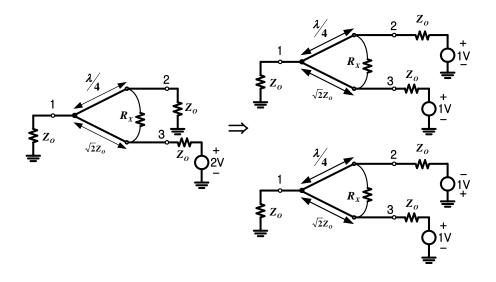

그림 4.2에서는 2-tone 신호를 인가하여 PPBA의 동작 특성을 설명하기 위한 블록도이다. 제안된 PPBA에서 오차 신호 추출에 사용되는 평형 전력증폭기의 MA는 세원텔레텍사의 STA030100827 모델을 사용되었고, 비교적 선형적인 동작 특성을 지닌 평형 전력증폭기의 PDMA는 세원텔레텍사의 STA030100828 모델이 사용되었다.

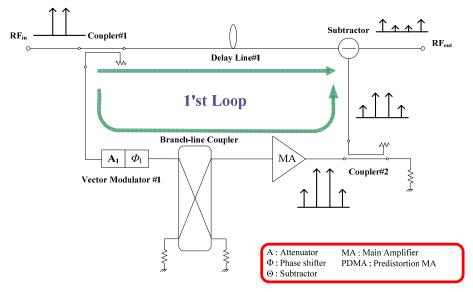

본 연구에서는 MA에서 오차 신호를 추출하여 평형 전력증폭기의 왜곡 신호 성분을 제거하는 방법을 취하고 있다. 그림 4.2의 블록도에서 동작 특성상 3가지 루프로 분류하여 동작 원리를 분석할 수 있다. 먼저 오차 신호를 추출하기 위한 주 신호 제거 루프(first loop), 선형화 대상 증폭기인 평형 전력증폭기 루프(second loop) 그리고 마지막으로 평형 전력증폭기의 왜곡 신호의 상쇄를 위한 오차 신호 주입 루프(third loop)로 나누어 동작 원리를 분석하고자 한다.

그림 4.2에서 알 수 있듯이 평형 전력증폭기에서 발생된 위상 및 진폭의 왜곡을 효과적으로 제거하기 위해 평형 전력증폭기의 일부분에서 발생되는 왜곡 신호를 이용하고 있다. 또한, 평형 전력증폭기의 일부에서 오차 신호를 추출하여 평형 전력증폭기의 비선형 특성을 개선하기에 오차 증폭기의 요구되지 않는 등 여러 가지 면에서 장점을 지니고 있다.

그림 4.2 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 동작 원리. Figure 4.2 Operation principle of partial predistortion balanced power amplifier.

#### (1) 주 신호 제거 루프의 동작 원리 (First loop)

그림 4.3은 주 신호 제거 루프의 동작 원리를 설명하기 위한 블록도를 보여주고 있다. 그림 4.3의 입력으로 2-tone 신호가 인가되면 10dB 방향성 결합기(Coupler#1)를 통해 주 증폭 경로와 지연 선로 경로의 두 경로로 분기된다. 이 두 경로 중 주 증폭 경로의 신호는 벡터 변조 기(Vector Modulator#1)과 3dB 브랜치 라인 결합기를 통과하여 MA 의 입력으로 인가되고, MA의 비선형 전달 특성으로 MA의 출력에서는 혼변조 왜곡 성분이 발생하게 된다. 또한 20dB 방향성 결합기 (Coupler#2)를 통과한 혼변조 왜곡 신호와 지연 선로 경로를 통과한 두 신호는 빼기 회로에 인가된다. 이때 출력된 신호들은 동일 전력, 역 위상, 동일 군속도 지연의 동시 정합 조건들을 만족하게 된다. 출력된 신호들을 동위상 결합기에 인가하면 출력 단에서는 입력 신호가 완전 히 상쇄된다. 여기서 주 증폭 경로를 통해 인가된 주 신호 성분과 지 연 선로 경로를 통해 인가된 주 신호 성분의 결합 시 주 신호의 제거 동작이 이루어지며, MA에서 출력된 왜곡 신호 성분은 동위상 결합기 의 출력 단에 나타나게 되어 오차 신호를 발생시킨다. 주 증폭 경로의 군속도를 측정하여 지연 선로에 반영하고 저 위상 가변 감쇄기와 위상 천이기를 통해 주 증폭 경로 신호의 크기와 위상의 조절이 가능해진다. 주 신호 제거 루프에서 탁월한 성능을 위해서는 빼기 회로의 두 입력 단자에 인가되는 신호의 이득 평탄도가 우수해야 한다. 본 논문에서는 두 경로의 이득 평탄도가 IMT-2000 대역인 2.11~2.17GHz에서 0.1dB 이내의 특성을 얻을 수 있었다.

그림 4.3 주 신호 제거 루프의 동작 워리.

Figure 4.3 Operation principle of the carrier cancellation loop.

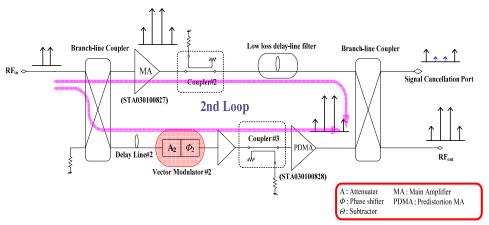

#### (2) 평형 전력증폭기 루프의 동작 원리 (Second loop)

그림 4.4는 본 논문에서 시료로 사용된 평형 전력증폭기 루프의 동작 원리를 설명하기 위한 블록도를 보여주고 있다. 입력 단자에 인가된 입력 신호는 평형 전력증폭기의 3dB 브랜치 라인 결합기의 입력에 인가되어 MA 경로와 PDMA 경로로 분기된다. 평형 전력증폭기는 두개의 증폭 소자들로 구성되어 있다. 평형 전력증폭기의 두 증폭기인 MA와 PDMA는 비선형 전달 특성의 정도의 차이를 가지고 있는데, 개념적으로는 동일한 증폭기를 사용해도 무관하지만 좀 더 효과적인 선형화 동작 특성을 얻기 위해 상이한 전력증폭기를 적용하였다. 이는 평형 전력증폭기의 MA에서 추출된 혼변조 신호를 이용하여 PDMA의

입력에 주입하여 평형 전력증폭기의 비선형 왜곡 신호를 효과적으로 제거하기 때문이다. 평형 전력증폭기의 MA 경로와 PDMA 경로의 크기, 위상 그리고 군속도가 일치되면 그림 4.4의 평형 전력증폭기의 신호 상쇄 출력 단자(signal cancellation output port)에서는 두 개의 3dB 브랜치 라인 결합기의 위상이 180°의 차이를 이루고 있기 때문에 MA의 혼변조 신호의 출력과 비교적 선형적인 PDMA의 선형 출력이 결합하여 주 신호가 제거되어 혼변조 왜곡 신호가 평형 전력증폭기의 출력 단자에 나타난다. 이렇게 신호 상쇄 출력 단자에서의 신호를 모니터링 하게 되면 평형 전력증폭기의 결합 상태를 점검할 수 있다.

본 논문에서 제안하는 PPBA는 MA에서 추출된 혼변조 신호를 PDMA의 입력에 주입하는 방법을 이용하여 평형 전력증폭기의 왜곡신호 성분을 효과적으로 제거할 수 있다.

그림 4.4 평형 전력증폭기 루프의 동작 원리.

Figure 4.4 Operation principle of balanced power amplifier loop.

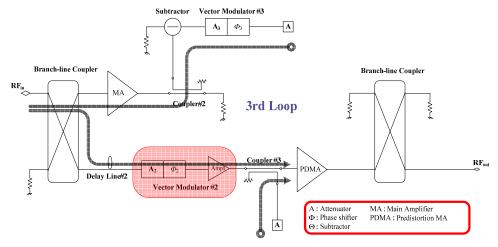

#### (3) 오차 신호 주입 루프의 동작 원리 (Third loop)

그림 4.5는 오차 신호의 주입 루프의 동작 원리를 설명하기 위한 블록도이다. 평형 전력증폭기의 입력된 신호는 입력 3dB 브랜치 라인결합기에 의해 MA 경로와 PDMA 경로로 각각 분기된다. MA에 인가된 신호의 출력은 증폭된 입력 신호 성분과 혼변조 왜곡 신호 성분이동시에 발생되게 된다. 앞서 언급한 주 신호 제거 루프에서 만들어진오차 신호 성분은 가변 감쇠기와 위상 천이기로 구성된 벡터 변조기를통해 신호의 크기와 위상이 조절이 된다. 이렇게 크기와 위상이 조절된 오차 신호는 10dB 방향성 결합기에 의해 PDMA의 입력으로 주입되게 된다.

그림 4.5 오차 신호 주입 루프 동작 원리.

Figure 4.5 Operation principle of error signal injection loop.

여기서 중요하게 고려해야 할 사항은 전체 오차 신호 주입 루프를

오차 신호 경로와 PDMA 경로로 구분할 수 있는데, 이렇게 분류된 두경로 간의 동일한 크기, 역 위상, 동일 군속도 지연의 동시 정합 조건이 만족되어야 하며, 이때 PDMA 경로의 주 신호와 오차 신호 경로의오차 신호가 역 위상의 관계를 가지며 10dB 방향성 결합기에 의해 결합하게 된다. 이렇게 결합한 신호는 PDMA의 입력으로 인가되어 평형증폭기의 왜곡 신호 성분을 제거하게 된다. 오차 신호 주입 루프에서무엇보다도 중요한 점은 만들어진 오차 신호의 주입 경로에 있는 감쇠기와 위상 천이기의 이득 평탄도 특성이 상당히 우수해야 한다는 것이다. 그리고 이 경로의 군속도 지연 효과는 혼변조 신호 성분의 측면에서 두 경로가 일치해야 하므로 약간의 조정이 필요하다.

본 논문에서는 평형 증폭기의 MA에서 추출된 혼변조 왜곡 신호를 이용하여 PDMA의 입력에 주입하는 방식을 취하고 있기 때문에 오차 신호 증폭기가 요구되지 않아 효율적인 면에서 유리하다.

# 제 5 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 구성 회로 설계

#### 제 1 절 90° 하이브리드(Hybrid) 회로

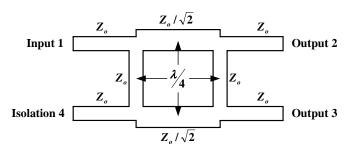

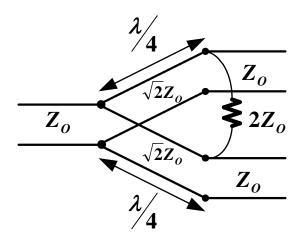

90° 하이브리드 회로는 출력에서 90° 위상 차를 가진 3dB 직교 결합기이다. 하이브리드의 형태는 그림 5.1과 같이 마이크로스트립 또는 스트립 선로 형태를 가지며, 브랜치 라인 하이브리드로 알려져 있다. 우 모드, 기 모드 분해기법을 사용하여 90° 하이브리드의 동작을 해석할 수 있다. 그림 5.1은 90° 하이브리드의 구조를 나타내었고 동작원리는 다음과 같다. 모든 단자는 정합되고, 전력 입력 단자 1(input port)에서 출력 단자 2와 3 사이로 전달되는 신호 사이에 90° 위상변위를 갖고 균등하게 전달된다. 전력은 단자 4(isolation port)에 결합되지 않는다. 그러므로 [S]행렬은 다음의 형태를 갖는다<sup>[16]</sup>.

$$[S] = \frac{-1}{\sqrt{2}} \begin{bmatrix} 0 & j & 1 & 0 \\ j & 0 & 0 & 1 \\ 1 & 0 & 0 & j \\ 0 & 1 & j & 0 \end{bmatrix}$$

(5.1)

어떤 단자가 입력 단자로 사용되더라도, 하이브리드 결합기는 상당한 대칭성을 갖는다. 각 열의 처음 값이 첫 열의 대칭 배치로부터 얻어질 수 있을 때 이런 대칭은 산란 행렬에 반영된다.

하이브리드 결합기의 정합 조건을 만족하는 결합도는 다음 식과 같이 병렬 및 직렬 임피던스 값에 의해 결정된다.

$$\frac{P_2}{P_3} = \left(\frac{Z_o}{Z_p}\right)^2 \qquad \frac{Z_o}{Z_r} = \left[\left(\frac{Z_o}{Z_p}\right) + 1\right]^{\frac{1}{2}}$$

(5.2)

그림 5.1 90° 하이브리드 회로. Figure 5.1 90° hybrid circuit.

본 논문에서는 90° 하이브리드 회로로서 Anaren 사의 3dB, 90° Surface Mount 종류인 S03B2150N3의 모델을 사용하였다. 도한 표 5.1은 각각 이들의 특성을 나타낸다.

표 5.1 3dB 하이브리드 결합기(S03B2150N3)의 사양.

Table 5.1 The specifications of 3dB hybrid coupler (S03B2150N3).

| Specification     | Bandwidth | Units         |

|-------------------|-----------|---------------|

| Frequency         | 2.0 ~ 2.3 | GHz           |

| Isolation         | 20        | DB min.       |

| Insertion Loss    | 0.15      | DB max.       |

| VSWR              | 1.25      | Max:1         |

| Amplitude Balance | ± 0.20    | DB max.       |

| Phase Balance     | 4         | Degrees max.  |

| Power Handling    | 300       | Avg. CW Watts |

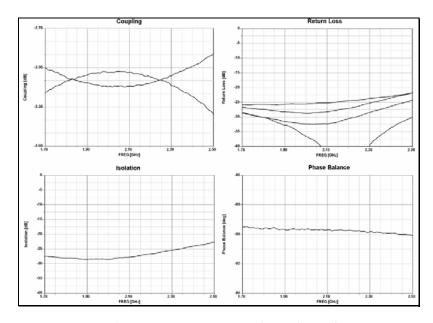

그림 5.2는 Anaren사 S03B2150N3의 주파수 대역에 따른 결합도 와 반사계수, 격리도, 위상 평형도를 나타내고 있다.

그림 5.2 S03B2150N3의 동작 특성.

Figure 5.2 Operation characteristics of S03B2150N3.

# 제 2 절 가변 위상 변환기

가변 위상 변환기는 전압에 따라 위상을 변화시킬 수 있는 회로이다. 여기서 사용되는 소자는 바렉터(varactor) 다이오드이며 기본적으로 가변 리액턴스 소자로서 기능하는 아날로그 동작 특성을 갖는다. 이런 가변 리액턴스 소자는 역방향 바이어스 전압에서 다이오드의 전압 조정 캐패시턴스를 통해 이루어 진다. 바렉터 다이오드 위상변환기는 반사형 구조의 회로를 주로 이용하며, 이 때 하이브리드 결합형이 가장

많이 쓰인다.

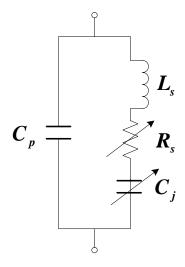

#### (1) 바렉터 다이오드의 특성<sup>[17][18]</sup>

바렉터 다이오드 소자는 전형적인 도핑 모양을 한  $p^+-n-n^+$ 샌드위치 구조로 이루어져 있다. 바렉터의 접합층 캐패시턴스 $C_f(V)$ 는 공핍층의 폭W의 함수이다. 이때 W는 인가된 역방향 바이어스 전압의 함수에따라 결정된다. 이 캐패시턴스는

$$C_j = \frac{\varepsilon A}{W(V)} \tag{5.3}$$

로서 표현되며, 이 때 A는 횡단면의 면적이고,  $\varepsilon$ 와 W(V) 는 각각 유전체 상수와 공핍층의 전압 의존형 폭이다. 역방향 전압이 O[V]부터 증가함 에 따라 공핍층 폭 W가 증가하게 되며 캐패시턴스는 감소하게 된다. n영역의 나머지 부분은 직렬저항  $R_s$ 로 볼 수 있으며, 이 저항 값은 역 방향 전압의 증가에 따라 감소하게 된다. 바렉터에서 도핑 밀도는 가능 한 저항 값을 줄이기 위해 접촉부의 끝에 상당히 높도록 만들어져 있다.

그림 5.3은 패키지 바렉터 다이오드 등가회로를 나타낸다. 이것은 리드 인덕턴스, 패키지 캐패시턴스를 포함하고 있다. 바렉터의 중요한 기능은 가변 캐패시턴스로서 동작하는 것이기 때문에 바이어스에 따른 캐패시턴스의 변화 범위는 원하는 위상 변화를 시킬 만큼 충분히 커야된다. 리액턴스  $1/\omega C_j$ 는 높은 주파수에서  $R_s$ 에 비교해 커야 된다.  $R_s$ 를 작게 유지시키기 위해서는 역방향 바이어스 영역에서 바렉터 다이오드가 동작하면 된다.

그림 5.3 바렉터 다이오드의 등가회로. Figure 5.3 Equivalent model of a varactor diode.

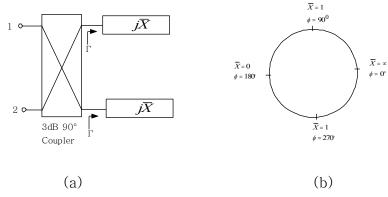

#### (2) 반사형 위상 변환 회로

반사형 아날로그 위상 변환기는 바렉터 다이오드를 종단 시킨 다음 이것을 서큘레이터나 3dB 하이브리드 결합기를 적용하여 바렉터의 반사특성을 이용한 회로이다<sup>[19][20]</sup>. 이 반사형 위상 변환기는 제어전압의 변화에 따라 낮은 삽입손실을 유지하면서 원하는 위상 변환기의 응답을 이룰 수 있도록 적절히 설계되어야 한다.

## 1) 종단 반사를 이용한 가변 리액턴스

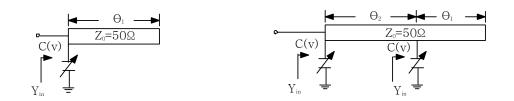

그림 5.4는 리액턴스 성분으로 3dB 하이브리드 결합기를 종단시켰을 경우의 회로도를 나타내고 그 때의 위상 변화를 나타내었다.

- (a) 가변 리액턴스로 종단된 결합기의 구조

- (a) Coupler terminated with variable reactance

- (b) 정격화된 리액턴스 함수로 표현되는 반사신호의 위상

- (b) Phase of reflected signal for normalized reactance function 그림 5.4 가변 위상 변환기에 사용된 결합기.

Figure 5.4 Coupler used in a variable phase shifter.

그림 5.5 가변 위상 변환기의 반사계수 산출.

Figure 5.5 Reflection coefficient calculation in variable phase shifter.

그림 5.5(a)에서 리액턴스 성분의 반사계수를 산출하기 위한 회로도를 타내었다.

$$Y_{in} = Y_{p} \frac{jwC(v) + jY_{p} \tan \theta_{p}}{Y_{p} + j(jwC(v)) \tan \theta_{p}} = j \frac{Y_{p}(wC(v) + Y_{p} \tan \theta_{p})}{Y_{p} - wC(v) \tan \theta_{p}}$$

$$= jwC(v) + j \frac{Y_{p}(wC(v) + Y_{p} \tan \theta_{p})}{Y_{p} - wC(v) \tan \theta_{p}} = jB$$

(5.4)

여기서 반사 계수는 다음과 같다.

식(5.5)으로부터 다음 식 (5.6)를 구할 수 있다.

$$\phi = -2\tan^{-1}(\overline{B}) \tag{5.6}$$

그림5.5(b)에서 본 바와 같이  $0^{\circ}$ 부터  $360^{\circ}$ 까지 위상변화를 시키기위해서는  $\overline{X}$ 는  $+\infty$ 부터 0을 거쳐  $-\infty$ 까지 변화해야만 된다. 리액턴스와 함께 위상변화의 변화율은  $\overline{X}=0$ 일 때 최대가 된다. 그러므로 최대 위상변화를 시키기 위해서는 다이오드의 용량성 리액턴스가 유도성리액턴스와 직렬 공진이 되도록 해야 된다. 이것은 스터브에 의해서공진시킬 수 있다.

#### 2) 실제 적용된 가변 위상 변환기

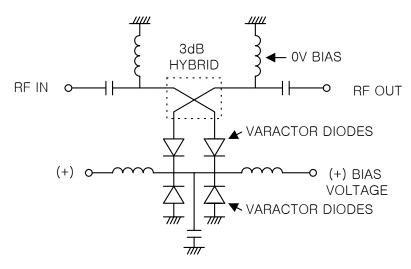

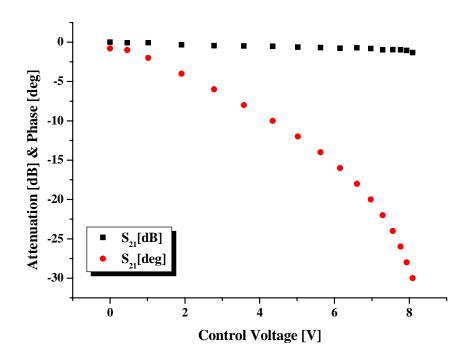

그림 5.6과 그림 5.7 그리고 표 5.2는 본 논문에 실제 사용된 위상 변환기의 회로 및 측정된 특성이다. 사용된 바렉터 다이오드는 Sony 사의 1T362이다.

그림 5.6 90° 하이브리드를 이용한 반사형 가변 위상 변환기의 회로. Figure 5.6 Reflection type variable phase shifter circuit using 90° hybrid.

그림 5.7 가변 위상 변환기 측정 결과. Figure 5.7 Variable phase shifter measurement.

표 5.2 가변 위상 변환기 측정 결과.

Table 5.2 Variable phase shifter measurement.

| Control Voltage[V] | $S_{21}[\deg]$ | $S_{21}[dB]$ |

|--------------------|----------------|--------------|

| 0                  | 0              | -0.7         |

| 0.5                | 5.7            | -0.7         |

| 1.0                | 10.6           | -0.7         |

| 1.5                | 15.6           | -0.8         |

| 2.0                | 20.7           | -0.8         |

| 2.5                | 25.9           | -0.9         |

| 3.0                | 32.4           | -0.9         |

| 3.5                | 36.9           | -1.0         |

| 4.0                | 43.4           | -1.0         |

| 4.5                | 49.8           | -1.1         |

| 5.0                | 56.9           | -1.1         |

| 5.5                | 63.5           | -1.2         |

| 6.0                | 72.3           | -1.3         |

| 6.5                | 81.1           | -1.3         |

| 7.0                | 90             | -1.4         |

| 7.5                | 99.1           | -1.4         |

| 8.0                | 109.9          | -1.4         |

| 8.5                | 121.1          | -1.4         |

| 9.0                | 133.2          | -1.4         |

| 10.0               | 155.4          | -1.3         |

| 11.0               | 175.7          | -1.2         |

| 12.0               | 194.1          | -1.0         |

| 13.0               | 207.3          | -0.9         |

| 14.0               | 218.6          | -0.8         |

| 15.0               | 227.6          | -0.8         |

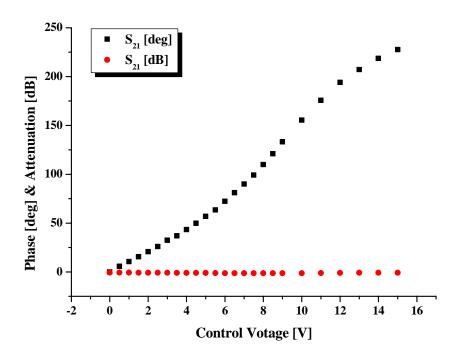

#### 제 3 절 저 위상 가변 감쇠기

감쇠기는 전기적으로 제어가 가능한 저항 성분을 갖고 있는 PIN 다이오드나 GaAs MESFET 등이 그 소자로 사용되는데 사용의 용이성을 갖는 PIN 다이오드를 사용하는 것이 일반적이다. MESFET으로 감쇠기를 제작할 경우 FET로 T형 또는 Pi형 저항성 Pad를 구현하고 각 FET의 게이트 전압을 조정함으로써 신호 감쇠 특성을 얻을 수 있다. MESFET 감쇠기는 PIN 다이오드를 이용한 감쇠기보다 더 큰 전력을 인가할 수 있다는 장점이 있으나 감쇠를 얻기 위한 제어 단자의수가 더 많아지는 단점이 있다. 감쇠기를 선형화기에 적용할 경우 감쇠기 입출력 단자간에 충분히 큰 선형성이 보장하기 위해 감쇠기에 인가되는 전력을 충분히 작게 하므로 PIN 감쇠기의 동작 전력 능력은 문제가 되지 않는다.

그림 5.8 반사형 감쇠기의 등가회로.

Figuer 5.8 The equivalent circuit of reflection type attenuator.

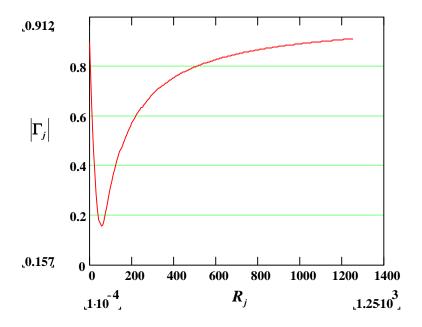

그림 5.8은 반사형 구조를 이용한 PIN 다이오드 감쇠기 회로 및 등 가회로를 나타낸 것으로 바이어스 전류에 의해 접합 저항(junction resistance:  $R_j$ ) 값이 변화함으로써 감쇠기가 동작하게 된다. 그러나 PIN 다이오드의 경우  $R_j$  이외에 다른 기생 소자 성분 때문에 신호 레벨 감쇠 동작 시에 위상 변화도 동반하는 것이 일반적이다<sup>[21][22]</sup>.

그림 5.9 PIN 다이오드의 접합저항 변화에 따른 반사계수 크기 특성. Figure 5.9 Magnitude variation of reflection coefficient for junction resistance in PIN diode.

그림 5.10 PIN 다이오드의 접합저항 변화에 따른 반사계수 위상 특성.

Figure 5.10 Phase variation of reflection coefficient for the variable resistance in PIN diode.

그림 5.9와 그림 5.10은 Mathcad를 이용하여 중심 주파수 2.14 GHz 에서  $Z_o$ =50  $\Omega$ ,  $L_s$ =1.748 nH,  $C_j$ =0.2034 pF,  $R_s$ =3.342  $\Omega$  일 때, PIN 다이오드의 접합 저항 변화에 따른 반사 계수의 진폭 및 위상 변화의 시뮬레이션 결과이다.  $R_j$ =50  $\Omega$ 에서 최대의 감쇠가 일어나며,  $R_j$ 가 0  $\Omega$  근처이거나 또는 50  $\Omega$ 보다 훨씬 큰 값을 가질 때 반사량이 많아져 감쇠량이 감소하는 것을 알 수 있다. 또한 시뮬레이션 결과는  $R_j$ 가 50  $\Omega$  일 때와 10  $\Omega$ 일 때의 위상차를  $\Delta\Phi_{50-10\Omega}$  라고 할 때

$\Delta\Phi_{50-10\Omega}$ =95.5°이며,  $\Delta\Phi_{50-200\Omega}$ =66.58°임을 보여주고 있다.

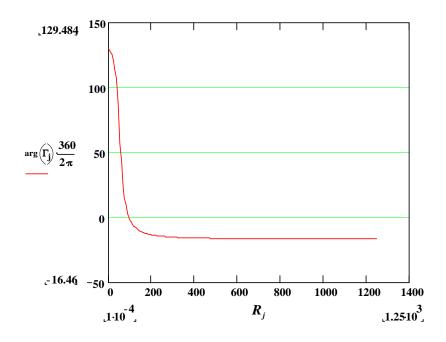

반사형 감쇠기의 감쇠에 따른 위상의 변화를 보상해주기 위한 회로는 그림5.11에 나타내었는데, 부가적으로 위상 보상회로인 개방형 스터브(open stub)를 추가하였다.

그림 5.11 반사형 저 위상 가변 감쇠기.

Figure 5.11 Reflection type low phase shift attenuator.

$$\Gamma_{in,j} = \left| \Gamma_{in,j} \right| e^{j\theta} = \frac{Z_{in,j} - Z_o}{Z_{in,j} + Z_o} \bigg|_{j=l \text{ arge or small}}$$

$$= \frac{R_S - Z_o + \frac{R_j}{1 + (\omega R_j C_j)^2} + j \left( \omega L_S - Z_o \cot \theta - \frac{\omega R_j^2 C_j}{1 + (\omega R_j C_j)^2} \right)}{R_S - Z_o + \frac{R_j}{1 + (\omega R_j C_j)^2} + j \left( \omega L_S - Z_o \cot \theta - \frac{\omega R_j^2 C_j}{1 + (\omega R_j C_j)^2} \right)} \bigg|_{R_j = l \text{ arge or small}}$$

(5.7)

$$\Phi_{j} = \tan^{-1} \left[ \frac{\omega L_{s} Z_{o} \cot \theta_{i} - \frac{\omega R_{j}^{2} C_{j}}{1 + (\omega R_{j} C_{j})^{2}}}{R_{s} - Z_{o} + \frac{R_{j}}{1 + (\omega R_{j} C_{j})^{2}}} \right]$$

$$- \tan^{-1} \left[ \frac{\omega L_{s} - Z_{o} \cot \theta_{i} - \frac{\omega R_{j}^{2} C_{j}}{1 + (\omega R_{j} C_{j})^{2}}}{R_{s} + Z_{o} + \frac{R_{j}}{1 + (\omega R_{j} C_{j})^{2}}} \right]_{R = large or small}$$

(5.8)

가변 감쇠기의 경우  $R_j=50\Omega$  근처에서는 반사량이 최소이고 감쇠량은 최대인 반면에,  $R_j=0$   $\Omega$  근처 또는  $R_j$ 이 매우 큰 저항 값을 가질 때반사량이 최대이고 감쇠량은 최소가 된다. 저 위상 가변 감쇠기의 경우  $R_j=50$   $\Omega$ 일 때 반사 신호의 위상과  $R_j=0$   $\Omega$  또는  $\max$   $\Omega$  일 때 반사 신호의 위상이 같게 된다면 신호 감쇠의 특성을 얻으면서 위상 변화 특성을 최소화 할 수 있게 된다.  $R_j=50$   $\Omega$  일 때의 감쇠기에 의한반사 신호의 위상을  $\Phi_{R_j=50}$ 이라 하고,  $\Phi_{R_j=10}$ 이라 하면,

$$F(\theta) = \Phi_{Ri=50} - \Phi_{Ri=Max} \approx 0 \tag{5.10}$$

을 만족하는 전기각  $\theta$ 를 구함으로써 저 위상 가변 감쇠기를 구현할 수 있게 된다. 저 위상 가변 감쇠기에 사용된 PIN 다이오드는 AVAGO사의 HSMP-4810 모델이다. Deloach 방법을 이용하여 다이

오드의 등가회로를 추출하였는데 추출 파라미터 값은  $L_S$ =1.748 nH,  $C_j$  =0.2034 pF,  $R_S$ =3.342  $\Omega$ 이다. 이 다이오드 파라미터를 이용하여 동작 주파수 2.14 GHz에서 저 위상 변화 감쇠기를 구현하기 위한 개방 선로의 전기각은 Mathcad를 통해서 계산 값  $\theta$ =70.7°을 얻었다. 가변 감쇠기의 감쇠량에 따른 위상 변화량은 감쇠량 30 dB에 대하여약 1° 미만의 특성을 얻었으며 이때 구현된 전기각은 약 69°이다. 표5.3에 제작된 저 위상 변화 감쇠기의 특성을 나타내었다.

그림 5.12 저 위상 가변 감쇠기의 측정 결과. Figure 5.12 Measurement results of low phase shift attenuator.

표 5.3 제작된 저 위상 가변 감쇠기의 측정 결과.

Table 5.3 Measurement results of manufactured low phase shift attenuator.

| Control Voltage[V] | $S_{21}[	ext{deg}]$ | $S_{21}[\mathrm{dB}]$ |

|--------------------|---------------------|-----------------------|

| 0                  | 0                   | -0.8                  |

| 0.46               | -0.085              | -1                    |

| 1.02               | -0.081              | -2                    |

| 1.91               | -0.336              | -4                    |

| 2.78               | -0.442              | -6                    |

| 3.58               | -0.487              | -8                    |

| 4.35               | -0.523              | -10                   |

| 5.02               | -0.628              | -12                   |

| 5.63               | -0.690              | -14                   |

| 6.15               | -0.769              | -16                   |

| 6.60               | -0.705              | -18                   |

| 6.97               | -0.814              | -20                   |

| 7.29               | -0.970              | -22                   |

| 7.56               | -0.951              | -24                   |

| 7.77               | -0.987              | -26                   |

| 7.93               | -1.060              | -28                   |

| 8.09               | -1.321              | -30                   |

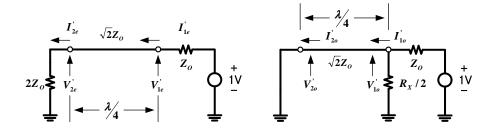

#### 제 4 절 동위상 전력 분배기/결합기

Wilkinson 전력 분배기는 입력 전력을 출력 두 단자에 동위상으로 양분하는 3단자 소자이고 출력 단자 간에 격리도(isolation)를 가지며모든 단자에서 임피던스 정합이 가능한 분배기이다. Wilkinson 전력분배기는 임의의 전력분배 비율을 갖도록 만들어 질 수 있으며, 본논문에서 3dB 전력분배기를 사용하였다. 그림 5.13은 Wilkinson 전력분배기를 나타내고 있으며 만약 단자 2, 3의 종단 임피던스가 50Ω으로 정합되어 있다면 단자 1(input port)에 인가된 입력 전력은 단자 2, 3에 균등하게 나누어지며 저항 2Z₀에서는 아무 전력도 소모하지 않는데, 이는 단자 2, 3이 등전위이기 때문이다<sup>[23][24]</sup>.

그림 5.13 Wilkinson 전력 분배기. Figure 5.13 Wilkinson power divider.

해석의 간략화를 위해 모든 임피던스를 특성 임피던스  $Z_0$  에 대해서 정합되었다고 한다면 그림 5.14에서와 같이 출력 단자에 전압 소스를 갖는 회로로 대치시킬 수 있으며, 전력 합성기의 우(even), 기(odd) 모드 여기 모델로 표현할 수 있다. 우 모드와 기 모드는 그림 5.13과 같은 2 단자 등가 모델로 변환시켜 생각할 수 있다. 무손실 전송 선로를 사용하였다고 가정할 때 입출력 전달 함수를 ABCD 행렬로 표현하면 식(5.11)와 식(5.12)로 표현할 수 있다.

그림 5.14 Wilkinson 전력 합성기의 우, 기 모드 여기 모델. Figure 5.14 Even and odd mode of Wilkinson power combiner.

그림 5.15 변환된 Wilkinson 전력 합성기의 우, 기 모드 여기 모델. Figure 5.15 Even and odd mode of Converted Wilkinson power combiner.

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{even} = \begin{bmatrix} \cos\frac{\pi}{2} & j\sqrt{2}Z_o\sin\frac{\pi}{2} \\ j\frac{1}{\sqrt{2}Z_o}\sin\frac{\pi}{2} & \cos\frac{\pi}{2} \end{bmatrix} = \begin{bmatrix} 0 & j\sqrt{2}Z_o \\ \frac{j}{\sqrt{2}Z_o} & 0 \end{bmatrix}$$

(5.11)

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ \frac{2}{R_X} & 1 \end{bmatrix} \begin{bmatrix} 0 & j\sqrt{2}Z_o \\ \frac{j}{\sqrt{2}Z_o} & 0 \end{bmatrix} = \begin{bmatrix} 0 & j\sqrt{2}Z_o \\ \frac{j}{\sqrt{2}Z_o} & \frac{j2\sqrt{2}Z_o}{R_X} \end{bmatrix}$$

(5.12)

이때 입출력 전압, 전류의 관계는 다음과 같다.

$$V'_{1e} = j\sqrt{2}Z_{o}I'_{2e} \qquad V'_{1o} = j\sqrt{2}Z_{o}I'_{2o}$$

$$I'_{1e} = \frac{j}{\sqrt{2}Z_{o}}V'_{2e} \qquad I'_{1o} = \frac{j}{\sqrt{2}Z_{o}}V'_{2o} + \frac{j2\sqrt{2}Z_{o}}{R_{X}}I'_{2o}$$

(5.13)

여기에  $V_{2e}^{'}=2Z_{o}I_{2e}^{'},\ V_{1e}^{'}+Z_{o}I_{1e}^{'}=1,\ V_{2o}^{'}=0,\ V_{1o}^{'}+Z_{o}I_{1o}^{'}=1$  인 조건을

적용하면 입출력 전압, 전류의 관계는 다음과 같다.

$$V'_{1e} = \frac{1}{2} \qquad V'_{1o} = \frac{1}{\left(1 + \frac{2Z_o}{R_X}\right)}$$

$$I'_{1e} = \frac{1}{2Z_o} \qquad I'_{1o} = \frac{2}{R_X \left(1 + \frac{2Z_o}{R_X}\right)}$$

$$V'_{2e} = \frac{-j}{\sqrt{2}} \qquad V'_{2o} = 0$$

$$I'_{2e} = \frac{-j}{2\sqrt{2}Z_o} \qquad I'_{2o} = \frac{-j}{\sqrt{2}Z_o \left(1 + \frac{2Z_o}{R_X}\right)}$$

(5.14)

단자 2에 입력 전력이 인가되고 단자 1, 3이 종단 임피던스  $Z_0$ 로 정합 되었다면 다음과 같다.

$$V_{1} = V_{2e}^{'} + V_{2o}^{'} = \frac{-j}{\sqrt{2}}$$

$$V_{2} = V_{1e}^{'} + V_{1o}^{'} = \frac{1}{2} + \frac{1}{\left(1 + \frac{2Z_{o}}{R_{X}}\right)}$$

$$V_{3} = V_{1e}^{'} - V_{1o}^{'} = \frac{1}{2} - \frac{1}{\left(1 + \frac{2Z_{o}}{R_{X}}\right)}$$

(5.15)

단자 3이 격리되기를 원한다면  $V_3=0$  , 즉  $1+\frac{2Z_o}{R_\chi}=2$  , 또는  $R_\chi=2Z_o$ 가 되어야 한다. 이 조건을 식(5.14)와 식(5.15)에 적용하면

$$V_{1} = \frac{-j}{\sqrt{2}} \qquad I_{1} = I'_{2e} + I'_{2o} = \frac{-j}{\sqrt{2}Z_{o}}$$

$$V_{2} = 1 \qquad I_{2} = I'_{1e} + I'_{1o} = \frac{1}{Z_{o}}$$

$$V_{3} = 0 \qquad I_{3} = 0$$

(5.16)

이 된다. 따라서 입력 전력의 1/2은 단자 1에 전달되고 나머지는 저항  $R_X$ 에서 소모하게 된다. 따라서  $R_X$  에서만 전력이 소모되기 위해서는  $R_X=100~\Omega$ 이어야 한다.

전력 합성기를 전력의 합성 용도로 쓸 때에는 우 모드의 결합 개념을 이용한다. 그러나 신호를 제거할 목적으로 사용할 때에는 기 모드의 결합 개념을 이용한다. 본 논문에서는 Wilkinson 전력 분배기를 빼기 회로에서는 신호 제거의 목적으로 사용하였다.

표 5.4 Wilkinson 전력 분배기의 측정 결과.

Table 5.4 Measurement result of Wilkinson power divider.

| Port   | S <sub>21</sub> [dB] | S <sub>11</sub> [11] |

|--------|----------------------|----------------------|

| Port 1 | -3.25                | -16.3                |

| Port 2 | -3.25                | -16.5                |

그림 5.16 Wilkinson 출력 단자 1, 2 특성.

Figure 5.16 Wilkinson characteristics at output port 1, 2.

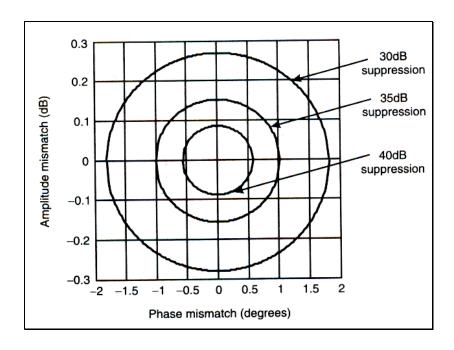

## 제 5 절 신호 상쇄 이론

본 논문에서 사용한 빼기 회로에 인가되는 신호의 크기와 위상을 제어하는 회로의 이론적 배경으로 두 신호의 크기와 위상의 오차에 따른 상쇄 정도에 대해 살펴 보기로 하자. 상쇄 회로에서 주 신호가 제거되는 과정을 수식적으로 살펴보면 다음과 같이 분석할 수 있다.

먼저 다음과 같이 동일한 주파수를 가진 두 경로로부터 입력되는 신호  $V_1$ 과  $V_2$ 가 있다.

$$V_1 = A_1 \cos(\omega_c t), \qquad V_2 = A_2 \cos(\omega_c t + \theta)$$

(5.17)

두 신호의 전력을 dB 단위로 표시하면 각각 다음과 같다.

$$P_1 = 10\log\frac{A_1^2}{2Z_0}, \qquad P_2 = 10\log\frac{A_2^2}{2Z_0}$$

(5.18)

두 신호가 합성되어 얻어지는 신호는

$$V_3 = V_1 + V_2 = A_1 \cos(\omega_c t) + A_2 \cos(\omega_c t + \theta)$$

(5.19)

이며, 이 신호의 전력을 계산하면 다음과 같이 표현할 수 있다.

$$P_3 = 10\log[10^{P_1/10} + 10^{P_2/10} + 2(10^{(P_1+P_2)/20} \times \cos\theta]$$

(5.20)

여기서  $P_1$ 과  $P_2$ 가 같은 전력을 가지고 위상차  $\theta$ 가  $180^\circ$  일 경우에 두 신호는 완전히 상쇄가 된다. 그러나 두 신호 사이에 전력과 위상의 차이가 존재할 경우에 전력과 위상 오차의 정도에 따라서 상쇄되는 한계가 결정된다.

$$P_2 = P_1 + \delta P$$

,  $\theta = \pi + \delta \theta$  (5.21)

$\delta P \, \mathrm{dB}$ 는 전력 오차이며,  $\delta \theta \, \mathrm{deg}$ 는 위상 오차를 나타낸다. 앞 절에서 언급한 Wilkinson 전력 결합기를 사용하기에 회로 내에서  $-3\mathrm{dB}$ 의 감쇠가 발생하며,  $P_1$ 을  $0 \, \mathrm{dBm}$ 으로 할 경우 상쇄되고 남은 전력과의 차이를 신호의 상쇄량으로 나타낼 수 있으므로 식 (5.21)을 식

(5.20)에 대입한 뒤 식 (5.20)을 변형하면 다음과 같은 상쇄 전력을 표현하는 식을 얻을 수 있다.

$$CP(\delta P, \delta \theta) = 10\log[1 + 10^{\delta P/10} - 2 \times 10^{\delta P/20} \times \cos \delta \theta] - 3$$

(5.22)

그림 5.17 경로간 진폭/이득 불일치에 따른 신호 상쇄도. Figure 5.17 Loop suppression and gain/phase matching requirements.

즉, 중심 주파수에서 완전하게 진폭과 역 위상정합이 만족되어도 동작 주파수 대역 끝에서는 주파수 차와 군속도 지연 차로 인해 완 전한 신호 상쇄가 일어나지 않음을 보이고 있다.

# 제 6 장 부분적인 전치왜곡 선형화기를 적용한 평형 전력증폭기의 성능 측정 및 분석

#### 제 1 절 주 전력증폭기 및 전치왜곡 전력증폭기

평형 전력증폭기에 사용된 MA와 PDMA는 모두 세원텔레텍사의 STA 2100-39MM 모델을 이용하였고, PDMA 보다 상대적으로 선형성 정도가 낮게 MA의 바이어스의 조정이 이루어졌다.

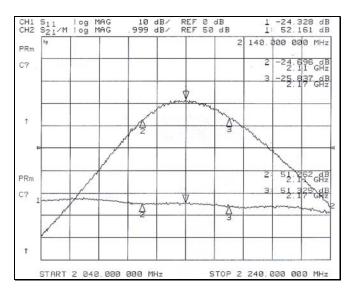

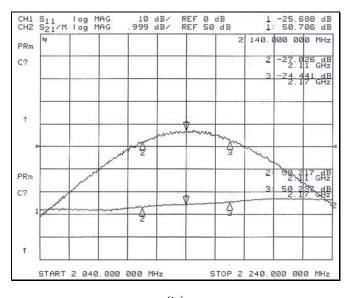

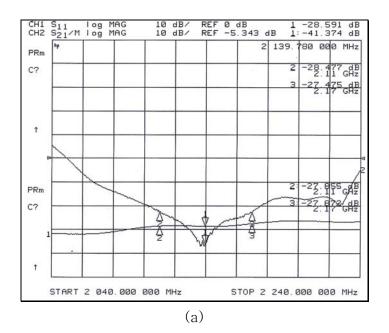

그림 6.1은 MA와 PDMA의 이득 특성을 측정한 결과이며 중심 주파 수에서 각각 52.16dB, 50.70dB 이다. IMT-2000 전체 대역 내에서 PDMA의 이득 평탄도는 0.5dB 이내인 반면 MA의 이득 평탄도는 0. 9dB 이다. 그러나 IMT-2000 대역의 WCDMA 4FA 신호 즉 20 M Hz 대역에 대한 선형성 개선 특성을 확인하므로 이득 평탄도가 다소 차이가 있지만 선형성 개선 특성을 확인하는데 있어 그다지 영향을 끼 치지 않는다. 그림 6.2는 MA와 PDMA의 ACPR 특성을 측정한 결과 로써 오차 신호를 추출하기 위해 사용되는 MA는 IMT-2000 대역의 WCDMA 4FA 신호를 인가 했을 경우의 결과로 중심 주파수인 2.14 GHz에서 12.5 MHz 이격된 지점을 기준으로 할 때 MA와 PDMA의 ACPR 특성은 각각 -27.05 dBc와 -44.68 dBc이다. 그릮 6.2에 두 증폭기 ACPR 특성에서 알 수 있듯이 중심 주파수로부터 상측파 및 하측파 대역의 ACPR 특성이 유사하게 조정을 실시하였다. 이는 MA 에서 추출된 오차 신호가 PDMA의 입력으로 인가되어 평형 증폭기의 왜곡 신호 성분을 제거하기 때문이다. 따라서 그림 6.1과 그림 6.2의 이득 특성과 ACPR특성에서 알 수 있듯이 이론적으로는 동일한 전달 함수를 가진 증폭기를 사용하여도 무관하지만 좀 더 효과적인 선형화

동작 특성을 얻기 위해 비대칭 구조를 적용하였다.

(a)

(b)

그림 6.1 (a)MA와 (b)PDMA의 이득 측정 결과.

Figure 6.1 Measurement results of (a)MA and (b)PDMA for gain.

(a)

(b)

그림 6.2 (a)MA와 (b)PDMA의 ACPR 측정 결과(@P<sub>out</sub>=39dBm). Figure 6.2 Measurement results of (a)MA and (b)PDMA for ACPR.

### 제 2 절 주 신호 제거 루프(First loop)

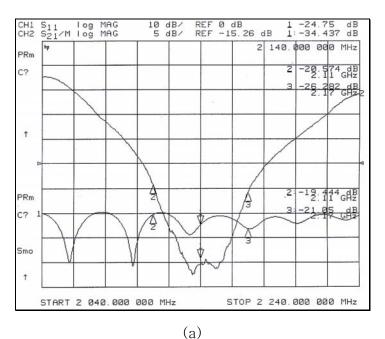

그림 6.3에서 주 신호 제거 루프의 특성을 살펴보기 위하여 입출력 간의 CW 신호 상쇄 특성과 WCDMA 4FA 신호 상쇄 특성을 살펴보 았고, 이를 그림 6.4에 나타내었다.

그림 6.3 주 신호 제거 루프의 블록도.

Figure 6.3 Block diagram of the carrier cancellation loop.

그림 6.4(a)의 IMT-2000 대역의 CW 주 신호 제거 특성에서 알수 있듯이 2.11~2.17GHz의 60MHz 대역에서 약 20dB 이상의 제거특성을 갖는다. 또한 그림 6.4(b)은 WCDMA 4FA 신호를 인가 했을경우, 주 신호 제거 특성을 나타내고 있으며 MA의 출력 신호 레벨이 39dBm 일 때 약 25dB 이상의 주 신호 제거 특성을 확인할 수 있었다.

그림 6.4 주 신호 제거 루프의 측정 결과(@P<sub>out</sub>=40dBm).

Figure 6.4 Measure results of the carrier cancellation loop.

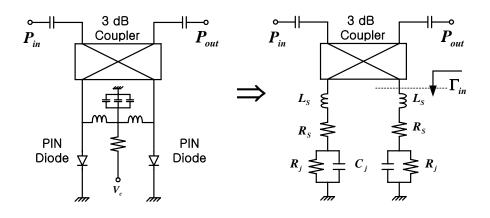

### 제 3 절 평형 전력증폭기 루프(Third loop)

그림 6.5의 평형 전력증폭기 블록도에서 앞서 언급한 바와 같이 MA 경로와 PDMA 경로간의 평형 조건을 충족하였을 경우, 그림 6.6 에서는 출력 3dB 브랜치 라인 결합기의 신호 상쇄 단자에서의 주 신호의 상쇄 정도를 측정한 결과를 나타내고 있다.

그림 6.5 평형 전력증폭기 루프.

Figure 6.5 Balanced power amplifier loop.

두 증폭기의 경로가 동일한 전력의 크기, 동 위상, 동일 군속도 지연효과 특성이 동시에 만족할 경우, 측정 과정을 그림 6.5(b)와 그림 6.5(c)에서 보여주고 있다. 그림 6.6의 평형 전력증폭기의 측정 결과를 통해 알 수 있듯이 대역 내에서 27dB 이상의 주 신호 제거 특성을 보여주고 있다.

그림 6.6 평형 전력증폭기의 측정 결과(@P<sub>out</sub>=40dBm).

Figure 6.6 Measurement results of the balanced power amplifier.

#### 제 4 절 선형화 측정 결과 및 분석

그림 6.7은 선형화 개선 특성을 측정하기 위한 블록도를 보여주고 있다.

그림 6.7 선형화 개선 특성 측정을 위한 블록도 Figure 6.7 Block diagram for measuring the linearization improvements.

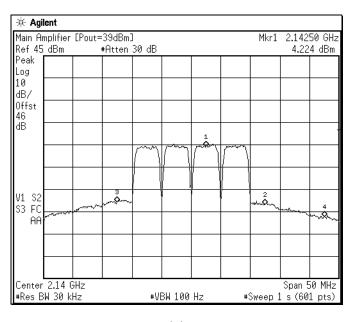

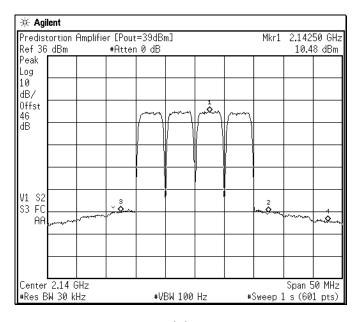

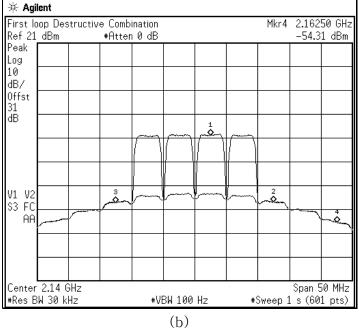

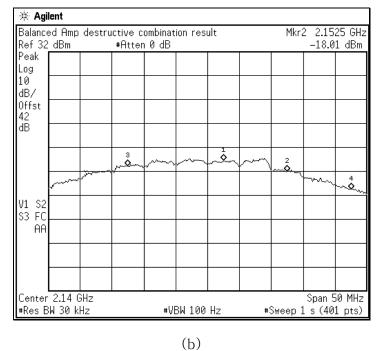

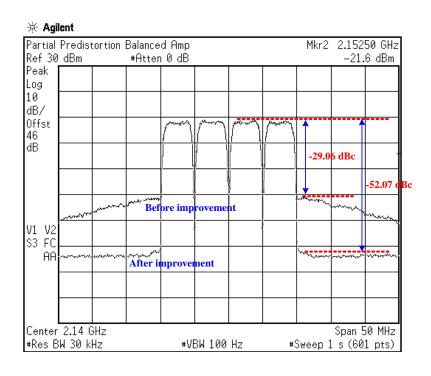

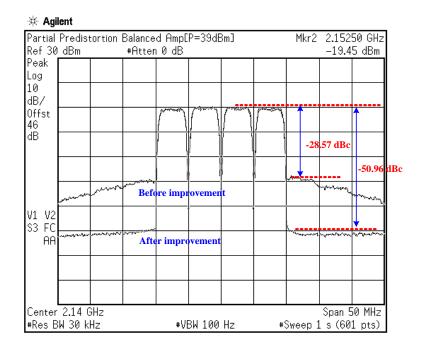

그림 6.8과 6.9는 평균 출력 전력 레벨이 각각 40dBm과 41dBm일 때의 제안된 PPBA의 최종 출력 단의 선형화 개선량을 보여주고 있다. 그림 6.8은 평형 전력증폭기 최종 출력 단의 평균 출력 레벨이 40dBm 일 때 제안된 선형화 기술을 적용 전/후를 비교해 보면, 중심주파수에서 12.5MHz 이격된 지점에서 ACPR 개선량이 -29.06dBc에서 -52.07dBc로 약 23.01dB 정도 개선됨을 보여주고 있다. 그리고 그림 6.9는 평형 전력증폭기의 최종 출력 단의 평균 출력 레벨이 41dBm일 때, 중심 주파수에서 12.5MHz 이격된 지점에서 ACPR 개선량이 -28.57dBc에서 -50.96dBc로 약 22.38dB 정도 개선됨을 보여줌으로써 상당히 우수한 개선 특성을 보여주고 있다. 그러나 스펙트

럼 분석기의 잡음 레벨의 한계성으로 인해 잡음 레벨 이하의 개선되는 특성이 나타나지 않아 더 많은 개선량을 기대할 수 있다.

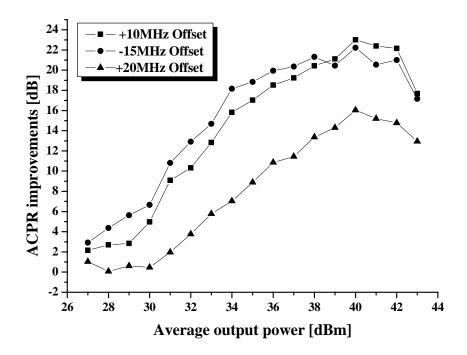

표 6.1에서 표 6.3과 그림 6.10는 동적 출력 전력 레벨에 따른 제안된 선형화기 적용 전/후의 ACPR 개선 특성 및 혼변조 제거 개선량을 보여주고 있다. 이 결과로부터 알 수 있듯이 잡음 레벨의 한계성을 가만하면 15dB 이상의 동적 전력 레벨 범위에서 우수한 선형화 동작특성을 보이고 있다.

그림 6.8 제안된 PPBA의 혼변조 왜곡 특성(@P<sub>out</sub>=40dBm) Figure 6.8 Intermodulation distortion characteristics of the proposed PPBA.

그림 6.9 제안된 PPBA의 혼변조 왜곡 특성(@P<sub>out</sub>=41dBm) Figure 6.9 Intermodulation distortion characteristics of the proposed PPBA.

표 6.1 제안된 PPBA의 동적 전력 레벨에 따른 개선 전 ACPR 특성. Table 6.1 ACPR characteristics of the proposed PPBA before improvement.

# **ACPR** characteristics before improvement

|                           | [dBm]                |         |         |        |  |

|---------------------------|----------------------|---------|---------|--------|--|

| $P_{out}\left[dBm\right]$ | RBW=30kHz, VBW=100Hz |         |         |        |  |

|                           | 2.1425GHz            | + 10MHz | - 15MHz | +20MHz |  |

| 43                        | 11.37                | -14.25  | -14.83  | -22.63 |  |

| 42                        | 9.97                 | -16.13  | -17.17  | -24.68 |  |

| 41                        | 9.13                 | -19.44  | -20.35  | -26.58 |  |

| 40                        | 7.74                 | -21.32  | -21.75  | -27.94 |  |

| 39                        | 7.08                 | -23.12  | -23.52  | -29.79 |  |

| 38                        | 5.98                 | -24.50  | -24.09  | -31.08 |  |

| 37                        | 5.10                 | -26.06  | -25.32  | -33.31 |  |

| 36                        | 4.85                 | -27.44  | -26.12  | -34.82 |  |

| 35                        | 3.22                 | -29.31  | -27.83  | -37.30 |  |

| 34                        | 2.32                 | -30.99  | -29.26  | -39.88 |  |

| 33                        | 0.90                 | -33.50  | -32.00  | -40.87 |  |

| 32                        | 0.84                 | -35.86  | -34.04  | -43.06 |  |

| 31                        | -0.91                | -38.06  | -36.27  | -45.02 |  |

| 30                        | -1.02                | -41.10  | -39.18  | -45.82 |  |

| 29                        | -2.61                | -43.51  | -41.47  | -46.15 |  |

| 28                        | -4.01                | -44.44  | -43.48  | -47.11 |  |

| 27                        | -4.71                | -45.36  | -44.33  | -46.63 |  |

표 6.2 제안된 PPBA의 동적 전력 레벨에 따른 개선 후 ACPR 특성. Table 6.2 ACPR characteristics of the proposed PPBA after improvement.

### ACPR characteristics after improvement

|                | [dBm]                |         |         |        |  |

|----------------|----------------------|---------|---------|--------|--|

| $P_{out}[dBm]$ | RBW=30kHz, VBW=100Hz |         |         |        |  |

|                | 2.1425GHz            | + 10MHz | - 15MHz | +20MHz |  |

| 43             | 11.50                | -31.80  | -31.86  | -35.44 |  |

| 42             | 10.38                | -37.87  | -37.77  | -39.05 |  |

| 41             | 9.54                 | -41.42  | -40.48  | -41.38 |  |

| 40             | 7.90                 | -44.17  | -43.81  | -43.83 |  |

| 39             | 7.34                 | -43.97  | -43.71  | -43.84 |  |

| 38             | 6.03                 | -44.89  | -45.36  | -44.40 |  |

| 37             | 5.40                 | -44.99  | -45.37  | -44.45 |  |

| 36             | 5.25                 | -45.57  | -45.66  | -45.28 |  |

| 35             | 3.67                 | -45.89  | -46.22  | -45.73 |  |

| 34             | 2.74                 | -46.39  | -47.00  | -46.49 |  |

| 33             | 1.16                 | -46.08  | -46.42  | -46.38 |  |

| 32             | 0.73                 | -46.30  | -47.07  | -46.93 |  |

| 31             | -0.52                | -46.76  | -46.69  | -46.59 |  |

| 30             | -1.89                | -46.93  | -46.71  | -47.15 |  |

| 29             | -2.73                | -46.46  | -47.22  | -46.88 |  |

| 28             | -3.59                | -46.72  | -47.42  | -46.76 |  |

| 27             | -4.46                | -47.26  | -47.00  | -47.42 |  |

표 6.3 제안된 PPBA의 동적 전력 레벨에 따른 ACPR 개선량. Table 6.3 ACPR improvements of the proposed PPBA.

# WCDMA 4FA improvements

|                        | [dB]                 |         |        |  |  |

|------------------------|----------------------|---------|--------|--|--|

| P <sub>out</sub> [dBm] | RBW=30kHz, VBW=100Hz |         |        |  |  |

|                        | + 10MHz              | - 15MHz | +20MHz |  |  |

| 43                     | 17.68                | 17.16   | 12.94  |  |  |

| 42                     | 22.15                | 21.01   | 14.78  |  |  |

| 41                     | 22.39                | 20.54   | 15.21  |  |  |

| 40                     | 23.01                | 22.22   | 16.05  |  |  |

| 39                     | 21.11                | 20.45   | 14.31  |  |  |

| 38                     | 20.44                | 21.32   | 13.37  |  |  |

| 37                     | 19.23                | 20.35   | 11.44  |  |  |

| 36                     | 18.53                | 19.94   | 10.86  |  |  |

| 35                     | 17.03                | 18.84   | 8.88   |  |  |

| 34                     | 15.82                | 18.16   | 7.03   |  |  |

| 33                     | 12.84                | 14.68   | 5.77   |  |  |

| 32                     | 10.33                | 12.92   | 3.76   |  |  |

| 31                     | 9.09                 | 10.81   | 1.96   |  |  |

| 30                     | 4.96                 | 6.66    | 0.46   |  |  |

| 29                     | 2.83                 | 5.63    | 0.61   |  |  |

| 28                     | 2.70                 | 4.36    | 0.07   |  |  |

| 27                     | 2.15                 | 2.92    | 1.04   |  |  |

그림 6.10 동적 출력 전력 레벨에 따른 ACPR 개선 특성. Figure 6.10 ACPR improvements at the dynamic power level.

#### 제 7 장 결론

통신 시장의 급변화로 이동 통신용 고출력 소자들의 고효율 특성과 효과적인 선형화 개선 방법에 관심이 집중되어 있다. 따라서 본 논문에서는 기존의 선형화 개선 특성이 탁월한 피드포워드 방식과전치 왜곡 선형화 기법을 접목하여 좀 더 효과적인 선형화 기술을 제시했다.

평형 전력증폭기 최종 출력 단의 평균 출력 레벨이 40dBm 일 때와 41dBm 일 경우, 각각 제안된 선형화 기술을 적용하여 중심 주파수에서 12.5MHz 이격된 지점에서 ACPR 개선량이 23.01dB와 22.38dB로 개선됨으로 우수한 성능을 보여주고 있다.

평형 전력증폭기의 MA에서 추출된 혼변조 신호를 이용하여 PDMA의 입력에 주입하는 방식을 취하고 있기 때문에 추가적인 오차 신호 증폭기가 요구되지 않아 효율적인 면에서 유리하다. 또한 기존 특허에서 제시된 평형 구조의 혼변조 제거 방식은 평형 전력 증폭기에서 동일한 두 개의 전력증폭기를 사용하였지만, 이론적으로는 동일한 전력증폭기를 사용해도 무관하지만, 효율적인 선형화 동작 특성을 얻기 위해 오차 신호의 생성에 이용되는 MA는 비교적 선형성이 낮게 조정을 하였고, 반면 전치 왜곡 개념을 접목하는 PDMA는 상대적으로 선형성이 우수하게 조정하였다[25]. 그리고 기존의 피드포워드 구조에서는 루프 별 지연 선로의 효과를 균형적으로 유지해야 하지만, 본 논문에서는 일부의 지연 선로의 군속도 지연 효과가 발생하게 되어 선형화 개선의 규명에 효과적이다. 측정

결과에서 알 수 있듯이 우수한 선형성 개선 효과와 넓은 동적 전력 범위를 가지기 때문에 이동 통신용 고출력 소자의 선형성 개선 기 술에 적절히 응용될 것이라고 기대된다.

### 참 고 문 헌

- [1] Kenington P.B., Wilkinson R.J., and Marvill J.D., "Power Amplification Techniques for Linear TDMA Base Station," *IEEE Global Telecommunication Conf.*, vol. 1, pp. 74–78, Dec. 1992.

- [2] Tri T.Ha, "Solid-state Microwave Amplifiers Design," A Wiley-interscience publication, 1981.

- [3] Fredric H Raab, Peter Asbeck, Steve Cripps, Peter B Kennington, Zoya B. Popovic, Nick Pothecary, John F. Sevic, Nathan O. Sokal, "Power Amplifiers and Transmitter for RF and Microwave," *IEEE Trans. on MTT*, vol. 50, no. 3, pp. 814–826, Mar. 2002.

- [4] Allen Katz, et al., "Distortion Correction of High Power Amplifier Using Digital Signal Processing," *IEEE MTT-S Workshop Proc.*, 2004.

- [5] 정용채, "이동통신기지국용 대전력 증폭기 설계 기술," *전자파기술*, 14권, 4호, pp. 39-49, 2003년 10월.

- [6] Lubell P.D., Dennston W.B., and Hertz R.F., "Linearizing Amplifiers for Multi-signal Use," *Microwaves*, pp. 46-50, 1974.

- [7] Y. S. Lee, I. Brelian, A.Atia, "Linearized Transponder Technology for Satellite Communication Part II: System Simulation and Performance Assessment," *Comsat Technical Review*, vol.15, No.2A, pp.309-330, Fall 1985.

- [8] Gunkichi Satoh, Toshio, "Impact of a New TWTA Linearizer Upon QPSK/TDMA Transmission Performance," *IEEE Journal of Selected Areas in Conn.*,vol. Sac-1, No.1, pp.39-45, 1983.

- [9] Steve C. Cripps, "RF power Amplifiers for Wireless Communications," (Artech house, Boston. London)

- [10] Nick Pothecary, "Feedforward Linear Power Amplifiers," (Artech

- House, 1999), pp.124

- [11] Hee-Young Jeong, Sang-Keun Pack, Nam-Sik Ryu, Yong-Chae Jeong, In-Bok Yom, Young Kim, "A Design of K-band Predistortion Linearizer using Reflective Schottky Diode for Satellite TWTAs," *European Microwave Conference*, pp. 321-324, October 2005.

- [12] John L.B. Walker, "High Power GaAs FET Amplifier," (Artech House, 1993), pp.315-351

- [13] D. Cahana, J. R. Potukuchi, R. G. Marshalek, D.K. Paul, "Linearized Transponder Technology for Satellite Communication Part I: Linearizer circuit Development for Experimental Characterization," Comsat Technical Review, vol.15, No.2A, pp227-308, Fall 1985.

- [14] H. Seidel, "A Microwave Feed-Forward Experiment," *Bell System Technical Journal*, vol. 50, No. 9, pp.2879-2916, Nov. 1971.

- [15] H. Seidel, "A Feed-Forward Experiment Applied to an L-4 Carrier System Amplifier," *IEEE Trans. Comm.* vol. COM-19, No. 3, pp.320-325, June, 1971.

- [16] David. M. Pozar, "Microwave Engineering," (John Wiley & Sons, INC, 1998), pp. 379-383.

- [17] J. F. White, "Microwave semiconductor engineering," (Van Nostrand, NJ, 1982).

- [18] R.V.Garver, "360° Varactor diode linear phase modulator", *IEEE Trans, on Microwave Theory and Tech.*, vol. MTT-17, pp.137-147, March, 1969.

- [19] S. Hopfer, "Analog Phase Shifter for 8-18GHz," *Microwave Journal*, Vol.22, pp.48-50, March, 1979.

- [20] R.H.Hardin, E. J.Downey, and J.Munushian, "Electronically variable phase shifters utilizing variable capacitance diodes", *Proc. IRE (Letter)*, Vol. 48, pp.944-945, May, 1960.

- [21] Stewart Walker, "A Low Phase Shift Attenuator," *IEEE Trans.* vol.MTT-42, No.2, pp.182-185, Feb., 1994.

- [22] Won-tae Kang, "Reflection Type Low Phase Shift Attenuator," *IEEE trans. Microwave Theory and Tech*, vol.46, No.7, pp.1019-1221, July, 1988.

- [23] David. M. Pozar, "Microwave Engineering," (John Wiley & Sons, INC, 1998), pp. 395-400.

- [24] E. H. Fooks, "Microwave Engineering using Microstrip Circuits," (Prentice Hall, 1990), pp. 155–166.

- [25] Mark Billsberry, Melbourne Beach, FL, "BALANCED DISTORTION REDUCTION CIRCUIT," *United States Patent*, Patent No. US 6,734,726 B2, May, 11, 2004.

- [26] Yoichiro Takayama, "Considerations for High-Frequency Operation of Microwave Transistor Power Amplifiers," *IEEE Trans, on Microwave Theory and Tech.*, vol.b80c, No.6, pp.726-732, June, 1997.