# 새로운 고조파 차단회로망을 이용한 RF 에너지 수확 시스템용 고효율 RF-DC 정류회로 설계

2011년 8월 22일

전 북 대 학 교 대 학 원

전자정보공학부

심 성 운

# 새로운 고조파 차단회로망을 이용한 RF 에너지 수확 시스템용 고효율 RF-DC 정류회로 설계

Design of High Efficiency RF-DC Conversion Circuit

using Novel Harmonics Termination Network

for RF Energy Harvesting System

2011 년 8월 22일

전 북 대 학 교 대 학 원

전자정보공학부

심 성 운

# 새로운 고조파 차단회로망을 이용한 RF 에너지 수확 시스템용 고효율 RF-DC 정류회로 설계

지도교수 정 용 채

이 논문을 공학 석사 학위논문으로 제출함.

2011 년 8월 22일

전 북 대 학 교 대 학 원

전자정보공학부

심 성 운

## 심성운의 석사학위논문을 인준함

위원장 전북대학교 부교수 손 해 원

위원 전북대학교 조교수 김정무

위원 전북대학교 교수 정용채

2011年 8月22日

전 북 대 학 교 대 학 원

## 목 차

| Α             | he  | tra | cts   |

|---------------|-----|-----|-------|

| $\overline{}$ | 115 | u a | C.I.S |

| 제 | 1 장 서 론                      | 1           |

|---|------------------------------|-------------|

| 제 | 2 장 렉테나                      | 4           |

|   | 제 1 절 렉테나의 정의                | 4           |

|   | 제 2 절 렉테나의 효율                | <b></b> 5   |

|   | 제 3 절 정류기                    | 8           |

|   | 제 4 절 Villard 전압 채배기         | 9           |

|   | 제 5 절 RF-DC 변환효율 향상을 위한 고려사항 | - 14        |

|   | 제 6 절 쇼트키 다이오드               | · 16        |

| 제 | 3 장 새로운 고조파 차단 회로망의 제안       | <b>-</b> 19 |

|   | 제 1 절 RF 다이오드의 비선형 특성        | - 19        |

|   | 제 2 절 고조파 차단 회로망             | - 23        |

|   | 3.2.1 E급 전력증폭기               | - 23        |

|   | 3.2.2 정류회로를 위한 고조파 차단 회로망    | - 25        |

|   | 제 3 절 새로운 고조파 차단 회로망의 제안     | - 27        |

|   | 3.3.1 출력단 고조파 차단 회로망         | - 27        |

|   | 3.3.2 입력단 고조파 차단 회로망         | - 29        |

|   | 3.3.3 입력 임피던스 정합회로           | - 32        |

| 제 | 4 장 제안된 고조파 차단 회로망의 시뮬레이션    | - 34        |

|   | 제 1 절 출력단 고조파 차단 회로망         | - 34        |

| 제 2 절 입력단 고조파 차단 회로망   | 38   |

|------------------------|------|

| 제 3 절 정류회로의 설계         | 42   |

| 제 5 장 제작 및 측정          | 47   |

| 제 1 절 출력단 고조파 차단 회로망   | 47   |

| 제 2 절 부하저항 및 커패시터 최적화  | 50   |

| 제 3 절 입력단 고조파 차단 회로망   | . 54 |

| 제 4 절 RF-DC 정류회로의 출력특성 | 57   |

| 제 6 장 결 론              | 63   |

| 참고논문                   | 65   |

|                        |      |

## 그 림 목 록

| 그림   | 1.1 RF 에너지 수확 기술의 개념도                              | 2  |

|------|----------------------------------------------------|----|

| 그림 : | 2.1 마이크로파 렉테나의 기본 구성도                              | 4  |

| 그림 : | 2.2 RF Energy Harvesting System의 블록 다이어그램          | 6  |

| 그림 : | 2.3 정류기의 다양한 구조                                    | 9  |

| 그림 : | 2.4 2단 Villard 전압 채배기 :                            | 13 |

| 그림   | 2.5 대칭 및 병렬 구조의 Villard 전압 채배기                     | 13 |

| 그림 : | 2.6 RF-DC 변환효율 향상을 위해 사용하는 일반적인 렉테나 구조 [           | 15 |

| 그림 : | 2.7 HSMS2822의 패키지 구조 :                             | 16 |

| 그림 : | 2.8 HSMS2822의 선형 등가회로 모델 :                         | 17 |

| 그림 : | 3.1 쇼트키 다이오드의 전압-전류 특성                             | 19 |

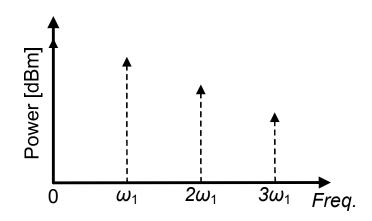

| 그림 : | 3.2 1-tone 신호가 입력될 때 다이오드의 비선형 주파수 응답 특성 - 2       | 22 |

| 그림   | 3.3 E급 전력중폭기의 기본 회로도와 고조파 차단을 위한 부하 회로망            | 의  |

| 주파수  | 우에 따른 동작                                           | 24 |

| 그림   | 3.4 고효율 특성을 위한 트랜지스터의 이상적인 전압과 전류 파형 2             | 24 |

| 그림 : | 3.5 고조파 차단 회로망을 이용한 RF Energy Harvesting System의 회 | 로  |

| 도    |                                                    | 26 |

| 그림   | 3.6 출력단 고조파 차단 회로망의 개념도                            | 28 |

| 그림 : | 3.7 주파수에 따른 출력단 고조파 차단 회로망의 동작                     | 29 |

| 그림   | 3.8 입력단 고조파 차단 회로망의 회로도 3                          | 30 |

| 그림   | 3.9 주파수에 따른 입력단 고조파 차단 회로망의 동작 3                   | 30 |

| 그림   | 3.10 입력단 고조파 차단 회로망에 스터브를 이용한 임피던스 정합    | 32 |

|------|------------------------------------------|----|

| 그림   | 4.1 ADS에서 구현한 출력단 고조파 차단 회로망의 회로도        | 34 |

| 그림   | 4.2 출력단 고조파 차단 회로망의 ADS 회로 시뮬레이션 결과      | 35 |

| 그림   | 4.3 HFSS에서 구현한 출력단 고조파 차단 회로망의 회로도       | 36 |

| 그림   | 4.4 출력단 고조파 차단 회로망의 EM시뮬레이션 결과           | 37 |

| 그림   | 4.5 ADS에서 구현한 입력단 고조파 차단 회로망의 회로도        | 38 |

| 그림   | 4.6 입력단 고조파 차단 회로망의 ADS 회로 시뮬레이션 결과      | 39 |

| 그림   | 4.7 HFSS에서 구현한 입력단 고조파 차단 회로망의 회로도       | 40 |

| 그림   | 4.8 입력단 고조파 차단 회로망의 EM시뮬레이션 결과           | 41 |

| 그림   | 4.9 HSMS2822을 이용하여 구현한 Vilallard 전압 채배기  | 43 |

| 그림   | 4.10 입력 임피던스 정합 전과 후의 출력 직류전압 비교         | 43 |

| 그림   | 4.11 출력단 고조파 차단 회로망 사용전과 후의 출력 직류전압 특성 - | 44 |

| 그림   | 4.12 출력단 고조파 차단 회로망 사용전과 후의 출력 전력에 다     | 바한 |

| Harn | nonic Balance 시뮬레이션 결과                   | 45 |

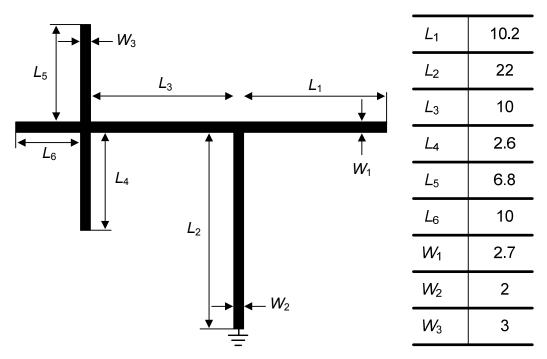

| 그림   | 5.1 출력단 고조파 차단 회로망의 도면과 치수               | 47 |

| 그림   | 5.2 제작된 고조파 차단 회로망의 사진                   | 48 |

| 그림   | 5.3 출력단 고조파 차단 회로망의 EM시뮬레이션과 측정 결과의 비교   | 49 |

| 그림   | 5.4 출력단 고조파 차단 회로망의 반사계수 특성              | 50 |

| 그림   | 5.5 부하저항 최적화를 위해 사용된 회로                  | 51 |

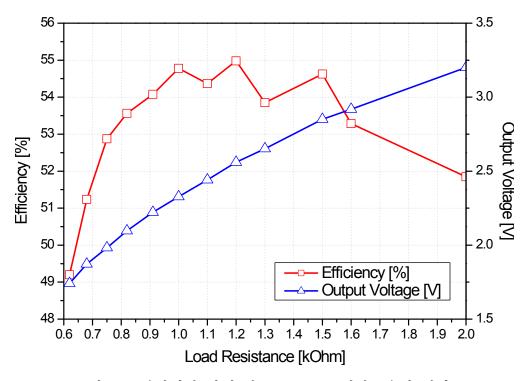

| 그림   | 5.6 부하저항 값에 따른 RF-DC 변환효율의 변화            | 52 |

| 그림   | 5.7 직렬 커패시턴스에 따른 출력전압의 변화                | 53 |

| 그림   | 5.8 부하 커패시턴스에 따른 출력전압의 변화                | 53 |

| 그림 | 5.9  | 입력단 고조파 차단 회로망의 도면과 치수             | 54 |

|----|------|------------------------------------|----|

| 그림 | 5.10 | 제작된 입력단 고조파 차단 회로망의 사진             | 55 |

| 그림 | 5.11 | 입력단 고조파 차단 회로망의 EM시뮬레이션과 측정 결과의 비교 | 55 |

| 그림 | 5.12 | 입력단 고조파 차단 회로망의 반사계수 특성            | 56 |

| 그림 | 5.13 | 완성된 RF-DC 정류회로의 사진                 | 58 |

| 그림 | 5.14 | RF-DC 정류회로의 변환효율과 출력전압 특성          | 58 |

| 그림 | 5.15 | 고조파 차단회로 사용에 따른 RF-DC 변환효율 비교      | 60 |

## 표 목 록

| 표 | 2.1 | HSMS2822의 전기적 특성                 | 18 |

|---|-----|----------------------------------|----|

| 丑 | 2.2 | HSMS2822의 SPICE 파라미터             | 18 |

| 丑 | 5.1 | 입력단 고조파 차단회로망과 다이오드의 입력 임피던스 정합점 | 56 |

| 丑 | 5.2 | RF-DC 정류회로의 변환효율과 출력전압 특성        | 59 |

| 표 | 5.3 | 렉테나에 관한 이전 연구들의 측정요약 및 성능 비교     | 62 |

본 논문은 RF Energy Harvesting System 구현을 위한 렉테나용 고효율 RF-DC 정류회로를 제안하였다. 고효율 전력증폭기에서 사용되는 고조파 차단부하 회로망의 개념을 적용하여 새로운 구조의 고조파 차단회로망을 설계하고 정류회로의 입·출력단에 배치하였다. 제안된 출력단 고조파 차단회로망을 이용하면 정류회로의 출력에서 발생하는 다이오드의 비선형 성분을 차단함으로써 출력 직류전력의 분산을 막아 RF-DC 변환효율의 향상을 기대할 수 있다. 또한 입력단 고조파 차단회로망을 이용하면 다이오드의 정류작용에서 발생하는 비선형 성분이 안테나로 재방사되어 나가는 것을 차단할 수 있고, 고조파 차단회로망 자체로 안테나와의 입력 임피던스 정합을 할 수 있어서 효율향상은 물론 회로 구현을 쉽게 할 수 있다는 장점이 있다.

동작주파수가 2.45 GHz인 본 회로를 측정한 결과 140 mW의 RF 전력이 인가되었을 때 10.59 V 의 직류전압이 측정되었고 이때 약 80.59 %의 RF-DC 변환효율을 얻을 수 있었다. 제작된 회로의 크기는 80mm × 55mm이다.

주요어: 렉테나, 하베스팅, 정류기, 무선전력전송, 고조파 차단회로

#### **Abstract**

# Design of High Efficiency RF-DC Conversion Circuit using A Novel Harmonics Termination Network for RF Energy Harvesting System

Shim Sungun

Division of Electronic and Information Engineering

Chonbuk National University

In this thesis, high efficiency RF-DC conversion circuit has been presented for a RF Energy Harvesting System. A novel harmonic termination network has been designed by utilizing the concept of the harmonic termination load network used in the high efficiency power amplifier design. The proposed harmonic termination network has been used in the input and output stage of RF-DC conversion circuit. The proposed output harmonic termination network in the output stage can forbid nonlinear components generated from diode and an improvement of RF-DC conversion efficiency can be expected. Also, the proposed input harmonics termination network in the input stage can prohibit nonlinear components reradiated from diode to the antenna and can match to the input impedance of antenna as matching network. The proposed circuits has advantages of a simple design and improvement of efficiency.

The size of the fabricated circuit operating at  $2.45~\mathrm{GHz}$  is  $80~\mathrm{mm}~\times~55~\mathrm{mm}$

mm. It has maximum RF-DC conversion efficiency of 80.59 % at input RF power of 140 mW.

keywords: rectenna, harvesting, rectifier, wireless power transmission, harmonic termination network

### 제 1 장 서 론

전자기파를 이용하여 무선으로 전원을 공급하기 위한 연구가 테슬라에 의해 제안된 이후 전 세계적으로 이 분야에 대한 주도권을 갖기 위하여 다양한 연구가 진행되고 있다. 최근에는 휴대용 무선 통신 단말기 사용이 보편화되고 다양한 통신 기술이 서비스되면서 회로의 소형화에 걸림돌이 되고 있는 배터리와 전선 문제를 해결하고 전원 공급과 충전을 무선으로 실현하려는 연구와 함께센서 네트워크의 전원 공급을 위한 배터리의 제한과 공간적 장벽을 무너뜨리는 새로운 전원 공급 방법에 대한 연구도 여러 분야에서 진행되고 있다 [1] - [3]. 특히 2007년 MIT 물리학과의 솔야치치 그룹에서 Science지에 발표한 자기 공명 방식을 이용한 논문이 기존의 비공진형 유도 방식과는 다른 새로운 해석과 접근으로 근접장에서 무선으로 전구를 결 수 있다는 것을 보인 후, 2008년이 기술이 미래 사회의 10대 유망 기술 중 하나로 선택되면서 무선 전력 전송분야가 더욱 주목 받고 있다 [4] - [5].

무선 전력 전송(Wireless Power Transmission, WPT)은 전력에너지를 마이크로파로 변환시켜 에너지를 전달하는 새로운 개념의 전력 전송 방식으로 전선없이 전기에너지를 공간을 통해 보낼 수 있는 전파전송의 원리이다. 라디오나무선전화기 등과 같이 무선 통신 방식에서 이용하는 신호의 개념이 아닌 전기에너지를 보내는 것으로 보통의 통신이 반송파에 신호를 실어 보내는 것이라면무선 전력 전송은 반송파만 보내는 것이다.

최근 유비쿼터스 센서 네트워크가 큰 시장으로 성장할 것이 예상됨에 따라 소

형 이동체나 전원공급이 어려운 환경에서 동작하는 시스템에 전원을 공급하는 무선 전력 전송기술의 응용의 폭이 훨씬 넓어질 것으로 예상되며, RFID 시스템의 수동형 태그에 전력을 공급하는 것 역시 응용분야의 중요한 사례로 부각되고 있다.

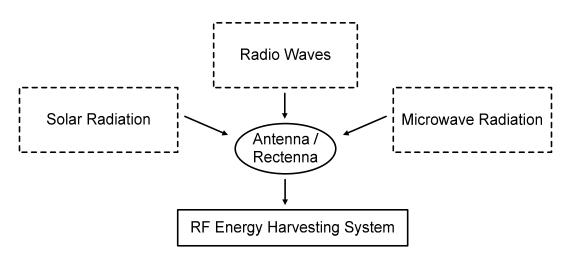

이러한 시스템을 구동하기 위해서 무선주파수 신호를 에너지 공급원으로 사용하기 위한 시도가 진행되고 있다. 기기가 위치한 장소나 개수에 관계없이 구동되기 위해 기기 주변의 전자파원을 이용할 수 있다면 연료 교환과 충전에 대한 걱정을 하지 않아도 에너지 공급원에 대한 문제를 해결할 수 있다. 에너지원을 만들기 위하여 직접 전자파를 방사하거나, 다양한 통신기술의 발달에 따라 대기 중에 발생하는 불요 전자파를 이용할 수도 있다. 주변의 전자파원을 활용하여 에너지를 재생산하는 기술을 특히 RF 에너지 수확 시스템(RF Energy Harvesting System 혹은 RF Energy Scavenging System)이라 부른다.

그림 1.1 RF 에너지 수확 시스템의 개념도.

Fig. 1.1 Concept for RF energy harvesting system.

렉테나는 대기 중의 전자파를 에너지 원으로써 손쉽게 채집하여 이용할 수 있도록 사용하는 대중적인 장치이다. RF 에너지 수확 시스템을 이용하여 센서와 같은 기기를 구동할 수 있을 정도로 전력을 얻기 위해서는 렉테나에 비교적 큰 RF 전력을 수신하여야 한다. 그러나 이를 위해 높은 전력을 무분별하게 방사할 경우 다른 기기의 장해 및 인체에도 해로운 영향을 끼칠 수 있어 국가별로 전자기파에 의한 인체의 영향을 고려하여 허용 전력 밀도에 대한 제한도 두고 있다 [6].

이러한 문제로 인하여 무선 기기들을 원활이 동작시키기 위해 고효율의 렉테 나 사용이 요구된다. 공중파 전력을 전기에너지로 변환할 때 효율이 낮은 렉테 나를 이용하게 되면 보다 많은 전력을 방사해야 하기 때문이다.

본 논문에서는 RF 에너지 수확 시스템을 구현하기 위해 ISM 대역인 2.45 GHz 주파수에서 RF 신호를 수신하여 직류 전력으로 변환하는 렉테나를 위한 고효율 RF-DC 정류회로를 설계하였다. RF-DC 변환효율을 높이기 위하여 고효율 전력증폭기 개발에 이용된 고조파 차단 회로망 개념을 이용하여 새로운 구조의 고조파 차단 회로를 RF-DC 정류회로에 적용하여 제작 및 측정하였다.

## 제 2 장 렉 테 나

#### 제 1 절 렉테나의 정의

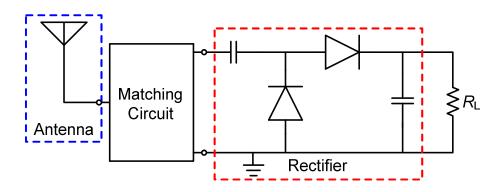

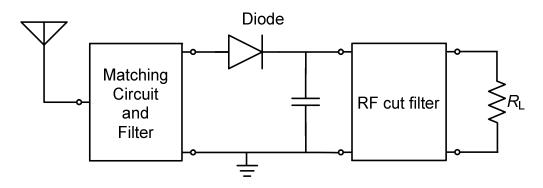

RF Energy Harvesting System에서 수전된 마이크로파를 직류로 변환시키기위한 회로를 렉테나라고 하며, 일반적으로 그림 (2-1)과 같이 구성한다. 렉테나는 정류기(Rectifier)와 안테나(Antenna)를 합성한 말로 두 회로를 조합한구조로 되어 있다. 대기를 통해 날아온 마이크로파 전력을 안테나로 수전하여다이오드 및 여파기로 구성된 정류기를 통과하면 직류 전력을 얻을 수 있다. 기기구동에 필요한 전력은 렉테나를 필요한 수만큼 연결하여 얻을 수 있다. [7], [9], [29], [30].

'렉테나'라고 불리는 이 회로에서 정류기는 동작주파수에 따라 AC-DC 정류회로 또는 RF-DC 정류회로라 부른다.

그림 2.1 마이크로파 렉테나의 기본 구성도.

Fig. 2.1 Basic topology of microwave rectenna.

#### 제 2 절 렉테나의 효율

렉테나의 RF-DC 변환효율은 수전된 RF 전력 대비 변환된 직류 전력의 비로써 부하저항에 나타나는 전압을 측정하여 식 (2-1)과 같이 구할 수 있다. 그림 2.1의 RF Energy Harvesting System에서 높은 RF-DC 변환효율을 얻기위해서는 안테나와 정류기 사이에 임피던스 정합회로를 이용하여 부하에 최대전력이 전달되도록 해야한다.

$$\eta = \frac{P_{\rm DC}}{P_{\rm RF}} = \frac{V_{\rm DC}^2 / R_{\rm L}}{P_{\rm RF}}$$

(2-1)

$P_{\mathrm{RF}}$ 는 안테나에 수전된 RF 전력이며,  $P_{\mathrm{DC}}$ 는 렉테나의 부하에서 측정된 직류 전력이다.

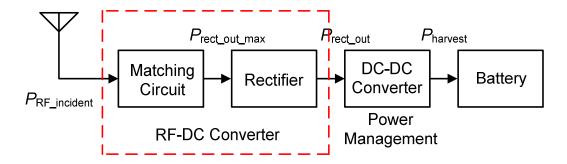

그림 2-2는 RF Energy Harvesting System을 세분화하여 블록 다이어그램으로 나타낸 것이다. 렉테나의 뒤에는 배터리나 특정 기능을 하는 기기가 부하로써 위치하는데, 이 회로들이 요구하는 적절한 전압을 제공하기 위해 DC-DC 변환기가 부하 앞에 위치한다. 이 DC-DC 변환기는 렉테나를 통해 최대의 직류 출력전력을 얻을 수 있도록 렉테나에서 부하를 바라보았을 때 일정한 저항으로 보이게 하는 역할도 수행한다.

그림 2-2를 통해 각 블록에서의 전력변환 효율을 정의할 수 있으며, 전체 효율에 영향을 미치는 부분이 무엇인지 파악할 수 있다. 다음은 전력변환 효율을 블록마다 수식으로 정리하였다.

그림 2.2 RF Energy Harvesting System의 블록 다이어그램.

Fig. 2.2 Block diagram of RF Energy Harvesting System.

식 (2-2)는 안테나를 통하여 입사된 전력 대비 정류기에 인가되는 전력이 어느 정도인지를 나타내는 효율을 나타낸다. 이를 통해 안테나와 정류기간의 정합 정도를 확인할 수 있다.

$$\eta_{\text{RF\_conversion}} = \frac{P_{\text{rectenna\_out\_max}}}{P_{\text{RF\_incident}}}$$

(2-2)

식 (2-3)은 정류기에 인가된 전력이 얼마나 손실 없이 정류되어 나가는지를 나타내는 것으로 정류기에 인가된 전력 대비 정류기의 출력전력으로 나타내는 효율은 다음과 같다.

$$\eta_{\text{track}} = \frac{P_{\text{rectenna\_out}}}{P_{\text{rectenna\_out\_max}}}$$

(2-3)

정류기에서 변환되어 얻어진 직류 전압은 DC-DC 변환기를 통해 부하가 요 구하는 전압으로 변환할 수 있는데, 이 변환 과정에서 발생한 손실을 나타내기 위하여 정류기의 출력 직류 전력 대비 DC-DC 변환기의 출력 직류 전력으로 나타내는 효율은 다음과 같다.

$$\eta_{\text{converter}} = \frac{P_{\text{harvest}}}{P_{\text{rect out}}}$$

(2-4)

최종적으로 RF Energy Harvesting System에 인가되는 전력 대비 배터리에서 얻을 수 있는 전력으로써 전체 시스템 효율을 다음과 같이 정의할 수 있다.

$$\eta_{\text{system}} = \frac{P_{\text{harvest}}}{P_{\text{RF\_incident}}}$$

(2-5)

본 논문에서는 센서나 수동형 RFID 태그와 같은 소형 회로에 적용할 수 있도록 단순한 구조의 렉테나를 설계하기 위하여 그림 2.2에서 DC-DC 변환기는 생략된 구조를 이용하였다. 따라서 전체 RF-DC 변환효율에 영향을 미치는 요소로 안테나와 정류기 사이에서 임피던스 정합과 정류기에서의 손실을 고려해야 한다.

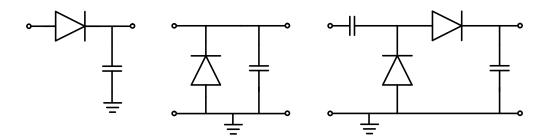

#### 제 3 절 정 류 기

정류기는 다이오드의 한쪽 방향으로만 전류를 통과시키는 성질을 이용한 것으로 주기적으로 양과 음 두 방향으로 변화하는 교류 전압을 직류 전압으로 변환시키는 장치이다. 높은 동작주파수에서는 RF-DC 정류회로라고 불리는 이 회로는 다이오드의 배열에 따라 몇 가지로 구성할 수 있다.

그림 2.3의 (a)나 (b)처럼 단일 다이오드를 직렬이나 병렬로 구성하거나, 그림 2.3의 (c)처럼 복수의 다이오드를 이용하여 정류기를 구성할 수도 있다. 그림 2.3의 (c)와 같은 회로는 출력 직류 전압을 증폭시키기 위하여 주로 사용되며, Villard 전압 체배기로 불린다.

이상적인 다이오드는 가장 기본적인 비선형 소자이며 기준 방향에 대해 양의 전압이 공급되면 다이오드 양단에 걸리는 전압은  $0\ V$  가 되어 전압 강하는 없고 전류만 흐르는 단락회로처럼 동작한다. 이 때 단일 다이오드로 구성된 정류기에 RF 신호가 인가되면 신호의 피크(peak) 전압은 그대로 커패시터에 충전되어 출력 직류 전압은  $V_{\rm out} \approx V_{\rm in,peak}$  가 된다. 그러나 다이오드가 순방향으로 동작하기 위해서는 문턱전압이 필요하므로, 정류기의 출력 직류 전압은  $V_{\rm out} = V_{\rm in,peak} - V_{\rm th}$ 로 나타낼 수 있다.

정류기의 출력 직류 전압은 사용된 다이오드 개수에 비례하며, 다음과 같이 일반화하여 나타낼 수 있다.

$$V_{\text{out}} = N(V_{\text{in,peak}} - V_{\text{th}}) \tag{2-6}$$

여기서 N은 다이오드의 개수이다.

그림 2.3 다양한 정류기 구조 : (a) 직렬 연결 구조, (b) 병렬연결 구조, (c) Villard 전압 체배기.

Fig. 2.3 Various rectifier structure: (a) series connected structure, (b) parallel connected structure, and (c) Villard voltage multiplier.

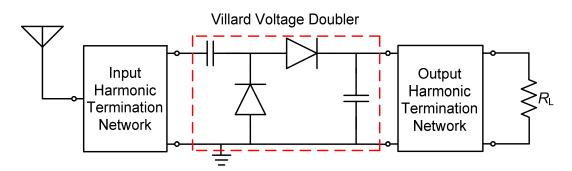

#### 제 4 절 Villard 전압 체배기

Villard 전압 체배기는 Cockcroft-Walton 전압 체배기로도 불리며, 이미 전력전자 분야에서 정류기를 구현하기 위해 광범위하게 사용되고 있는 회로이다. 다이오드와 커패시터 두 쌍으로 이루어진 비교적 단순한 구조로, 입력 RF 신호의 피크 전압의 두 배의 출력 직류 전압을 손쉽게 얻을 수 있기 때문에 가장대중적으로 사용되고 있다.

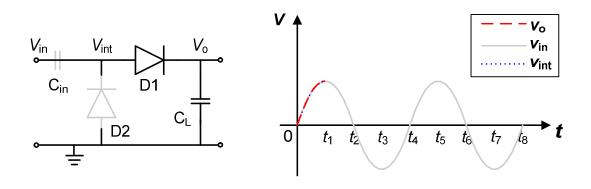

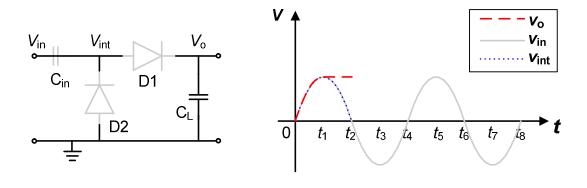

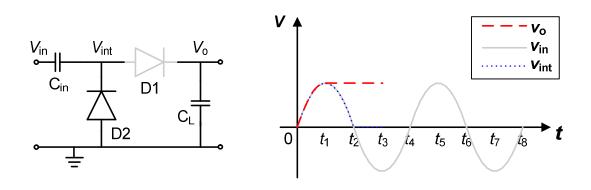

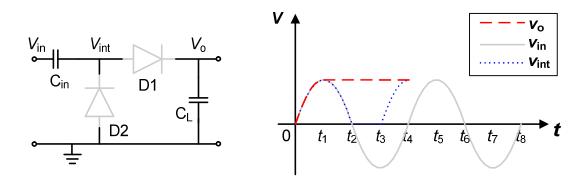

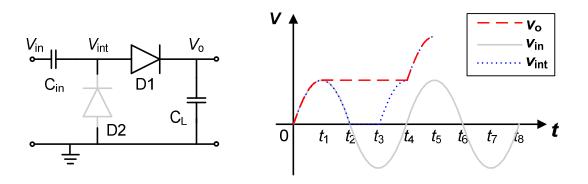

Villard 전압 체배기에 특정주파수를 갖는 연속적인 신호가 인가될 때의 동작원리를 살펴본다. 이 때 다이오드는 이상적이고 직렬 커패시터  $C_{\rm in}$ 과 부하 커패시터  $C_{\rm L}$ 의 초기 전압은 0 V 로 가정한다.  $V_{\rm int}$ 는  $C_{\rm in}$ 의 다이오드 방향의 극

의 전압을 나타내며,  $V_{

m in,peak}$  는 입력 RF 신호의 peak 전압을 나타낸다.

(1)  $0 \sim t_{\rm l}$  : 입력 신호가 양의 주기인 이 구간에서 D1은 순방향 바이어스가 가해져서 단락되고, D2는 역방향 바이어스가 가해져서 개방된다. 양의 주기 동안  $V_{\rm in,peak}$  만큼  $C_{\rm L}$ 에 충전되며,  $V_{\rm int}$ 는  $C_{\rm L}$ 에 충전된 전압과 같은  $V_{\rm in,peak}$ 가 된다.

(2)  $t_1 \sim t_2$  : 이 구간에서  $V_{\rm int}$  의 전압은  $V_{\rm o}$ 보다 낮기 때문에 D1은 개방되고, D2에는 역방향 바이어스가 가해져서 역시 개방된다. 출력 전압은  $C_{\rm L}$  에 충전되어 있는 전압이 그대로 나타난다.

(3)  $t_2 \sim t_3$  : 입력 신호가 음의 주기로 바뀌는 이 구간에서 D1은 역방향 바이어스가 가해져서 개방되고, D2는 순방향 바이어스가 가해져서 단락된다.  $V_{\rm int}$ 는 접지와 연결되어 있으므로  $0~\rm V$  로 고정되며,  $C_{\rm in}$ 에는  $-V_{\rm in,peak}$ 가 충전된다.

(4)  $t_3 \sim t_4$  : 이 주기에서 입력신호는  $C_{

m in}$ 의 전압을  $V_{

m in,peak}$  만큼 밀어올려  $V_{

m int}$ 는  $V_{

m in,peak}$ 가 되고 D2는 역방향 바이어스가 가해져서 개방된다.

(5)  $t_4 \sim t_5$  : 입력 신호가 양의 주기로 바뀌는 이 구간에서 입력 신호가  $C_{\rm in}$  의전압을 다시  $V_{\rm peak}$  만큼 밀어올려  $V_{\rm int}$ 는  $2V_{\rm peak}$ 가 된다.  $V_{\rm int}$ 가  $C_{\rm L}$ 에 충전되어 있는 전압보다 크기 때문에 D1은 순방향 바이어스가 가해져서 단락되고,  $V_{\rm int}$ 는

$C_{

m L}$ 에 충전되어 최종 출력 직류 전압은  $2V_{

m peak}$ 가 된다.

(6)  $t_{\rm 5}\sim$  : 이 구간에서  $V_{\rm int}$ 의 전압은  $V_{\rm o}$ 보다 낮기 때문에 D1은 개방되고, D2에는 역방향 바이어스가 가해져서 역시 개방된다.  $C_{\rm L}$ 에 충전되어 있는 전압은계속해서  $2V_{\rm peak}$ 를 나타낸다.

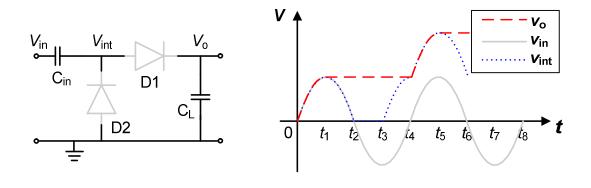

이와 같은 원리로 Villard 전압 체배기를 이용하여 2배의 출력 직류 전압을 얻을 수 있으며, 그림 2.4와 같이 Villard 구조를 여러 개 연결하거나 그림 2.5와 같이 2단 Villard 구조를 대칭 또는 병렬로 연결하여 더 높은 출력 전압을 얻을 수도 있다.

그림 2.4 2단 Villard 전압 체배기.

Fig. 2.4 2-stage Villard voltage multiplier.

그림 2.5 대칭 및 병렬 구조의 Villard 전압 체배기.

Fig. 2.5 Symmetry and parallel structure of Villard voltage multiplier.

RF Energy Harvesting System에서 마이크로파 입력 전력을 직류 전력으로 바꾸기 위해 사용하는 Villard 전압 체배기는 매력적인 구조이지만, 높은 출력 직류 전압을 얻기 위해서 너무 많은 다이오드로 구성하면 문턱전압으로 인하여 효율이 나빠지기 때문에, 효율에 최소한의 영향을 미치도록 단수를 선택할 필요가 있다.

#### 제 5 절 RF-DC 변환효율 향상을 위한 고려사항

RF Energy Harvesting System은 대기 중에서 전파를 받아 이를 직류전원으로 변환하여 사용하기 위한 목적을 가지고 있으므로 무엇보다도 렉테나가 높은 RF-DC 변환효율을 갖도록 설계해야 한다. 일반적으로 렉테나 설계시 효율향상을 위해 고려해야 할 점으로는 다이오드의 문턱전압과 비선형 특성으로 인한손실, 안테나와 정류기 사이의 임피던스 정합, 그리고 안테나의 효율적인 설계를 들 수 있다. 그림 2-6은 이런 사항들을 반영하여 렉테나가 높은 효율을 갖도록 타 연구에서 주로 사용하는 구조이다. 이 구조의 특징을 정리하면 다음과 같다.

- 1) 마이크로파 전력 수집 능력 향상을 위한 복수의 안테나의 배열. 또는 복수의 렉테나 배열.

- 2) 다이오드의 비선형 동작으로 인해 발생한 고조파가 안테나로 재방사되어 나가는 것을 막기 위해 안테나와 정류기 사이에 동작주파수 성분만을 통과시키 는 대역통과 필터를 삽입. 필터의 종단 임피던스를 각각 안테나와 정류기의 임 피던스로 선택하여 임피던스 정합이 가능하도록 함.

- 3) 다이오드의 문턱전압으로 인한 손실을 최소화하기 위한 정류기 구조 이용과 낮은 문턱전압을 갖는 쇼트키 다이오드의 선택.

- 4) 부하저항에 다이오드의 비선형 동작으로 발생한 고조파 성분을 차단하고 직류 전력만을 흐르게 하기 위한 고조파 차단 필터 삽입. 다이오드와 부하의

임피던스를 필터의 종단 임피던스가 되게 하여 필터 설계.

1)에서 언급한 것처럼 대기 중의 마이크로파를 더 많이 채집하기 위한 안테나 또는 렉테나 배열은 센서나 수동형 RFID 태그와 같이 소형으로 제작되어야하는 기기에는 공간 제약으로 인해 적합하지 않으므로 정류회로에서 효율상승을 위한 고려가 바람직하다.

2)와 4)에서 언급한 방법은 입력단과 출력단에서 각각 동작주파수와 직류 성분만을 통과시키는 필터를 사용하는데, 필터의 종단 임피던스가 임의의 임피던스를 갖도록 설계하면 회로 구현상의 복잡성 문제와 함께 필터의 삽입 손실로인하여 시스템 효율에 악영향을 미칠 수 있다. 이러한 문제로 인하여 다이오드의 비선형 동작으로 인한 문제와 임피던스 정합을 간단히 해결하기 위한 새로운 방법이 모색되어야 한다.

그림 2.6 RF-DC 변환효율 향상을 위해 사용하는 일반적인 렉테나 구조.

Fig. 2.6 Rectenna structure for improvement of RF-DC conversion efficiency.

렉테나에서 임피던스 정합과 다이오드의 비선형 동작으로 인한 효율감소 문제를 해결하기 위해 다음 장에서 고효율 전력증폭기에서 사용하는 고조파 차단회로망의 개념을 렉테나에 적용하는 방안에 대해 살펴보겠다.

#### 제 6 절 쇼트키 다이오드

RF Energy Harvesting System에 수전되는 신호의 주파수는 높고 이러한 신호가 수전단에 인가될 때는 신호의 크기가 상대적으로 작기 때문에, 정류기에 사용되는 다이오드는 시스템의 효율을 높이기 위해서 높은 동작주파수와 낮은 문턱전압이 요구된다. 이러한 조건을 충족시키기 위해 쇼트키 다이오드를 사용한다.

쇼트키(Schottky) 다이오드는 쇼트키 장벽에 의한 정류작용을 이용한 소자로 낮은 문턱전압과 매우 빠른 스위칭 속도를 갖는 반도체 다이오드이다. 높은 동작주파수를 갖는 회로에서 고효율 특성을 얻기 위하여 주로 사용된다.

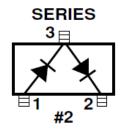

그림 2.7 HSMS2822의 패키지 구조.

Fig. 2.7 The package structure of HSMS2822.

본 연구에 사용된 쇼트키 다이오드는 Avago사의 HSMS-2822이며, 쇼트키다이오드 중에서도 낮은 문턱전압으로 인하여 렉테나 설계에 많이 이용되고 있다. 그림 2.7의 내부 패키기 구조가 Villard 전압 체배기에 이용하기 적합하게되어 있다.

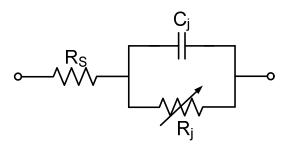

그림 2.8은 HSMS-2822의 등가회로 모델이며 다이오드의 전기적 특성 및 파라미터들이 다음 표에 제시되어 있다. RF-DC 변환효율에 가장 큰 영향을 미치는 문턱전압은 다이오드에 큰 전류가 흐르지 않는 이상 340 mV 정도를 유지한다.

R<sub>S</sub> = series resistance

C<sub>i</sub> = junction capacitance

$$R_{j} = \frac{8.33 \times 10^{-5} \text{ nT}}{I_{b} + I_{S}}$$

$I_b$  = externally applied bias current in amps

I<sub>S</sub> = saturation current

T = temperature, ∘K

n = ideality factor

그림 2.8 HSMS-2822의 선형 등가회로 모델.

Fig. 2.8 Linear equivalent circuit model of HSMS-2822.

#### 표 2.1 HSMS-2822의 전기적 특성.

Table 2.1 Electrical specifications of HSMS-2822 @  $T_{\rm C}$  =  $25^{\rm o}C$

| Part number          | Maximum<br>Forward Voltage<br>V <sub>F</sub> (mV) |     | Breakdown<br>Voltage<br>B <sub>V</sub> (V) | Maximum<br>Capacitance<br>C <sub>T</sub> (pF) | Dynamic<br>Resistance<br>$R_D(\Omega)$ |    |

|----------------------|---------------------------------------------------|-----|--------------------------------------------|-----------------------------------------------|----------------------------------------|----|

| HSMS2822             | 340                                               | 340 | 500                                        | 15                                            | 1.0                                    | 12 |

| @I <sub>F</sub> (mA) | 0.1                                               | 1   | 10                                         |                                               |                                        | 5  |

<sup>\*</sup>  $R_D = R_S + R_j$

표 2.2 HSMS-2822의 SPICE 파라미터.

Table 2.2 SPICE Parameters of HSMS-2822.

| Parameter       | Unit |                  |

|-----------------|------|------------------|

| B <sub>V</sub>  | V    | 15               |

| C <sub>J0</sub> | pF   | 0.7              |

| E <sub>G</sub>  | eV   | 0.69             |

| I <sub>BV</sub> | Α    | 1E <del>-4</del> |

| Is              | Α    | 2.2E-8           |

| N               |      | 1.08             |

| R <sub>S</sub>  | Ω    | 6.0              |

| P <sub>B</sub>  | V    | 0.65             |

| P <sub>T</sub>  |      | 2                |

| М               |      | 0.5              |

| ·               | .,,  |                  |

## 제 3 장 새로운 고조파 차단 회로망의 제안

#### 제 1 절 RF 다이오드의 비선형 특성

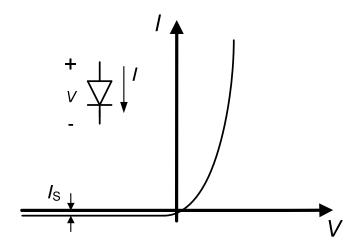

쇼트키 다이오드는 상대적으로 큰 접합 커패시턴스를 갖는 기존의 pn접합 다이오드와 달리 훨씬 작은 접합 커패시턴스로 인해 고주파 회로설계에 적합하다. 비선형 저항기로써 동작하는 쇼트키 다이오드의 소신호 전압-전류 특성은 다음과 같다.

$$I(V) = I_s(e^{\alpha V} - 1)$$

(3-1)

여기서  $\alpha=q/nkT$  , q 는 전자의 전하량, k 는 볼츠만 상수, T 는 온도 (=290K), n은 이상 계수,  $I_{\rm S}$ 는 포화전류 $(10^{-6}\sim 10^{-15}~{\rm A})$ 이다.

그림 3.1 쇼트키 다이오드의 전압-전류 특성.

Fig. 3.1 V-I characteristics of a Schottky diode.

그림 3.1은 일반적인 다이오드의 전압-전류 특성을 나타낸 것이다. 이 때 다이오드의 전압은 식 3-2로 나타낼 수 있다.

$$V = V_0 + v \tag{3-2}$$

여기서  $V_0$ 는 직류 바이어스 전압, v는 교류 소신호 전압이다.

식 3-1을  $V_0$ 중심에서 Taylor 급수로 전개하면 다음을 얻는다.

$$I(V) = I_0 + v \frac{dI}{dV}\Big|_{V_0} + \frac{1}{2}v^2 \frac{d^2I}{dV^2}\Big|_{V_0} + \frac{1}{6}v^3 \frac{d^3I}{dV^3}\Big|_{V_0} + \cdots$$

(3-3)

여기서  $I_0 = I(V_0)$ 는 직류 바이어스 전류이다.

$V_0$ 에서 I(V)의 1차 도함수는 다음과 같다.

$$\left. \frac{dI}{dV} \right|_{V_0} = \alpha I_S e^{\alpha V_0} = \alpha \left( I_0 + I_S \right) = G_d = \frac{1}{R_i}$$

(3-4)

여기서  $R_j$ 는 다이오드의 접합 저항이고,  $G_d=1/R_j$ 는 다이오드의 소신호 컨덕 턴스(dynamic conductance)라 한다.

I(V)의 2차 도함수는 다음과 같다.

$$\frac{d^{2}I}{dV^{2}}\Big|_{V_{0}} = \frac{dG_{d}}{dV}\Big|_{V_{0}} = \alpha^{2}I_{S}e^{\alpha V_{0}} = \alpha^{2}(I_{0} + I_{S}) = \alpha G_{d} = G_{d}^{'}$$

(3-5)

I(V)의 3차 도함수는 다음과 같다.

$$\left. \frac{d^3 I}{dV^3} \right|_{V_0} = \frac{dG'_d}{dV} \right|_{V_0} = \alpha^3 I_S e^{\alpha V_0} = \alpha^3 \left( I_0 + I_S \right) = \alpha^2 G_d = G''_d \tag{3-6}$$

따라서 식 3-3은 직류 바이어스 전류  $I_0$ 와 교류 전류 i의 합으로 다음과 같이 나타낼 수 있다.

$$I(V) = I_0 + i = I_0 + vG_d + \frac{v^2}{2}G_d' + \frac{v^3}{6}G_d'' + \cdots$$

(3-7)

식 3-7에서 다이오드 전류를 첫 네 항만 취할 때 이를 소신호 근사식이라 하며, 이 근사식은 대부분의 응용에 사용하기 적합하다. 소신호 근사식은 식 3-1의 직류 전압-전류 관계를 근거로 한 것으로, 다이오드의 등가 회로가 비선형 저항을 가짐을 나타낸다.

정류기에서 다이오드는 RF 입력신호의 일부를 직류 전력으로 변환하는데 사용된다. 다이오드 전압은 직류 바이어스 전압과 소신호 RF 전압으로 다음과 같이 표현할 수 있다.

$$V = V_0 + v_0 \cos \omega_0 t \tag{3-8}$$

식 3-7과 3-8로부터 다이오드의 출력 전류를 다음과 같이 나타낼 수 있다.

$$\begin{split} I(V) &= I_0 + v_0 G_d \cos \omega_0 t + \frac{v_0^2}{2} G_d^{'} \cos^2 \omega_0 t + \frac{v_0^3}{6} G_d^{''} \cos^3 \omega_0 t \\ &= I_0 + v_0 G_d \cos \omega_0 t + \frac{v_0^2}{2} G_d^{'} \left( \frac{1}{2} + \frac{1}{2} \cos 2\omega_0 t \right) + \frac{v_0^3}{6} G_d^{''} \left( \frac{3}{4} \cos \omega_0 t + \frac{1}{4} \cos 3\omega_0 t \right) \\ &= I_0 + \frac{v_0^2}{4} G_d^{'} + \left( v_0 G_d + \frac{v_0^3}{8} G_d^{''} \right) \cos \omega_0 t + \frac{v_0^2}{4} G_d^{'} \cos 2\omega_0 t + \frac{v_0^3}{24} G_d^{''} \cos 3\omega_0 t \quad (3-9) \end{split}$$

출력신호를 살펴보면 직류성분과 입력주파수 성분, 그리고 보다 고차인 고조파 성분이 동반됨을 확인할 수 있다.  $I_0$ 는 바이어스 전류이고  $v_0^2G_d^\prime/4$ 는 정류된 직류 전류이다. 그리고 다이오드 출력에는  $\omega_0$ 와  $2\omega_0$ ,  $3\omega_0$ 인 교류 신호도 포함되어 있으며, 이것은 간단한 저역통과 여파기로 제거할 수 있다. 다이오드의 비선형 전달 특성을 갖는 2단자 회로망의 비선형 주파수 응답 특성은 그림 3-2와 같다.

그림 3.2 1-tone 신호가 입력될 때 다이오드의 비선형 주파수 응답 특성.

Fig. 3.2 Nonlinear frequency response of diode for 1-tone signal input.

RF Energy Harvesting System에서 수전된 마이크로파는 직류 전압을 포함하지 않기 때문에 식 3-9에서 다이오드의 출력 직류 전류는 정류된 전류를 통해서만 얻을 수 있다. 고조파 전류성분이 부하에서 소비하는 전력은 최대한의 직류 전력만을 얻고자 하는 RF Energy Harvesting System에서 RF-DC 변환효율의 감소로 이어진다. 따라서 정류회로의 부하에서 발생하는 고조파 성분을

차단하여 직류전력으로 전환할 수 있다면 시스템 효율향상을 기대할 수 있다. 다음 절에서 이와 같은 문제를 해결하여 시스템의 효율을 향상시킨 예를 살펴 보고, 이를 응용하여 본 RF Energy Harvesting System에서 적용할 수 있는 방법을 모색한다.

#### 제 2 절 고조파 차단 회로망

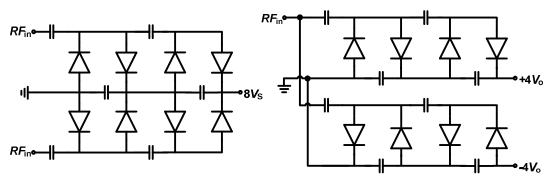

기존에 단일대역에서 고효율 전력증폭기를 설계하기 위해 트랜지스터의 고조파를 차단하는 개념을 이용한 E급 및 F급 전력증폭기 설계방법이 있으며 두회로 모두 고조파 차단을 위한 부하 회로망을 이용하였다. 전력증폭기에서 고조파 차단 부하 회로망을 효율 향상을 위해 어떻게 이용하였는지 살펴본다.

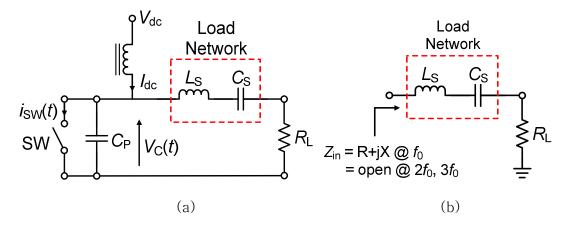

#### 3.2.1 E급 전력증폭기

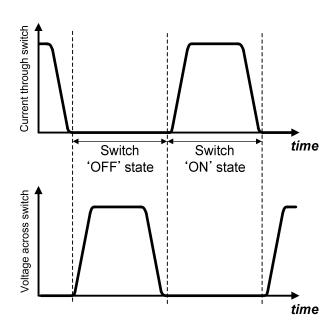

E급 전력증폭기는 스위치모드 증폭기로써 스위치 동작에 의해 트랜지스터에 인가되는 전압과 전류를 on/off 시킴으로써 고효율 특성을 얻을 수 있다. 그림 3.3(a)는 E급 전력증폭기의 이상적인 등가회로이다. 트랜지스터가 이상적인 스위칭 동작을 한다고 가정하면 스위치가 개방될 때 스위치에 흐르는 전류는 0이지만 큰 전압이 걸린다. 스위치가 단락될 때 전압은 0에 가깝지만 부하 커패시터에서 방전된 큰 전류가 흐른다. 이러한 스위칭 동작으로 트랜지스터의 소모 전력은 0에 가깝게 되며 이론적으로 100%의 전력 효율을 갖게 된다.

그림 3.3 (a) E급 전력증폭기의 기본 회로도와 (b) 고조파 차단을 위한 부하 회로망의 주파수에 따른 동작.

Fig. 3.3 (a) Basic Class—E power amplifier schematic and (b) operation of load network according to frequency for harmonic termination.

그림 3.4 고효율 특성을 위한 트랜지스터의 이상적인 전압과 전류 파형.

Fig. 3.4 Conceptual target waveform of transistor voltage and current.

그림 3.3에 고효율 특성을 얻기 위한 트랜지스터의 전압과 전류의 이상적인 파형이 제시되었다. 사실 E급 증폭기의 스위칭 동작에 의한 이상적인 전압과전류 파형을 만드는 역할을 하는 것이 부하 회로망이다. 그림 3.3(b)와 같이부하 회로망은 동작주파수의 신호 성분에 대해서는 임의의 임피던스로 정합할수 있도록 하여 최대 전력이 부하에 전달되도록 통과시키지만 스위칭 동작에의해 발생하는 고조파 성분들에 대해서는 큰 임피던스로 보이게 하여 신호를 반사한다. 부하 회로망이 고조파 신호의 발생을 억제하기 때문에 그림 3.4와같은 이상적인 전압과 전류 파형을 기대할 수 있다. 실제 부하 회로망을 구현할 때 모든 고조파 성분들을 조율하는 것은 불가능하기 때문에 대개 3차 고조파 성분까지만 제어할 수 있도록 설계한다.

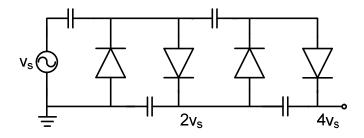

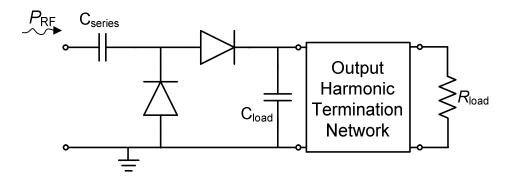

## 3.2.2 정류회로를 위한 고조파 차단 회로망

다이오드의 정류된 출력 직류 전류는 인가된 신호의 정수배 주파수에서 고조파 성분을 갖는다. F급 전력증폭기에 사용된 고조파 차단 회로망은 짝수 차수고조파에서 발생한 직류 성분만을 단락시켜 차단하기 때문에 정류작용을 하는 회로에는 적용할 수 없다. 하지만 E급 전력증폭기에 사용된 고조파 차단 회로 망은 동작주파수를 제외한 모든 고조파에서 개방 임피던스로 보이게 하여 출력 전류성분을 차단하기 때문에, RF Energy Harvesting System에서 입력단에는 E급 전력증폭기의 고조파 차단 회로망의 개념 자체를 이용하고 출력단에는 동작주파수 성분까지 차단하는 추가적인 고려가 이루어진 회로를 통해 정류회로

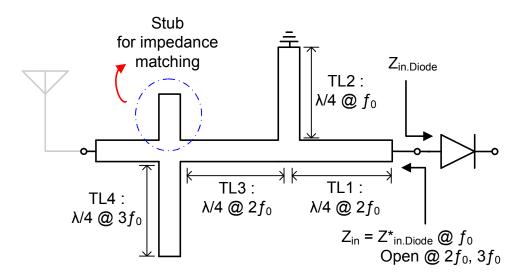

의 RF-DC 변환효율 향상에 크게 기여할 수 있을 것이다. 그림 3.7은 고조파차단 회로망을 적용한 렉테나의 회로도를 나타낸다. 입력단의 정합회로와 대역통과 필터를 대체하기 위하여 다이오드에서 방사되는 고조파 성분은 차단시키고 동작주파수 신호만을 통과시키는 고조파 차단회로망을 이용할 수 있다. 이회로는 입력단의 임피던스 정합 기능을 함께 하도록 설계할 수 있다. 또한 출력단에서 정류된 직류성분을 제외한 고조파 성분들이 부하로 전달되는 것을 막기 위해서 사용되는 고조파 차단 필터도 역시 고조파 차단 회로망을 이용하여간단한 구조를 통해 구현할 수 있다.

그림 3.5 고조파 차단 회로망을 이용한 RF Energy Harvesting System의 회로도.

Fig. 3.5 Block diagram of RF Energy Harvesting System using harmonic termination network.

## 제 3 절 새로운 고조파 차단 회로망의 제안

## 3.3.1 출력단 고조파 차단 회로망

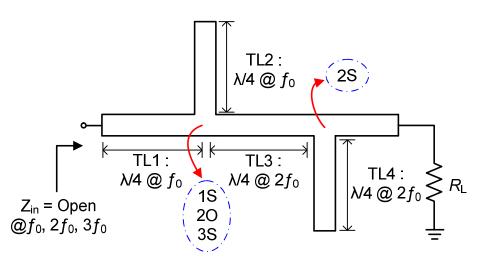

그림 3.6은 본 논문에서 제안한 RF-DC 정류회로의 출력단에서 사용할 수 있는 새로운 구조의 고조파 차단 회로망을 나타내고 있다. 출력단에서 사용할 고조파 차단 회로망은 부하에 고조파 신호가 넘어가는 것을 차단해야 하기 때문에 기본파와 2차 및 3차 고조파에서 정류기의 종단이 개방으로 보이도록 설계하였다. 모든 고조파 성분들을 차단하는 것은 현실적으로 어렵기 때문에 3차고조파까지 차단하도록 구현하였다.

이 회로망은 기본파, 2차 및 3차 고조파 성분을 제어하는 직렬 및 개방 전송 선로로 구성되어 있다. TL1과 TL2는 동작주파수 $(f_0)$ 에서  $\lambda/4$ 의 물리적 길 이를 가지며, TL3와 TL4는 2차 고조파 $(2f_0)$ 에서  $\lambda/4$ 의 물리적 길이를 갖는 다. 제안된 출력단 고조파 차단 회로망의 동작 원리는 각 고조파에 따라 다음 과 같이 설명할 수 있다.

먼저, 동작주파수 $(f_0)$ 에 대하여 회로를 해석하면 TL2는 개방 선로로 TL2의 접점에서 단락 임피던스(1S)로 변환되기 때문에 TL3 및 TL4, 그리고 부하  $(R_{\rm L})$ 에 관계없이 단락된 것처럼 보인다. 따라서  $f_0$ 에서는  $\lambda/4$ 길이의 전송 선로인 TL1의 입력단에서 개방 임피던스로 보인다.

2차 고조파 $(2f_0)$ 에 대해서 회로를 해석하면 개방 선로인 TL2는  $2f_0$ 에서  $\lambda/2$ 의 전기적 길이를 갖기 때문에 TL2의 접점에서 개방 임피던스(2O)로 보

여 회로에 아무런 영향을 주지 않는다. 개방 선로인 TL4는 TL3와의 접점에서 단락 임피던스(2S)로 변환되며 같은 길이인 TL3를 거치면 개방 임피던스 (2O)로 변환된다. TL1은  $2f_0$ 에서  $\lambda/2$ 의 길이를 갖기 때문에 전송선로 TL1의 입력단에서는 개방 임피던스로 보인다.

3차 고조파( $3f_0$ )에 대해서 회로를 해석하면 개방 선로인 TL2가  $3f_0$ 에서는  $3\lambda/4$ 의 전기적 길이를 갖기 때문에 TL1과의 접점에서 단락 임피던스(3S)로 변환되어, TL3 및 TL4 그리고 부하( $R_L$ )에 관계없이 단락된 것처럼 보인다. 따라서  $3f_0$ 에서는  $3\lambda/4$ 길이의 전송선로인 TL1의 입력단에서는 개방 임피던스 보인다.

회로의 해석을 통하여 2차, 3차 고조파 신호들뿐만 아니라 기본파 신호도 차단할 수 있다는 것을 확인할 수 있으며, 회로의 동작 원리는 그림 3.7을 통해쉽게 이해할 수 있다.

그림 3.6 출력단 고조파 차단 회로망의 회로도.

Fig. 3.6 Output harmonic termination network topology.

그림 3.7 주파수에 따른 출력단 고조파 차단 회로망의 동작.

Fig. 3.7 Operation of output harmonic termination network according to operating frequency.

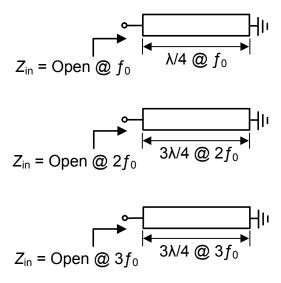

## 3.3.2 입력단 고조파 차단 회로망

그림 3.8은 본 논문에서 제안한 RF-DC 정류회로의 입력단에서 사용할 수 있는 새로운 구조의 고조파 차단 회로망을 나타내고 있다. 입력단에서 사용할 고조파 차단 회로망은 다이오드의 비선형 동작으로 인해서 발생되는 고조파 성분이 안테나로 재방사되는 것을 막기 위해서 사용되며, 동작주파수 성분은 통과시키고 2차 및 3차 고조파 성분만 차단하도록 설계되어야 한다. 이 회로망은 각 고조파 성분을 제어하는 직렬 및 개방/접지 전송선로로 구성되어 있다. TL1과 TL3는 2차 고조파( $2f_0$ )에서  $\lambda/4$ , TL2는 동작주파수에서  $\lambda/4$ , TL4는 3차 고조파( $3f_0$ )에서  $\lambda/4$ 의 물리적 길이를 각각 갖는다.

그림 3.8 입력단 고조파 차단 회로망의 회로도.

Fig. 3.8 Input harmonic termination network topology.

그림 3.9 주파수에 따른 입력단 고조파 차단 회로망의 동작.

Fig. 3.9 Operation of input harmonic termination network according to operating frequency.

제안한 입력단 고조파 차단 회로망의 동작원리는 각 고조파에 따라 다음과 같이 설명할 수 있다.

먼저, 동작주파수( $f_0$ )에 대하여 회로를 해석하면 TL2는 단락선로로 TL1과의 접점에서 개방 임피던스로 변환되기 때문에 이 전송선로는 회로에 아무런영향을 주지 않는다.  $f_0$ 에서 TL1과 TL3의 전기적 길이 합은  $\lambda/4$ 길이를 가지며, TL4 전송선로가 용량성(capacitive) 리액턴스를 제공한다. 따라서  $\lambda/4$ 길이를 가지는 TL1과 TL3를 이용하여 임피던스의 실수성분 정합이 가능하고,임피던스의 허수성분 정합은 간단한 회로를 추가하여 할 수 있다.

2차 고조파( $2f_0$ )에 대해서 회로를 해석하면 단락선로인 TL2는  $2f_0$ 에서  $\lambda/2$ 의 물리적 길이를 갖기 때문에 TL1과의 접점에서 단락 임피던스(2S)로 보여 전송선로 TL3, TL4 그리고 다른 정합회로에 관계없이 단락된 것처럼 보인다. 따라서  $2f_0$ 에서는  $\lambda/4$ 길이의 전송 선로 TL1를 거치면 회로의 입력에서는 개방 임피던스(2O)로 보인다.

3차 고조파( $3f_0$ )에 대해서 회로를 해석하면 단락선로인 TL2가  $3f_0$ 에서는  $3\lambda/4$ 의 길이를 갖기 때문에 TL2의 접점에서 개방 임피던스로 변환되어 TL2는 회로에 아무런 영향을 주지 않는다.  $3f_0$ 에서  $\lambda/4$ 길이를 갖는 개방선로인 TL4는 TL3와의 접점에서 단락 임피던스(3S)로 변환되고,  $3f_0$ 에서  $3\lambda/4$ 의 길이를 갖는 선로인 TL1과 TL3를 통과하면 회로의 입력에서 개방 임피던스(3O)로 보인다.

위와 같이 회로의 해석을 통하여 2차와 3차 고조파는 차단하고 동작주파수 성분은 통과하도록 동작한다는 것을 알 수 있으며, 회로의 동작 원리는 그림 3.9를 통해 쉽게 이해할 수 있다.

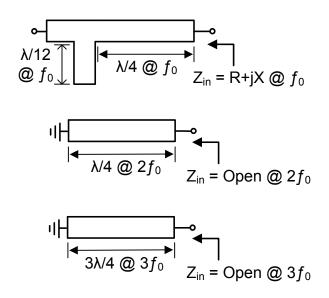

## 3.3.3 입력 임피던스 정합회로

안테나와 정류회로 간의 임피던스 정합은 렉테나에서 RF-DC 변환효율에 영향을 미치는 큰 요소 중 하나이다. 그림 3.8에서와 같이 일반적으로 안테나와 정류회로 사이에서 다이오드로부터 발생하는 비선형 성분의 재방사를 막기 위해 사용하는 대역통과 필터에 종단 임피던스를 각각 안테나와 정류회로의 입력임피던스로 하여 정합을 한다. 하지만 필터의 종단 임피던스가 50 Ω이 아닌임의의 임피던스로 선택되면 필터 설계가 복잡해지는 문제가 있다.

그림 3.10 입력단 고조파 차단 회로망에 스터브를 이용한 임피던스 정합.

Fig. 3.10 Impedance matching method using additional stub in input harmonic termination network.

RF-DC 정류회로의 입력단에 사용하도록 제안된 구조인 고조파 차단 회로망

에 간단히 스터브를 삽입하여 임피던스 정합을 할 수 있다. 그림 3.10은 스터브를 이용 한 입력 임피던스 정합을 보여준다. 이 때 상황에 따라 개방 스터브나 단락 스터브를 선택적으로 선택할 수 있다.

다음 장에서는 시뮬레이션을 통하여 제안된 구조가 의도한대로 동작할 수 있는지를 살펴본다.

# 제 4 장 제안된 고조파 차단 회로망의 시뮬레이션

## 제 1 절 출력단 고조파 차단 회로망

전력증폭기에 사용되는 고조파 차단 부하 회로망은 동작주파수 성분은 통과시키지만 2차와 3차 고조파 성분은 차단하여 전력효율을 향상시키고자 하였다. RF-DC 정류회로 설계에 사용된 출력단 고조파 차단 회로망은 전력증폭기에서와는 새로운 구조로 2차와 3차 고조파 성분뿐만 아니라 동작주파수 성분도차단하여 순수 직류 성분만을 얻고자 하였다.

앞장에서 제안한 새로운 구조의 고조파 차단 회로망이 실제로도 구현 가능한 지 여부를 판단하기 위하여 시뮬레이션을 통해 확인하였다. 그림 4.1은 Agilent사의 ADS2009를 이용하여 전송선로 조합으로 회로를 구현한 것이다.

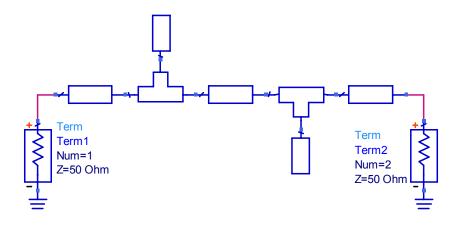

그림 4.1 ADS에서 구현한 출력단 고조파 차단 회로망의 회로도.

Fig. 4.1 Schematic of output harmonic termination network in ADS.

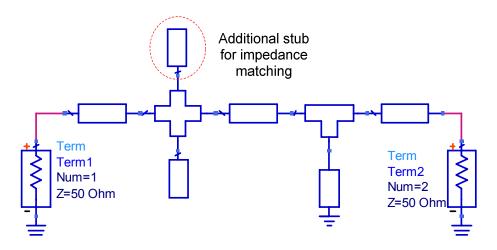

그림 4.2 출력단 고조파 차단 회로망의 ADS 회로 시뮬레이션 결과

(a) S21 특성, (b) 스미스 차트상에서의 S11 특성.

Fig. 4.2 Simulation results of output harmonic termination network in ADS

(a) S21 characteristic, (b) S11 characteristic on smith chart.

그림 4.2(a)는 출력단 고조파 차단 회로망의 통과 특성이며 1차, 2차 및 3차주파수에서 S21이 모두 -37 dB 이상을 나타내어 고조파 성분을 통과시키지 않는다는 것을 알 수 있다. 그림 4.2(b)는 스미스 차트 상에서 반사계수 특성을 나타내며 세 주파수에서 모두 개방 임피던스 점 근처에 모여 있는 것으로 보아 고조파 성분이 모두 반사될 것이라 예상할 수 있다.

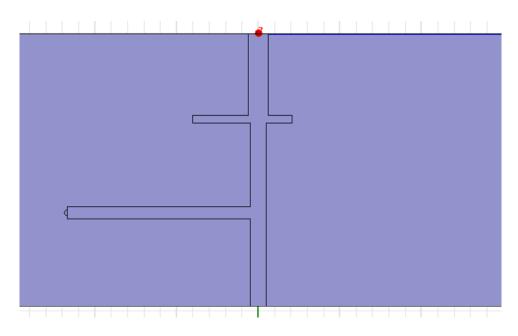

실제 환경에서도 동일한 결과가 나오는지 확인하기 위하여 Ansoft사의 HFSS11을 이용하여 EM시뮬레이션을 하였다. 그림 4.3과 같이 회로를 구현한 후 앞서 살펴본 것과 마찬가지로 S파라미터 특성을 살펴보았다.

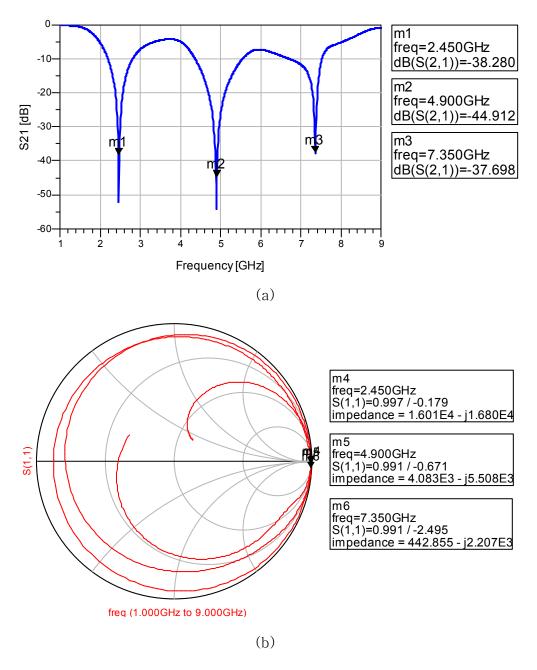

그림 4.3 HFSS에서 구현한 출력단 고조파 차단 회로망의 회로도.

Fig. 4.3 Schematic of output harmonic termination network in HFSS.

그림 4.4 출력단 고조파 차단 회로망의 EM시뮬레이션 결과

(a) S21 특성, (b) 스미스 차트상에서의 S11 특성.

Fig. 4.4 EM simulation results of output harmonic termination network

(a) S21 characteristic, (b) S11 characteristic on smith chart.

EM시뮬레이션 결과 역시 ADS 회로 시뮬레이션과 비슷한 통과대역 특성과 반사계수 특성을 나타냈다. 이로써 제안한 고조파 차단회로망이 렉테나의 출력 단에서 고조파 차단 필터를 대신할 수 있음을 보인 것으로 이론과 같이 실제로 도 구현 가능함을 확인할 수 있다.

## 제 2 절 입력단 고조파 차단 회로망

렉테나의 입력단에 사용되는 고조파 차단 회로망은 기존의 대역통과 필터를 대신하여 동작주파수 성분은 통과시키고 2차와 3차 고조파 성분은 차단하도록 고안된 새로운 구조이다. 또한 이 회로를 이용하여 입력 임피던스 정합도 할수 있어야 한다. 새롭게 제안된 이 구조가 실제로도 구현 가능한지 여부를 판단하기 위하여 Agilent사의 ADS2009를 이용하여 시뮬레이션 하였다.

그림 4.5 ADS에서 구현한 입력단 고조파 차단 회로망의 회로도.

Fig. 4.5 Schematic of input harmonic termination network in ADS.

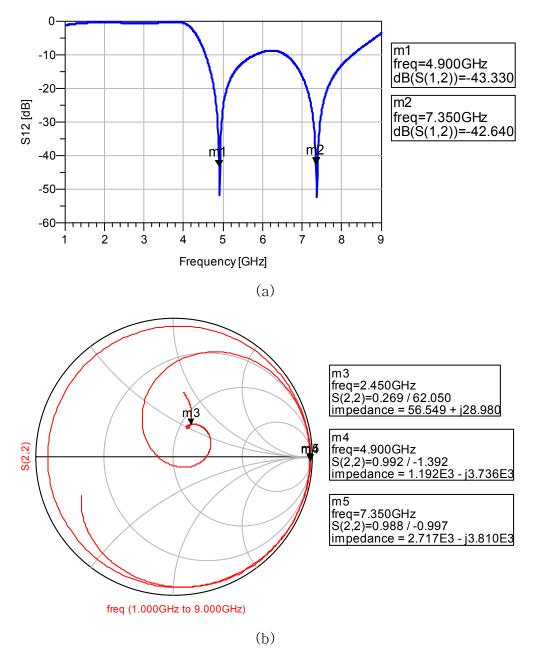

그림 4.6 입력단 고조파 차단 회로망의 ADS 회로 시뮬레이션 결과

(a) S12 특성, (b) 스미스 차트상에서의 S22 특성.

Fig. 4.6 Simulation results of input harmonic termination network in ADS

(a) S12 characteristic, (b) S22 characteristic on smith chart.

그림 4.5는 입력단 고조파 차단 회로망의 구조이며, 임피던스 정합을 하기 위하여 개방 스터브에 병렬로 개방 스터브를 추가하였다. 주어진 임피던스에 따라 개방 및 단락 스터브를 추가할 수 있다.

그림 4.6(a)는 입력단 고조파 차단 회로망의 통과 특성이며 2차와 3차 고조파에서만 재방사되어 나가는 성분을 차단할 수 있음을 확인할 수 있다. 전송선로로 구현된 이 회로에서 S21특성은 S12특성과 같기 때문에 동작주파수에서는 신호가 통과하도록 설계되었다. 그림 4.6(b)는 스미스 차트상에서 반사계수특성을 나타내며 2차와 3차 고조파에서 개방 임피던스 점 근처에 모여 있고해당 고조파 성분이 모두 반사될 것이라 예상할 수 있다. 동작주파수에서는 임의의 임피던스를 나타내어 입력 임피던스 정합을 가능하도록 하였다.

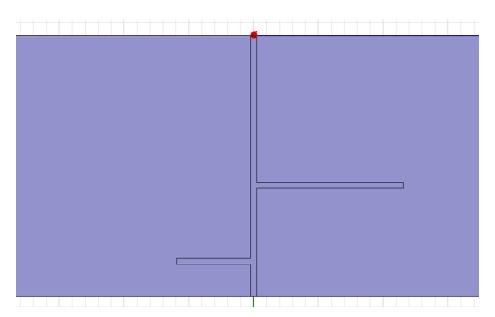

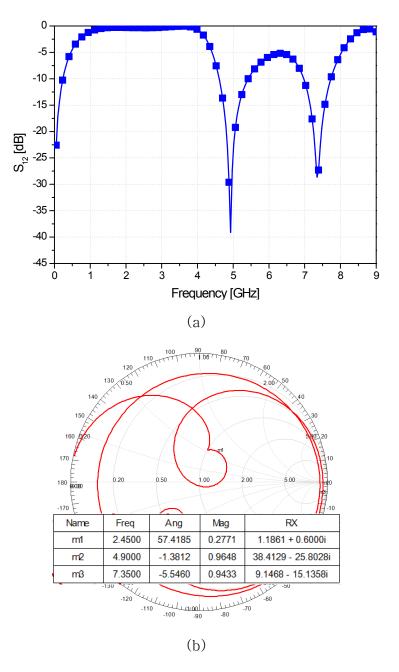

그림 4.7 HFSS에서 구현한 입력단 고조파 차단 회로망의 회로도.

Fig. 4.7 Schematic of input harmonic termination network in HFSS.

그림 4.8 입력단 고조파 차단 회로망의 EM시뮬레이션 결과 (a) S12 특성, (b) 스미스 차트상에서의 S22 특성.

Fig. 4.8 EM simulation results of output harmonic termination network

(a) S12 characteristic, (b) S22 characteristic on smith chart.

입력단 고조파 차단 회로망도 EM시뮬레이션을 통하여 S파라미터 특성을 확인하였다. 임피던스 정합을 위한 스터브가 추가된 상태에서 ADS 회로 시뮬레이션과 유사한 결과를 얻을 수 있었다. 이런 특성은 렉테나의 입력단에서 임피던스 정합 기능을 갖는 대역통과 필터를 대신할 수 있음을 보인 것으로 역시이론과 같이 실제로도 구현 가능함을 확인할 수 있다.

## 제 3 절 정류회로의 설계

렉테나에서 정류 작용을 하는 Villard 전압 체배기의 비선형 동작을 시뮬레이션을 통해 확인하고 제안된 고조파 차단회로망을 적용했을 때의 효과를 살펴본다.

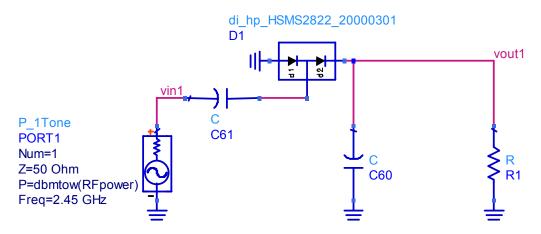

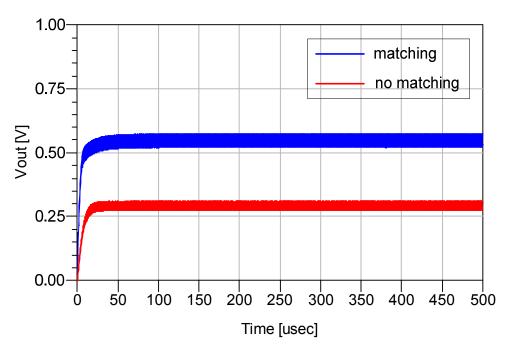

그림 4.9는 ADS상에서 구현한 Villard 전압 체배기의 회로도이다. 쇼트키 다이오드인 HSMS2822을 모델링한 소자와 22pF의 용량을 갖는 커패시터, 1k 의 지항을 이용해 구성하였다. 먼저 입력 임피던스 정합의 영향을 알아보기 위하여 정합 전과 후의 출력 직류 전압을 transient 시뮬레이션을 통해 비교하였다. 이때 입력 RF 전력은 0 dBm 이며 그림 4.10을 통해 결과를 확인할 수 있다. 결과를 통해 정합이 되지 않은 회로는 입력 신호의 상당 부분이 반사되기때문에 임피던스 정합된 회로보다 출력 직류 전압이 작을 것이라는 것을 쉽게예측할 수 있다. 따라서 RF-DC 변환효율 향상을 위해 안테나와 정류회로 사이에서 임피던스 정합은 필수적이다.

그림 4.9 HSMS2822을 이용하여 구현한 Villard 전압 체배기 회로도.

Fig. 4.9 Schematic of Villard voltage multiplier using HSMS2822 in ADS.

그림 4.10 입력 임피던스 정합 전과 후의 출력 직류 전압 비교.

Fig. 4.10 Comparison of output DC voltage before and after input impedance matching in rectenna.

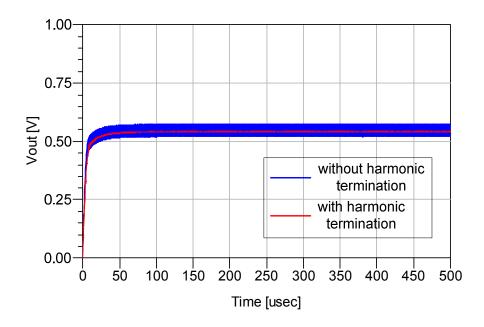

다음은 출력단의 고조파 차단 회로망이 렉테나의 특성에 미치는 영향을 확인하기 위하여 출력단 고조파 차단 회로망을 사용하기 전과 후의 출력 직류 전압을 비교하였다. 그림 4.11을 살펴보면, 출력단에 고조파 차단 회로망을 사용했을 때, 출력 직류 전압에 존재했던 상당한 리플이 제거된 것을 확인할 수 있다. 직류 전압의 리플은 RF-DC 변환효율뿐만 아니라 부하 회로로 사용될 수 있는 전력관리 회로나 배터리 등의 동작에 나쁜 영향을 미치기 때문에 적을 수록좋다.

그림 4.11 출력단 고조파 차단 회로망 사용전과 후의 출력 직류전압 특성.

Fig. 4.11 Comparison of output DC voltage with and without output harmonic termination network.

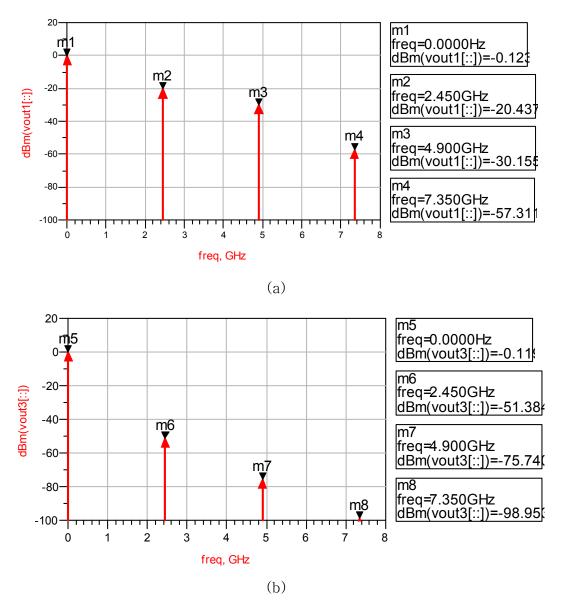

그림 4.12 출력단의 고조파 차단 회로망 사용전과 후의 출력 전력에 대한 Harmonic Balance 시뮬레이션 결과.

Fig. 4.12 Harmonic Balance simulation results for output DC power with and without output harmonic termination network.

출력단 고조파 차단 회로망의 효과는 주파수 상에서 고조파 성분들의 전력레벨의 비교를 통해서도 확인할 수 있다. 그림 4.12는 출력단 고조파 차단 회로 망을 사용하기 전과 후의 Harmonic Balance 시뮬레이션 결과이다. 직류성분을 제외한 고조파 성분의 전력레벨이 출력단 고조파 차단 회로망을 사용한 후에 크게 줄어든 것을 확인할 수 있다. 이것은 출력 직류전압의 리플이 감소된 그림 4.11의 결과에도 부합한다. 또한 직류 전력레벨이 소량 증가한 것을 확인할수 있다. 이 결과를 통해 감소된 고조파 성분들은 직류 전력으로 재변환되어 렉테나의 효율을 향상시킨다는 것을 알 수 있다.

# 제 5 장 제작 및 측정

4장에서 설계한 입·출력단 고조파 차단 회로망을 PCB로 제작하여 실제 동작을 측정한다. 회로 제작에 이용되는 기판은 Rogers사의 RT/Duroid-5880이며, 2.2의 유전율( $\varepsilon_r$ ), 31 mil의 유전체 높이(h) 그리고 1 Oz 의 동판 두께(t)를 갖는다.

## 제 1 절 출력단 고조파 차단 회로망

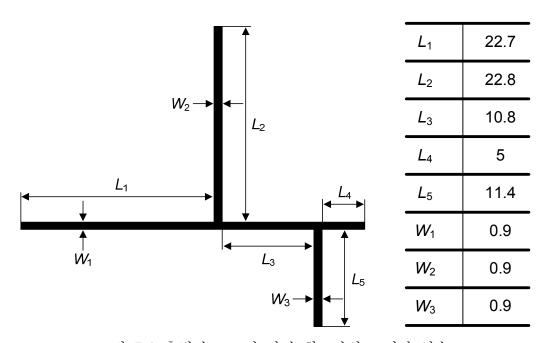

그림 5.1 출력단 고조파 차단 회로망의 도면과 치수.

Fig. 5.1 Layout and size of output harmonic termination network.

그림 5.1은 앞장에서 EM시뮬레이션을 통해 최적화된 특성을 갖는 회로의 모양과 치수이다. 그림 5.2와 같이 PCB로 제작하여 측정하였으며, 측정한 결과는 EM시뮬레이션 결과와 비교하여 그림 5.3에 제시하였다. 측정을 위해 Agilent사의 Network Analyzer 8720D가 사용되었다.

그림 5.2 제작된 고조파 차단 회로망의 사진.

Fig. 5.2 Photograph of the fabricated output harmonic termination network.

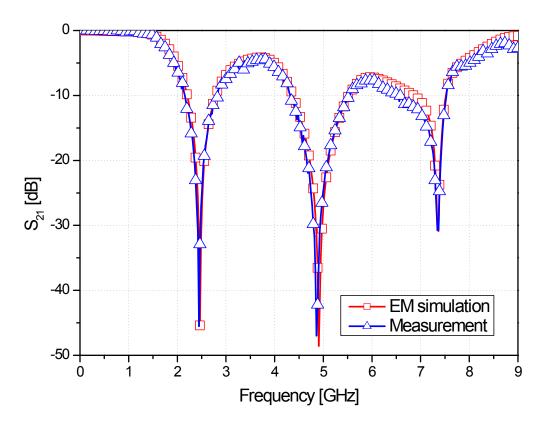

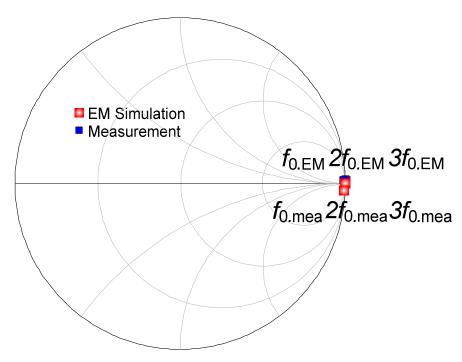

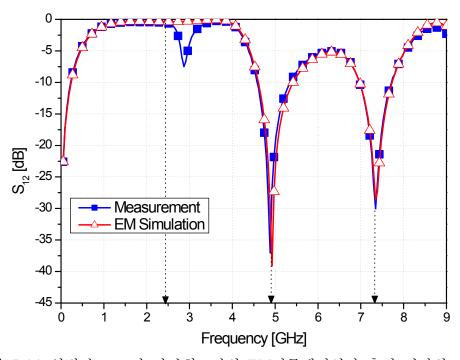

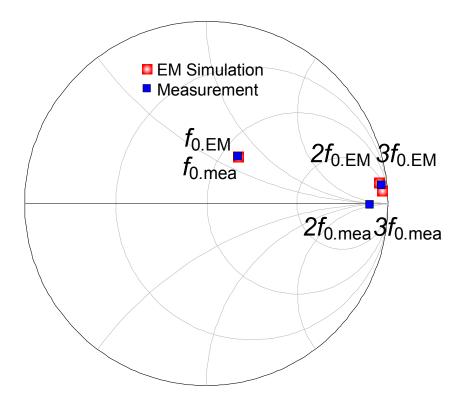

측정결과는 기본파와 2차 및 3차 고조파 성분이 통과하지 못하도록 각 고조파에서 30 dB 이상의 감쇠 특성이 나타나며 EM시뮬레이션 결과와 거의 일치한다. 그림 5.4에 스미스 차트상에서 반사계수 특성 역시 EM시뮬레이션과 측정결과를 비교하여 나타내었으며, 세 주파수에서의 임피던스가 모두 개방 지점에 모여 있는 것을 알 수 있다. 제작된 출력단 고조파 차단 회로망은 설계한대로 동작하는 것을 확인할 수 있다.

그림 5.3 출력단 고조파 차단 회로망의 EM시뮬레이션과 측정 결과의 비교.

Fig. 5.3 Comparison between EM simulation and measurement result of output harmonic termination network.

그림 5.4 출력단 고조파 차단 회로망의 반사계수 특성.

Fig. 5.4 Reflection coefficient characteristics of output harmonic termination network on Smith chart.

## 제 2 절 부하저항 및 커패시터 최적화

일반적으로 부하저항 값이 크면 출력전압 역시 커지지만 이것이 효율의 증가를 의미하는 것은 아니다. 렉테나의 RF-DC 변환효율을 계산할 때 사용하는 식 2-1은 높은 효율을 얻기 위해 적절한 부하저항 값의 선택을 요구한다. 이를 위해 최적의 부하저항 및 커패시터 값을 이용하여 Villard 전압 체배기를 구성하는 작업을 하였다.

그림 5.5는 부하저항을 최적화하기 위한 실험에 이용된 회로도이다. 이때

Villard 전압 체배기를 구성하는 두 커패시터는 22 pF을 사용했으며 부하저항이 바뀌는 모든 경우에 회로에 영향을 주는 요소를 없애기 위해 입력 임피던스정합은 하지 않았다. 입력 RF 전력은 10 dBm을 사용했다.

그림 5.5 부하저항 최적화를 위해 사용된 회로.

Fig. 5.5 Schematic of circuit used to find optimal load resistance.

그림 5.6은 일정한 범위 내에서 표준저항 값을 사용하여 부하저항을 변화시켰을 때 그림 5.5의 회로에서 얻을 수 있는 효율을 나타내는 것으로,  $1 \text{ k}\Omega$  까지는 효율이 지속적으로 증가하다가  $1.1 \text{ k}\Omega$  부터는 등락하며 감소하는 불안정한모습을 보여주었다. 이를 통해 안정적으로 상승하는 구간 내에서 가장 높은 효율을 얻을 수 있었던  $1 \text{ k}\Omega$ 의 저항을 최적의 부하저항으로 선택하였다. 이 결과는 높은 출력전압이 높은 효율을 의미하는 것이 아님을 알 수 있다.

다음은 Villard 전압 체배기를 구성하는 직렬 커패시턴스의 최적화된 값을 실험을 통해 구하였다. 부하저항과 입력전력은 각각 1 k $\Omega$  과 10 dBm으로 고정하고 high-Q 커패시터를 이용하였다. 커패시턴스에 따른 출력전압은 그림 5.7

과 같다. 부하저항이 고정된 상태에서는 출력전압이 높을수록 효율도 높기 때문에 실험에 의해 직렬 커패시터로 68 pF의 값을 선택하였다.

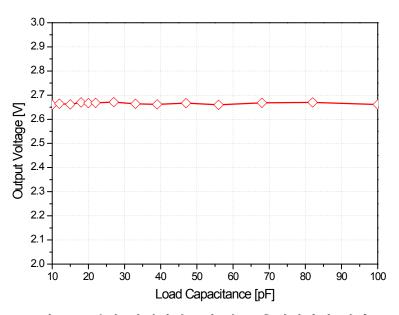

마지막으로 부하저항과 직렬 커패시터, 입력 전력레벨을 고정한 상태에서 최적의 부하 커패시턴스를 찾기 위한 실험을 하였다. 그림 5.8과 같이 부하 커패시턴스에 상관없이 일정한 출력전압을 얻을 수 있었으며, 앞으로의 실험에서 22 pF의 값을 부하 커패시턴스로 사용하였다.

회로를 구성하는 소자 값을 시뮬레이션이 아닌 실험을 통해 찾은 이유는 실험에 사용된 다이오드의 비선형 시뮬레이션 데이터가 제공되지 않기 때문이다.

그림 5.6 부하저항 값에 따른 RF-DC 변환효율의 변화.

Fig. 5.6 Variation of RF-DC conversion efficiency according to load resistance.

그림 5.7 직렬 커패시턴스에 따른 출력전압의 변화.

Fig. 5.7 Variation of output voltage according to series capacitance.

그림 5.8 부하 커패시턴스에 따른 출력전압의 변화.

Fig. 5.8 Variation of output voltage according to load capacitance.

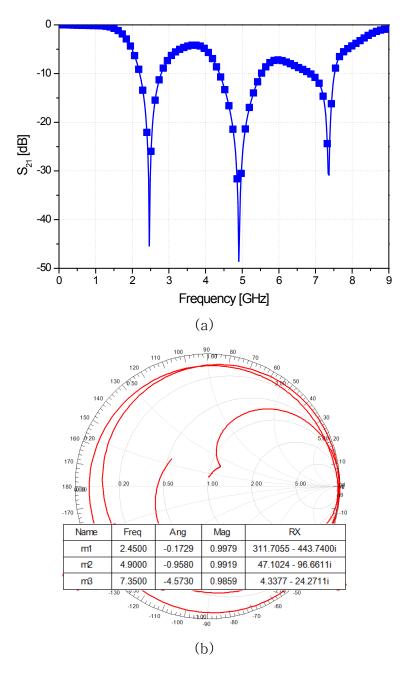

## 제 3 절 입력단 고조파 차단 회로망

앞절에서 설계한 출력단 고조파 차단 회로망과 Villard 전압 체배기를 연결하고 이 회로를 들여다본 임피던스를 입력단 고조파 차단 회로망을 이용하여 안테나와 정합할 수 있다. 그림 5.9는 임피던스 정합을 위해 스터브가 추가된 입력단 고조파 차단회로망의 도면과 치수를 나타낸다. EM 시뮬레이션을 통해 최적화된 특성을 갖는 회로를 그림 5.10과 같이 PCB로 제작하였다. 그림 5.11의 측정결과를 통해 2차와 3차 고조파는 차단시키지만 기본파는 통과하도록 동작하는 것을 알 수 있으며 이는 EM 시뮬레이션 결과와도 거의 일치한다.

그림 5.9 입력단 고조파 차단 회로망의 도면과 치수.

Fig. 5.9 Layout and size of input harmonic termination network.

그림 5.10 제작된 입력단 고조파 차단 회로망의 사진.

Fig. 5.10 Photograph of the fabricated input harmonic termination network.

그림 5.11 입력단 고조파 차단회로망의 EM시뮬레이션과 측정 결과의 비교.

Fig. 5.11 Comparison between EM simulation and measurement result of input harmonic termination network.

그림 5.12 입력단 고조파 차단회로망의 반사계수 특성.

Fig. 5.12 Reflection coefficient characteristics of input harmonic termination network on Smith chart.

## 표 5.1 입력단 고조파 차단 회로망과 다이오드의 입력 임피던스 정합점.

Table 5.1 Input impedance matching point of input harmonic termination network and diode.

| Z <sub>in.Diode</sub>                                                 | 58.404 - j 30.041 Ω |  |

|-----------------------------------------------------------------------|---------------------|--|

| $Z_{\text{in.EM}}$ (= $Z^*_{\text{in.Diode}}$ ) in HTN <sub>in</sub>  | 58.070 + j 29.550 Ω |  |

| $Z_{\text{in.PCB}}$ (= $Z^*_{\text{in.Diode}}$ ) in HTN <sub>in</sub> | 58.766 + j 30.090 Ω |  |

그림 5.12의 스미스 차트상에서 반사계수 특성을 살펴보면, 2차와 3차 고조파에서는 개방 임피던스 근처에 위치하고 동작주파수에서는 임의의 임피던스 정합점에 위치하는 것을 알 수 있다. 이 임피던스 정합점은 출력단 고조파 차단회로와 Villard 전압 체배기를 연결한 회로를 들여다본 임피던스( $Z_{\rm in,Diode}$ )로써 입력단 고조파 차단회로가 다이오드에 연결되는 부분을 들여다본 임피던스( $Z_{\rm in,EM}$  또는  $Z_{\rm in,PCB}$ )가  $Z_{\rm in,Diode}$ 에 켤레복소수를 가져야 한다. 표 5.1은  $Z_{\rm in,EM}$ 과  $Z_{\rm in,PCB}$ 가 거의 일치하며  $Z_{\rm in,Diode}$ 에 켤레복소수임을 확인할 수 있다. 이를 통해 제작된 입력단 고조파 차단회로가 필터로써의 기능과 정합회로로써의 역할을 모두 수행할 수 있음이 확인되었다.

지금까지의 측정 결과를 통해 입력단 고조파 차단회로망 역시 설계한대로 특성을 얻을 수 있다는 것을 알 수 있다.

## 제 4 절 RF-DC 정류회로의 출력 특성

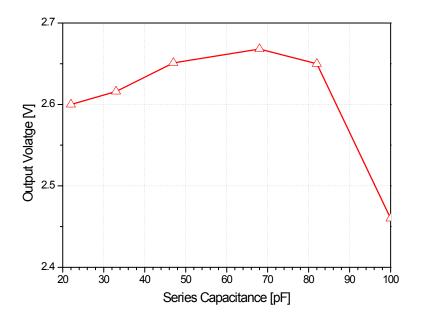

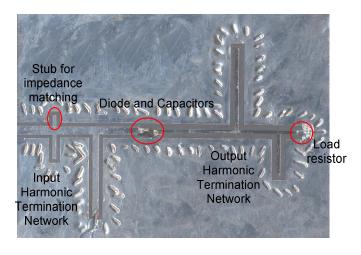

본 논문에서 새롭게 고안된 고조파 차단 회로망을 적용하여 RF-DC 정류회로를 그림 5.13과 같이 제작하였다. 다이오드와 커패시터로 구성된 정류기를 중심으로 입·출력 고조파 차단회로가 연결되어 있다. 입력단에는 안테나의 임피던스를  $50 \Omega$ 으로 가정하고 정합이 이루어졌다. 회로의 크기는 80mm X 55mm 이다. 안테나 대신 HP사의 Signal Generator E4432B를 이용하여 회로에 전력을 직접 인가하였다.

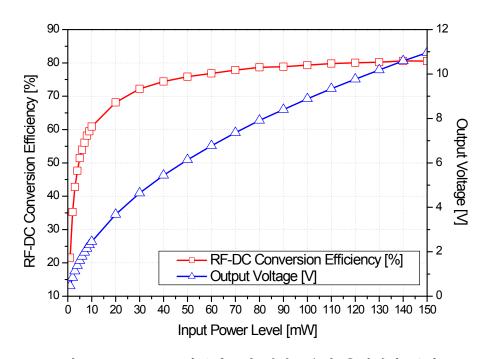

그림 5.14는 완성된 회로에 대한 효율과 출력전압 특성이 나타나 있다. RF-

그림 5.13 완성된 RF-DC 정류회로의 사진.

Fig. 5.13 Photograph of the fabricated RF-DC conversion circuit.

그림 5.14 RF-DC 정류회로의 변환효율과 출력전압 특성.

Fig. 5.14 Characteristics of efficiency and output voltage of RF-DC conversion circuit.

## 표 5.2 RF-DC 정류회로의 변환효율과 출력전압 특성.

Table 5.2 Characteristics of efficiency and output voltage of RF-DC conversion circuit.

| P <sub>in</sub> [mW] | V <sub>out</sub> [V] | P <sub>out</sub> [mW] | Efficiency [%] |

|----------------------|----------------------|-----------------------|----------------|

| 1                    | 0.473                | 0.225                 | 22.5079        |

| 2                    | 0.844                | 0.717                 | 35.8318        |

| 3                    | 1.132                | 1.289                 | 42.972         |

| 4                    | 1.379                | 1.913                 | 47.8280        |

| 5                    | 1.595                | 2.559                 | 51.1876        |

| 6                    | 1.795                | 3.241                 | 54.0246        |

| 7                    | 1.980                | 3.944                 | 56.3438        |

| 8                    | 2.151                | 4.654                 | 58.1841        |

| 9                    | 2.308                | 5.359                 | 59.5446        |

| 10                   | 2.46                 | 6.088                 | 60.8813        |

| 20                   | 3.68                 | 13.624                | 68.1207        |

| 30                   | 4.64                 | 21.659                | 72.1985        |

| 40                   | 5.44                 | 29.772                | 74.4306        |

| 50                   | 6.14                 | 37.927                | 75.8543        |

| 60                   | 6.77                 | 46.110                | 76.8493        |

| 70                   | 7.36                 | 54.497                | 77.8523        |

| 80                   | 7.91                 | 62.946                | 78.6822        |

| 90                   | 8.40                 | 70.986                | 78.8732        |

| 100                  | 8.88                 | 79.330                | 79.3304        |

| 110                  | 9.34                 | 87.762                | 79.7838        |

| 120                  | 9.77                 | 96.029                | 80.0242        |

| 130                  | 10.18                | 104.258               | 80.1984        |

| 140                  | 10.59                | 112.825               | 80.5893        |

| 150                  | 10.96                | 120.847               | 80.5645        |

|                      | •                    | •                     | •              |

DC 정류회로에 최대 150 mW 범위에서 전력을 인가하였다. 출력전압은 계속해서 선형적으로 증가하지만 RF-DC 변환효율은 약 30 mW 부근에서 포화되기 시작하여 140 mW에서 최대 80.59 %를 나타냈다. 이때 출력 직류전압은 10.59 V 로 측정되었다. 150 mW 부터는 효율이 줄어들기 시작했다. 본 실험에서 제작된 회로를 이용하여 얻은 효율은 기존 연구에서 얻을 수 있는 효율의최대치와 비슷하며, 이는 새로운 이론이 기존 회로를 대체해서 사용할 수 있음을 나타낸다.

그림 5.15 고조파 차단회로 사용에 따른 RF-DC 변환효율 비교.

Fig. 5.15 Comparison of RF-DC conversion efficiency in case of with and without harmonic termination network.

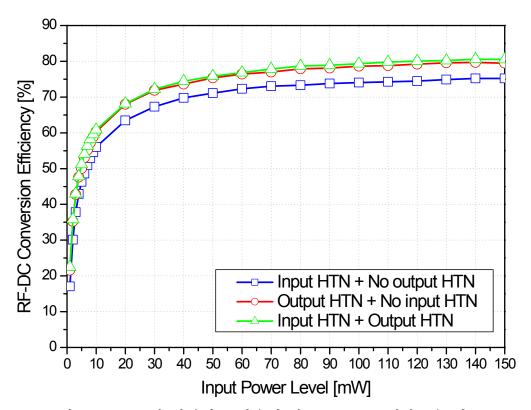

그림 5.15는 새롭게 제안된 입·출력 고조파 차단 회로망을 적용한 회로와 입력단이나 출력단에만 제안된 회로를 적용했을 때 RF-DC 변환효율의 차이를 비교한 그림이다. 고조파 차단회로를 입력단에만 사용했을 때는 입·출력단모두에 회로를 사용했을 때와 5 % 가량의 효율 차이를 보였다. 이는 출력단에서 발생하는 고조파 성분이 전력을 상당부분 소비한다는 것을 의미하며 고조파차단의 효과로 5% 가량의 효율 향상을 기대할 수 있다. 출력단에만 고조파차단의 효과로 5% 가량의 효율 향상을 기대할 수 있다. 출력단에만 고조파차단 회로망을 사용했을 때는 1% 범위 내에서 큰 차이를 보이지 않았다. 그 이유는 입력단에서 차단하는 고조파 성분이 2차, 3차 뿐이며 재방사되는 전력레벨이 상대적으로 작기 때문이다. 이 결과는 입력단 고조파차단 회로망을 이용하여 임피던스 정합이 가능하다는 것을 증명한다고 할 수 있다.

표 5.3은 렉테나에 관한 이전 연구들의 측정요약 및 성능비교를 나타낸다. ISM 대역인 2.45 GHz 또는 5.8 GHz에서 동작하도록 구현된 RF-DC 정류회로는 다이오드의 다양한 조합으로 구성되었다. 이 회로들의 RF-DC 변환효율은 58 ~ 82 % 의 범위에 있다. 이전 연구결과들과 비교를 통해, 본 논문에서 제안한 구조의 측정결과는 기존의 구조를 대체할 수 있을 만큼 뛰어나다는 것을 알 수 있다.

## 표 5.3 렉테나에 관한 이전 연구들의 측정요약 및 성능 비교.

Table 5.3 Measurement summary and performance comparison among previous researches for the rectenna.

| Reference | Rectifier structure           | Maximum<br>RF-DC<br>conversion<br>efficiency [%] | Operating frequency [GHz] |

|-----------|-------------------------------|--------------------------------------------------|---------------------------|

| [21]      | Single shunt                  | 82                                               | 5.8                       |

| [28]      | Single series                 | 75                                               | 2.45                      |

| [29]      | Single shunt                  | 81                                               | 5.71                      |

| [30]      | Dual series-<br>antiparallel  | 76                                               | 5.8                       |

| [31]      | Single series                 | 65.87                                            | 5.8                       |

| [32]      | Single series                 | 70.7                                             | 5.8                       |

| [33]      | Dual series –<br>antiparallel | 58                                               | 2.45                      |

| [34]      | 4 diodes -<br>antiparallel    | 61                                               | 2.45                      |

| This work | Villard multiplier            | 80.59                                            | 2.45                      |

# 제 6 장. 결 론

무선 전력 전송분야에서 대기중의 RF 신호를 받아 직류전원으로 변환시켜 회로를 구동하는 기술인 RF Energy Harvesting System에서 임피던스 정합과함께 다이오드의 비선형 특성과 문턱전압 효과는 효율에 절대적인 영향을 미친다. 문턱전압 효과는 쇼트키 다이오드를 이용하여 극복할 수 있지만, 비선형 특성을 극복하는 것은 기존 연구에서 제시된 방법으로는 한계가 있다. RF 전력을 직류 전력으로 변환하는 과정에서 고조과 발생으로 분산되는 전력을 차단하기위하여 기존과 같이 렉테나의 입·출력단에 필터를 사용한다면, 필터의 삽입손실 등으로 오히려 효율향상에 악영향을 미칠 것이다. 또한 동작 조건이나 적용되는 회로에 따라 필터의 설계 방법이 달라지기 때문에 구현상의 문제점도 발생한다.

본 논문에서는 RF Energy Harvesting System의 구현을 위한 렉테나의 설계에 사용되는 고효율 RF-DC 정류회로를 제안하였다. RF-DC 변환효율에 큰영향을 미치는 RF-DC 정류회로에 고효율 전력증폭기의 고조파 차단 회로망개념을 적용하여 입·출력단에 각각 새롭게 고안된 고조파 차단 회로망의 구조를 제시하였다. 출력단 고조파 차단 회로망은 다이오드의 비선형 특성에 의해서 발생된 고조파 성분을 다이오드로 반사시켜 직류 전력으로 전환하게 함으로써 RF-DC 변환효율을 높일 수 있다. 또한 입력단 고조파 차단 회로망을 이용하면 다이오드에서 재방사되는 비선형 성분을 차단하고 임피던스 정합회로로써의 역할도 기대할 수 있다. 2.45 GHz의 주파수에서 동작하도록 설계된 본 회

로를 측정하여 140 mW의 RF전력이 인가되었을 때 10.59 V 의 직류전압과약 80.59 %의 효율을 얻을 수 있었다. 제작된 회로의 크기는 80mm X 55mm이다. 이 회로는 입력단 고조파 차단 회로망만 적용한 회로와 비교했을 때 평균 5 % 가량 높은 변환효율을 보여 출력단 고조파 차단 회로망의 비선형 차단 특성을 입증했다. 출력단 고조파 차단 회로망만 적용한 회로와 비교했을 땐 1 % 내에서 변환효율 차이를 보였고 정합회로로써의 동작도 입증했다. 측정결과는 제안된 구조의 타당성을 입증한다. 본 구조를 이용하면 다양한 기기에서 적용할 수 있도록 손쉽게 변환이 가능하다. 제안된 새로운 RF-DC 정류회로의 설계 방법을 이용하여 고효율의 무선 전력 전송 시스템을 구현할 수 있을 것이라기대된다.

# 참 고 문 헌

- [1] T. Sekitani et al., "A large-area wireless power transmission sheet using printed organic transistors and plastic MEMS switches." *Nat. Mater.*, vol. 6, pp. 413-417, Jun. 2007.

- [2] A. Kurs et al., "Wireless power transfer via strongly coupled magnetic resonances," *Science*, vol. 317, pp. 83-86, Jun. 2007.

- [3] W. Stewart, "The Power to Set You Free," *Science*, vol. 317, pp. 55-56, Jul. 2007.

- [4] A. Karalis, J. D. Joannopoulos, M. Soljacic, "Efficient Wireless Non-radiative Mid-range Energy Transfer," *Ann. Phys.*, vol. 323, pp. 34-48, Apr. 2007.

- [5] MIT, Technology Review, Mar./Apr. 2008.

- [6] J. U. M. Araiza, "Wireless transmission of power for sensors in context aware spaces", *Master of Science in Media Arts and Sciences at MIT*, Jun. 2002.

- [7] Y. J. Ren, K. Chang, "5.8-GHz circularly polarized dual-rhombic-loop traveling-wave rectifying antenna for low power-density wireless power transmission applications", *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 5, pp. 1548-1553, May 2003.

- [8] N. Shinohara and H. Matsumoto, "Experimental Study of Large

- Rectenna Array for Microwave Energy Transmission", *IEEE Trans.*Microw. Theory Tech., vol. 46, no. 3, pp. 261-268, Mar. 1998.

- [9] Y. J. Ren, K. Chang, "Bow-tie retrodirective rectenna", *IEEE Electron. Lett.*, vol. 42, no. 4, pp. 191-192, Feb. 2006.

- [10] Y. Fujino et al., "A Dual Polarization Microwave Power Transmission System for Microwave propelled Airship Experiment", Proc. of ISAP' 96, vol. 2, pp. 393-396, 1996.

- [11] S. A. Maas, *Microwave Mixers*, Artech House, Dedham, Mass, 1993.

- [12] D. M. Pozar, Microwave Engineering 3rd ed., Wiley, 2005.

- [13] S. C. Cripps, RF Power Amplifiers For Wireless Communications, Artech House, Norwood, MA, 2006.

- [14] F. H. Raab, "Idealized operation of the Class E tuned power amplifier," *IEEE Trans. Circuits and Systems*, vol. CAS-24, no. 12, pp. 725-735, Dec. 1977.

- [15] N. O. Sokal, "Class-E High-Efficiency RF/Microwave Power Amplifiers: Principles of Operation, Design Procedures, and Experimental Verification", UC Berkeley.

- [16] B. Strassner and K. Chang, "5.8-GHz Circularly Polarized Rectifying Antenna for Wireless Microwave Power Transmission", IEEE Trans. Microw. Theory Tech., vol. 50, no. 8, pp. 1870-1876, Aug. 2002.

- [17] A. Alden and T. Ohno, "Single Foreplane high Power Rectenna", Electron. Lett., vol. 21, no. 11, pp. 1072-1073, 1992.

- [18] M. Arrawattia, M. S. Baghini, and G. Kumar, "RF Energy Harvesting System at 2.67 and 5.8GHz", in Asia-Pacific Microw. Conf. Proceedings, pp. 900-903, Nov. 2010.

- [19] S. Imai, K. Fujimori, M. Sanagi, and S. Nogi, "An important relation for determining a high-efficiency RF-DC Conversion Circuit", *in Asia-Pacific Microw. Conf. Proceedings*, pp. 2319 2321, Nov. 2010.

- [20] T. Paing, J. Shin, R. Zane, and Z. Popovic, "Resistor Emulation Approach to Low-Power RF Energy Harvesting", *IEEE Trans. Power Electronics.*, vol. 23, no. 3, pp. 1494–1501, May 2008.

- [21] H. Jabbor, Y. S. Song, and T. T. Jeong, "RF energy harvesting system and circuits for charging of mobile devices", *IEEE Trans. Consumer Electron.*, vol. 56, no. 1, pp. 247–253, Feb. 2010.

- [22] T. Shibata et al., "Microwave Energy Transmission System for Microrobot", IEICE Trans. Electron., vol. 80-C, no. 2, pp. 303-308, 1997.

- [23] C. H. K. Chin, Q. Xue, and C. H. Chan, "Design of a 5.8-GHz Rectenna Incorporating a New Patch Antenna", IEEE Antenna Wirel. Propag. Lett., vol. 4, pp. 175-178, 2005.

- [24] J. A. Hagerty et al., "Broadband Rectenna Arrays for Randomly Polarized Incident Waves", Proc. of 30th European Microwave Conference, pp. 1-4, Oct. 2000.

- [25] Y. H. Suh, and K. Chang, "A Novel Low-Cost High-Conversion

- Efficiency Microwave Power Detector Using GaAs FET", Microw. Opt. Technol. Lett., vol. 44, no. 1, pp. 29-31, Nov. 2004.

- [26] C. Gomez, J. A. Garcia, A. Mediavilla, and A. Tazon, "A High Efficiency Rectenna Element using E-pHEMT Technology", Proc. of 12th GAAS Symposium, pp. 315-318, 2004.

- [27] D. Bouchouicha, M. Latrach, F. Dupont, and L. Ventura, "An experimental evaluation of surrounding RF energy harvesting devices", *in Proc. 40th Europeon Microw. Conf.*, pp. 1381–1384, Sep. 2010.

- [28] A. Douyere, J.D. Lan, and F. Alicalapa, "High efficiency microwave rectenna circuit: modeling and design", *IET Electron. Lett.*, vol. 44, no. 24, pp. 1409–1410, Nov. 2008.

- [29] Y. J. Ren, K. Chang, "Highly efficient C-band circularly polarized rectifying antenna array for wireless microwave power transmission applications", *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 6, pp. 1347–1356, Jun. 2003.

- [30] Y. J. Ren, K. Chang, "5.8-GHz circularly polarized dual-diode rectenna and rectenna array for microwave power transmission", *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 7, pp. 1495-1502, Jul. 2006.

- [31] T. Yamamoto, K. Fujimori, M. Sanagi, and S. Nogi, "Design of highly efficient and compact RF-DC conversion circuit at mW-class by LE-FDTD method", *IEICE Trans. Eletron.*, vol. E93-C, no. 8, pp. 1323-1332, Aug. 2010.

- [32] T. Yamamoto, K. Fujimori, M. Sanagi, and S. Nogi, "The fundamental design approach of the RF-DC conversion circuit for optimizing its characteristics", *in Proc. of 3rd Europeon Microw. Integ. Circuit Conf.*, pp. 370–373, Oct. 2008.

- [33] H. Takhedmit, B. Merabet, L. Cirio, B. Allard, F. Costa, C. Vollaire, and O. Picon, "A 2.45-GHz Dual-Diode RF-to-dc rectifier for rectenna applications", *in Proc. 40th Europeon Microw. Conf.*, pp. 37-40, Sep. 2010.

[34] H. Takedmit, "A 2.45-GHz Low Cost and Efficient Rectenna," *European Conf. on Antennas and Propagation*, Apr., 2010.