석사학위논문

# 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로

2015년 2월 23일

전 북 대 학 교 대 학 원

전 자 정 보 공 학 부

김 재 연

# 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로

CMOS Negative Group Delay Circuit Using Source Series Feedback Circuit and Shunt Resonating Resistance.

2015년 2월 23일

전 북 대 학 교 대 학 원

전자정보공학부

김 재 연

# 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로

지도교수 정 용 채

이 논문을 공학 석사 학위논문으로 제출함.

2014년 11월 24일

전 북 대 학 교 대 학 원

전 자 정 보 공 학 부

김 재 연

## 김재연의 석사학위논문을 인준함.

| 위원장 | 전북대대학교 | 교수 | 손 해 원 | (인) |

|-----|--------|----|-------|-----|

| 위원  | 전북대대학교 | 교수 | 임 동 구 | (인) |

| 위원  | 전북대대학교 | 교수 | 정 용 채 | (인) |

2014년 12월 12일

전 북 대 학 교 대 학 원

## 목 차

## ABSTRACT

| 1. | 서론                                  | . 1 |

|----|-------------------------------------|-----|

| 2. | 음의 군지연 특성 이론                        | 4   |

|    | 2.1 군지연 시간(Group Delay)             | . 4 |

|    | 2.2 Shunt-Series 공진구조의 음의 군지연 회로    | 4   |

|    | 2.3 Series-Parallel 공진구조의 음의 군지연 회로 | 10  |

| 3. | CMOS 음의 군지연 회로 설계                   | 14  |

|    | 3.1 전송선로 이론                         | 14  |

|    | 3.1.1 전송선로에 대한 집중 정수소자 회로모델         | 14  |

|    | 3.1.2 전송 선로상의 전파 전달                 | 17  |

|    | 3.1.3 무손실 선로                        | 19  |

|    | 3.2 전송 매트릭스                         | 20  |

|    | 3.2.1 ABCD 매트릭스                     | 20  |

|    | 3.2.2 Z 매트릭스                        | 24  |

|    | 3.2.3 Y 매트릭스                        | 25  |

|    | 3.3 CMOS & 수동 소자 결합                 | 26  |

| 3.3.1 CMOS 음의 군지연 증폭기 설계26                                                                             |

|--------------------------------------------------------------------------------------------------------|

| 3.3.2 Cascade 구조의 T매칭 음의 군지연 증폭기 설계 34                                                                 |

| 3.3.3 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로 설계                                                    |

| 4. 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 제작 및 측정 결과                                          |

| 4.1 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한         CMOS 음의 군지연 회로의 레이아웃       46                              |

| 4.2 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 분석 및 측정 결과                                         |

| 5. 결론                                                                                                  |

| REFERENCES                                                                                             |

| 그 림 목 록                                                                                                |

| 그림 1.1 피드포워드 선형화기법 2                                                                                   |

| 그림 2.1 (a) Shunt-Series 공진구조 음의 군지연 회로도, (b) 저항 값과<br>인덕턴스에 따른 음의 군지연 시간 특성, (c) 저항 값에 따른 Shunt-Series |

| 공진구조 음의 군지연의 전달 및 반사 계수 특성                                                                             |

| 그림 2.2 (a) Shunt-Series 공진 구조 음의 군지연 회로의 시뮬레이션, (b) 전달   |

|----------------------------------------------------------|

| 및 반사 계수 특성, (c) 군지연 특성                                   |

| 그림 2.3 (a) Series-Parallel 공진구조 음의 군지연 회로도, (b) 저항 값과    |

| 인덕턴스에 따른 음의 군지연의 시간 특성, (c) 저항 값에 따른 Series-Parallel     |

| 공진구조 음의 군지연 전달 및 반사 계수 특성12                              |

| 그림 2.4 Series-Parallel 공진구조 음의 군지연 회로의 시뮬레이션, (b) 전달 및   |

| 반사 계수 특성, (c) 군지연 특성 13                                  |

| 그림 3.1 전송선로의 길이 증가에 따른 전압 및 전류의 정의 및 등가회로 (a)            |

| 전압 및 전류의 정의 (b) 집중정수 등가회로15                              |

| 그림 3.2 (a) 2포트 회로망 (b) 2포트 회로망의 직렬 연결 21                 |

| 그림 $3.3$ 일반적인 어플리케이션을 사용하여 직렬로 접속한 $Z$ 파라미터 $24$         |

| 그림 $3.4$ 일반적인 어플리케이션을 사용하여 병렬로 접속한 $Y$ 파라미터 $25$         |

| 그림 3.5 제안하는 기본 회로도 26                                    |

| 그림 3.5 (a) 제안하는 기본 회로도, (b) 전달 계수 및 군지연 특성 32            |

| 그림 3.6 매트랩을 사용하여 나타낸 전달 계수 와 군지연 특성                      |

| 그림 3.7 저항 값과 캐패시턴스에 따른 음의 군지연 시간 특성                      |

| 그림 3.8 Cascade 구조의 T매칭 네트워크를 사용한 음의 군지연 회로 34            |

| 그림 3.9 Cascade 구조의 T매칭 네트워크의 (a) 반사 계수 특성들, (b) 전달       |

| 계수 및 군지연 특성                                              |

| 그림 $3.10$ 동작 주파수가 다른 NGD1과 NGD2를 이용한 음의 군지연 회로 $37$      |

| 그림 3.11 NGD1, NGD2의 전달 계수 및 군지연 특성                       |

| 그림 3.12 Cascade 구조의 기본 회로도                               |

| 그림 3.13 Cascade 구조의 기본 회로도의 전달 계수 와 군지연 특성 39            |

| 그림 3.14 NGD 회로도 변화순서                                     |

| 그림 3.15 매칭된 cascade 구조 Shunt-Series의 (a) 전달 계수 및 군지연 특성, |

| (b) 각각의 반사 계수, (c) 안정도                                   |

| 그림 3.16 매칭이 없는 cascade 구조 Shunt-Series의 (a) 전달 계수 및 군지연  |

| 특성, (b) 반사 계수 특성, (c) 안정도                                |

| 그림 3.17 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS    |

|-------------------------------------------------|

| 음의 군지연의 전체 회로도                                  |

| 그림 3.18 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS    |

| 음의 군지연의 전체 회로도의 (a) 전달 계수 및 군지연 특성, (b) 반사 계수   |

| 특성, (c) 안정도                                     |

| 그림 4.1 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의  |

| 군지연 회로의 layout                                  |

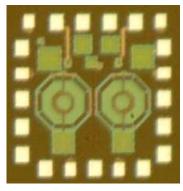

| 그림 4.2 제작된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS     |

| 음의 군지연 회로의 칩                                    |

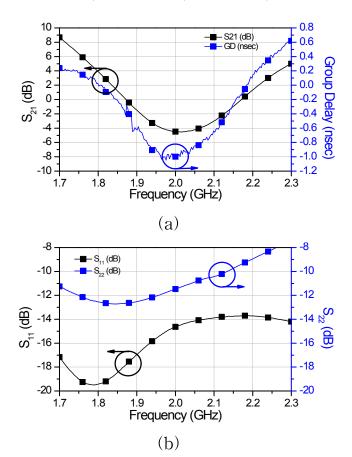

| 그림 4.3 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의      |

| 군지연 회로의 (a) 전달 계수 및 군지연 특성, (b) 반사 계수 특성들 48    |

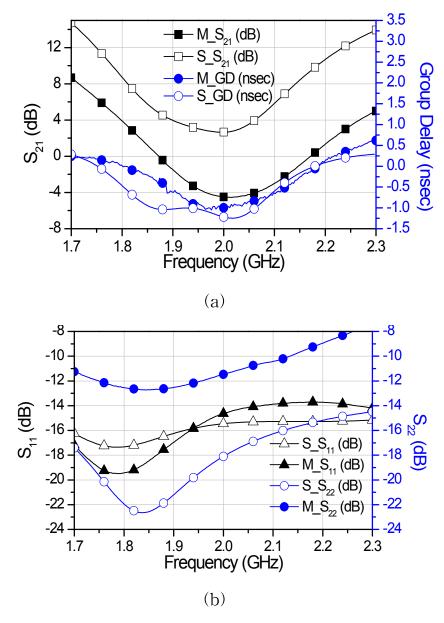

| 그림 4.4 시뮬레이션 결과와 측정 결과의 (a) 전달 계수 및 군지연 특성, (b) |

| 반사 계수 특성들 50                                    |

## 표 목 록

| 丑 3.1 | 몇몇 유용한 2포트 회로의 ABCD 파라미터2                                           | :3 |

|-------|---------------------------------------------------------------------|----|

| 班 3.2 | 2포트 회로망 파라미터 사이의 변환                                                 | 9  |

| 班 3.3 | 동작 주파수에서의 특성( $V_{DD}$ =1.2 V, $V_{G}$ =0.6 V, $I_{ds}$ =11.5 mA) 2 | 3  |

| 표 4.1 | 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의                             |    |

| 군지연   | 회로의 특성                                                              | 9  |

| 班 4.2 | 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의                             |    |

| 군지연   | 회로의 시뮬레이션 결과와 측정 결과 비교5                                             | 1  |

#### 초 록.

통신기술의 발전에 따라 다양한 통신 방식의 연구가 진행되고 있으며, 그 일환으로 단말기의 성능 및 무선 기지국 시스템의 성능을 극대화 시키기 위한 연구가 아직까지 활발히 이루어지고 있다. 급격히 증가하는 이동통신 이용자들을 한정된 주파수 자원으로 원활히 수용하기 위하여 우수한 선형성을 갖는시스템을 요구하게 된다. 지금까지 비선형 출력신호를 선형 신호로 개선시키는 선형화 기술 중에서 피드포워드(Feedforward)기술은 신호의 동일 진폭, 역 위상, 그리고 군지연 시간의 정확한 정합이 중요하게 알려져 있다.

따라서 본 연구에서는 CMOS 음의 군지연 회로를 설계 하였다. CMOS 음의 군지연 회로는 W-CDMA 상향 대역인 1.95 GHz(1.92 GHz ~ 1.98 GHz) 대역에서 설계 되었으며, 전달계수 특성은 -2.93±1.57 dB, 군지연 특성은 -0.8±0.2 nsec 이때, 대역폭은 244 MHz(1.836 GHz ~ 2.08 GHz) 그리고 반사계수 특성은 각각 -11 dB로 측정 하였다. 따라서 음의 군지연 증폭기를 이용하여 초고주파 송, 수신 시스템의 군지연 신호를 상쇄시키는 블록에 유용하게 사용될 수 있을 것이다.

주요어: 음의 군지연 회로, CMOS, 군지연 정합, 선형성, 본딩 와이어

#### ABSTRACT.

CMOS Negative Group Delay Circuit Using Source Series Feedback Circuit and Shunt Resonating Resistance.

Jaeyeon Kim

Department of Electronics and Information Engineering

Chonbuk National University

With increase demand of higher data rate of systems, the relevant of values of group delay seems necessary to insure the signal synchronization in RF/digital systems. Therefore, well-synchronization signals are required to maintain the system performance. Recently, some interesting studies of the negative group delay (NGD) concept have led to its experimental validation through the realization of electronic circuit. In order to enhance synchronization in the RF/microwave and millimeter-wave equipment, various techniques based on the application of the NGD concept at baseband and microwave bands were presented in previous works. However, the researches of NGD network in RFIC using CMOS process are lacking as compared with other areas.

In this research, the NGD circuit in CMOS process is proposed using source series feedback circuit and shunt resonating resistance. The propose active NGD network is designed using cascade amplifier in CMOS process, which can provide NGD as well as gain for wideband code division multiple access (W-CDMA) uplink band (1.92 ~ 1.98 GHz).

This work seems the first attempt to design NGD network using CMOS in the field of RFIC.

Keywords: Negative Group Delay Circuit, CMOS,

RF Communication transmitter, Matching network.

## 1. 서 론

통신기술의 발전에 따라 다양한 통신 방식의 연구가 진행되고 있으며, 그 일환으로 단말기의 성능 및 무선 기지국 시스템의 성능을 극대화시키기 위한 연구가 아직까지 활발히 이루어지고 있다. 이동통신 기기의 성능은 기기에 사용되는 고주파소자들에 의해서 상당부분 결정되므로 고주파 소자들에 대한기술 개발이 절실히 요구된다. 특히 이동 통신용 고주파소자는 기기의 성능을 좌우하는 핵심 부품으로 고효율화 및 선형성 향상 측면에서 다양한 연구가 이루어지고 있고, 급격히 중가하는 이동통신 이용자들을 한정된 주파수 자원으로 원활히수용하기 위하여 우수한 선형성을 갖는 시스템을 요구하게 된다.[1]

신호가 왜곡 없이 전달되려면 신호가 경유하는 시스템은 선형적인 특성을 가져야 한다. 만약 어떤 시스템이 비선형적인 특성을 가지고 있다면 입력되는 신호가 선형적이라 할지라도 출력 신호는 비선형적일 수밖에 없다. 예를 들어 이동통신 시스템의 경우 선형 입력 신호 대비 비선형 출력 신호를 지적할수 있는데, 이러한 신호 관계는 AMtoAM, AMtoPM, 혼변조 왜곡(Intermodulation Distortion : IMD), 인접채널 전력비 (Adjacent Channel Power Ratio : ACPR) 등을 이용하여 설명

할 수 있다. 지금까지 비선형 출력신호를 선형 신호로 개선시키는 선형화 기술 중에서 피드포워드(Feedforward) 기술은 신호의 동일 진폭, 역 위상, 그리고 군지연 시간의 정확한 정합이 중요하게 알려져 있다.<sup>[2][3]</sup>

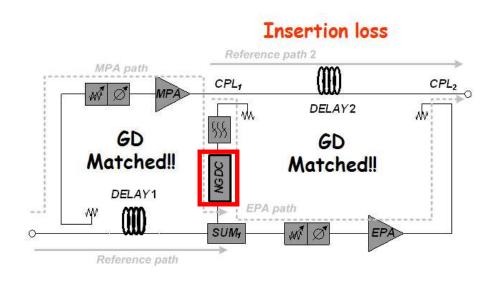

그림 1.1 피드포워드 선형화기법.

Fig. 1.1 Feedforward linearization technique.

입력에서 신호가 들어오고 MPA에서 증폭된 신호와 군지연을 맞추기 위해 Delay1 소자를 삽입하고, EPA도 마찬가지로 군지연을 맞추기 위해 Delay2 소자를 삽입해준다. 이때, Delay 소자들은 피드포워드 선형화 기술의 효율 저하에 주요 원인이된다. 본 논문에서는 이런 문제점을 상쇄하기 위해서 피드포워드 회로에 음의 군지연 회로(Negative Group Delay Circuit:

NGDC)를 삽입하여 Delay2 소자를 상쇄하여 효율을 상승 시키고, 전체 회로도의 크기를 최소화 시킨다. 그리고 NGDC가 Delay2 소자 보다 크다고 하면, Delay1 소자도 같이 상쇄가되어 효율과 크기에 대해 이점이 있다.

본 논문에서는 기저대역 에서의 음의 군지연 특성<sup>[4]</sup>이 아닌 WCDMA 상향 대역인 1.95 GHz(1.92 GHz ~ 1.98 GHz) 음의 군지연을 제공 할 뿐만 아니라, 수동 군지연 회로와는 달리 동작 주파수에서 이득을 가진다.

## 2. 음의 군지연 특성 이론

## 2.1 군지연 시간(Group Delay)

군 지연 시간은 신호가 임의의 시스템을 통과하는데 얼마의 시간이 걸리는가를 나타낸다. 그것은 시스템의 전기적 특성과 물리적 길이에 큰 영향을 받고, 보통 주파수에 대해서는 크게 영향을 받지 않는다. 일반적으로 군 지연 시간은 각주파수 변 화에 따라 전체 위상의 변화율로 나타낼 수 있으며, 아래의 수 식과 같이 정의 할 수 있다.<sup>[5]</sup>

$$GD = -\frac{d\phi}{d\omega} \tag{1}$$

여기에서  $\phi$  와  $\omega$  는 각각 전체 위상의 변화와 각주파수를 나타낸다. 또한, 군지연 시간 왜곡은 송수신 신호나 데이터의 왜곡을 관찰하는 중요한 파라미터이다.

## 2.2 Shunt-Series 공진구조의 음의 군지연 회로

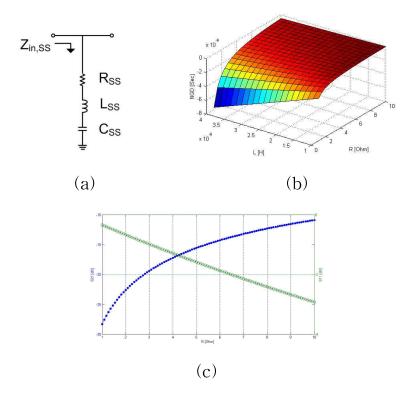

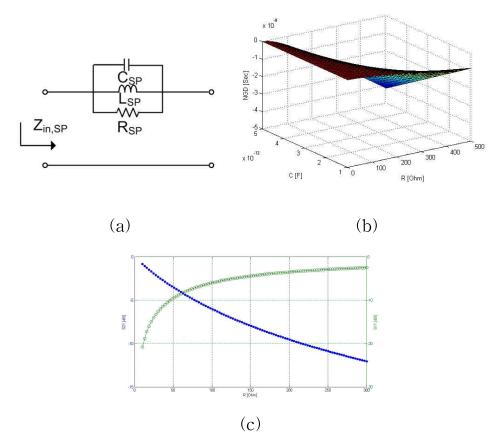

그림 2.1 (a)는 제안하는 Shunt-Series 공진구조의 음의 군지 연 기본 회로도를 나타내고 있다. 기본적으로 이 회로는 L 과 C를 공진회로에 소모성 저항이 부착되어서, 공진 주파수에서

감쇄를 일으키는 작용을 한다. 이 Shunt-Series-NGDC의 입력 임피던스는 식 (2)와 같이 표현된다.

$$Z_{in,SS} = R_{SS} + j\omega L_{SS} + \frac{1}{j\omega C_{SS}}$$

(2)

식 (2)와 식 (3)은 Shunt-Series 공진회로의 ABCD파라미터로 부터 전달 계수  $(S_{21})$ 의 위상 계수  $(\phi_{ss})$ 를 식(3)과 같이 나타낼 수 있다.

$$\begin{pmatrix} A & B \\ C & D \end{pmatrix}_{SS} = \begin{pmatrix} 1 & 0 \\ Y_{in,SS} & 1 \end{pmatrix} = \begin{pmatrix} 1 & 0 \\ 1/\left[R_{SS} + j\left(\frac{\omega^2 L_{SS}C_{SS} - 1}{\omega C_{SS}}\right)\right] & 1 \end{pmatrix}$$

(3)

$$S_{21} = \frac{2}{A + \frac{B}{Z_0} + CZ_0 + D} = \frac{2}{2 + Z_0 \left( \frac{1}{R_{SS} + j \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right)} \right)}$$

$$= \frac{2 \left( R_{SS} + j \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right) \right)}{2 \left( R_{SS} + j \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right) \right) + Z_0} = \frac{2R_{SS} + 2j \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right)}{Z_0 + 2R_{SS} + 2j \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right)}$$

(4)

$$\phi_{SS} = \tan^{-1} \left[ \frac{2 \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right)}{2R_{SS}} \right] - \tan^{-1} \left[ \frac{2 \left( \omega L_{SS} - \frac{1}{\omega C_{SS}} \right)}{2R_{SS} + Z_0} \right]$$

(5)

식 (3)으로부터 Øss의 시간 변화에 따른 변화율을 통해 군지 연 시간을 유도할 수 있는데, 이때, 공진 조건을 ☞= √1cc 을 대입 하면 식 (4)와 같이 간략화 할 수 있다.

$$GD_{SS}\big|_{\omega=1/\sqrt{L_{SS}C_{SS}}} = -\frac{d}{d\omega} \tan^{-1} \left[ \frac{\omega L_{SS} - \frac{1}{\omega C_{SS}}}{R_{SS}} \right] + \frac{d}{d\omega} \tan^{-1} \left[ \frac{2\left(\omega L_{SS} - \frac{1}{\omega C_{SS}}\right)}{2R_{SS} + Z_0} \right]$$

$$= -\frac{2L_{SS}Z_0}{R_{SS}\left(2R_{SS} + Z_0\right)}$$

(6)

식 (6)에서 모든 파라미터들이 양의 값을 가지므로 군지연시간은 음의 값을 갖게 된다. 따라서 제안한 회로가 동작 주파수에서 공진이 되도록 하면 NGD의 특성을 얻을 수 있음을 수식으로부터 확인할 수 있다. 임의의 동작 주파수에서 임의의원하는 NGD를 얻기 위해서는 식 (6)을 통해  $R_{SS}$ 와  $L_{SS}$  소자값을 정할 수 있고, 공진 조건을 이용하여  $C_{SS}$ 값은  $L_{SS}$ 값에 따라 소자 값을 얻을 수 있다. 회로 소자 값들의 조합에 따른 NGD 변화의 직접적인 이해를 돕고자 Matlab 프로그램을 이

용하여 그림 2.1 (b)와 같이 3차원 그래프로 나타내었으며, 이를 통해 제안된 SS-NGDC의 군지연은 저항 값에 반비례하고 인덕턴스에 비례함을 알 수 있다. 또한, SS-NGDC의 전달계수와 반사 계수 특성을 그림 2.1 (c)에 나타내었다. 저항 값을 0으로 접근시킬수록 NGD의 증가를 가져오지만 삽입 손실 (Insertion loss: IL)의 증가와 반사 특성의 열화를 초래함을 그래프로 확인할 수 있었다.

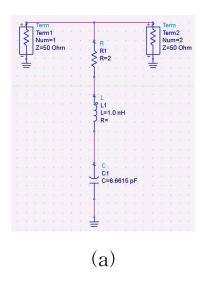

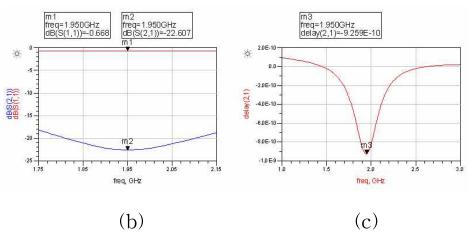

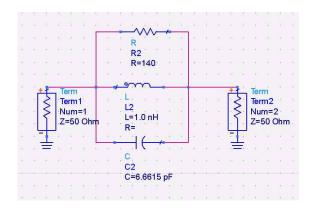

Agilent사의 ADS2013을 이용하여 SS-NGDC의 회로 시뮬레이션 결과들을 그림 2.2에 나타내었다. 1.95 GHz 대역에서 -0.9 nsec의 NGD를 얻기 위해서 식 (6)와 그림 2(b)를 이용하여 회로 소자 값을 추출하였는데, 필요 소자 값은 각각 R<sub>SS</sub>=2 Ω, C<sub>SS</sub>=6.6615 pF, L<sub>SS</sub>=1 nH 로 설정하였다. 이때 삽입 손실과 반사 계수는 각각 -22.6 dB와 -0.67 dB이며, 신호의 전달및 반사 계수 특성과 NGD 특성을 그림 2.2 (b)와 그림 2.2(c)에 나타내었다. 시뮬레이션으로 얻어진 NGD 시간이 Matlab의 그림 2.1 (b), (c)과 Agilent사의 ADS2013에서 얻어진 그림 2.2 (b), (c)의 값들이 일치함을 확인할 수 있다.

그림 2.1 (a) Shunt-Series 공진구조 음의 군지연 회로도, (b) 저항 값과 인덕턴스에 따른 음의 군지연 시간 특성, (c) 저항 값에 따른 Shunt-Series 공진구조 음의 군지연 전달 및 반사 계수 특성.

Fig. 2.1 (a) Circuit diagram of Shunt-Series-NGDC, (b) 3D plot of Shunt-Series-NGDC according to the resistance and inductance, and (c) transmission and input reflection characteristic with respect to resistance.

그림 2.2 (a) Shunt-Series 공진구조 음의 군지연 회로의 시뮬레이션, (b) 전달 및 반사 계수 특성, (c) 군지연 특성

Fig. 2.2 (a) Simulation of Shunt-Series-NGDC, (b) transmission and reflection characteristic, and (c) group delay characteristic.

## 2.3 Series-Parallel 공진구조의 음의 군지연 회로

그림 2.3 (a)은 Series-Parallel 공진구조를 갖는 또 다른 구조음의 군지연 회로 이다. 앞 절과 유사한 과정을 통하여 NGD에 대한 일반식을 전개한다. 단, 공진 조건인 ☞= √1元 일 때, 다음과 같은 수식을 얻을 수 있다.

$$Z_{in,SP} = \frac{1}{\frac{1}{R_{SP}} + \frac{1}{j\omega L_{SP}} + j\omega C_{SP}} = \frac{\omega L_{SP} R_{SP}}{\omega L_{SP} + jR_{SP} (\omega^2 L_{SP} C_{SP} - 1)}$$

(7)

$$\begin{pmatrix} A & B \\ C & D \end{pmatrix}_{SP} = \begin{pmatrix} 1 & Z_{in,SP} \\ 0 & 1 \end{pmatrix} = \begin{pmatrix} 1 & \frac{\omega L_{SP} R_{SP}}{\omega L_{SP} + j R_{SP} \left(\omega^2 L_{SP} C_{SP} - 1\right)} \\ 0 & 1 \end{pmatrix}$$

(8)

$$S_{21} = \frac{2}{A + \frac{B}{Z_0} + CZ_0 + D}$$

$$= \frac{2Z_0 \left(\omega L_{SP} + jR_{SP} \left(\omega^2 L_{SP} C_{SP} - 1\right)\right)}{2Z_0 \left(\omega L_{SP} + jR_{SP} \left(\omega^2 L_{SP} C_{SP} - 1\right)\right) + \omega L_{SP} R_{SP}}$$

(9)

$$\phi_{SP} = \tan^{-1} \left[ \frac{2Z_0 R_{SP} \left( \omega^2 L_{SP} C_{SP} - 1 \right)}{2Z_0 \omega L_{SP}} \right] - \tan^{-1} \left[ \frac{2Z_0 R_{SP} \left( \omega^2 L_{SP} C_{SP} - 1 \right)}{2Z_0 \omega L_{SP} + \omega L_{SP} R_{SP}} \right]$$

(10)

$$GD_{SP}|_{\omega=1/\sqrt{L_{SS}C_{SS}}} = -\frac{d}{d\omega} \tan^{-1} \left[ \frac{R_{SP} \left( \omega^2 L_{SP} C_{SP} - 1 \right)}{\omega L_{SP}} \right] + \frac{d}{d\omega} \tan^{-1} \left[ \frac{2Z_0 R_{SP} \left( \omega^2 L_{SP} C_{SP} - 1 \right)}{2Z_0 \omega L_{SP} + \omega L_{SP} R_{SP}} \right]$$

(11)

식 (11)에서 모든 파라미터들의 양의 값을 가지므로 군지연시간은 음의 값을 갖게 된다. 따라서 제안된 SP-NGDC 역시동작 주파수에서 공진이 되도록 한다면 NGD 특성을 얻을 수있음을 수식으로 확인할 수 있다. 회로 소자 값에 따른 NGD변화의 직접적인 이해를 위해 Matlab 프로그램을 이용하여 그림 2.3 (b)와 같이 3차원 그래프로 나타내었으며, 제안된SP-NGDC의 군지연은 저항값에 비례하고 커패시턴스에 비례함을 알 수 있다. 또한, SP-NGDC의 전달 계수와 반사 계수특성을 그림 2.3 (c)에 나타내었다. NGD의 증가는 삽입 손실의 증가와 반사 특성의 열화를 동반함을 확인할 수 있었다. 시뮬레이션으로 얻어진 NGD 시간이 Matlab의 그림 2.3 (b), (c)과 Agilent사의 ADS2013에서 얻어진 그림 2.4 (b), (c)의 값들이 일치함을 확인할 수 있다.

그림 2.3 (a) Series-Parallel 공진구조 음의 군지연 회로도, (b)저항 값과 캐패시턴스에 따른 음의 군지연 시간 특성, (c) 저항 값에 따른 Series-Parallel 공진구조 음의 군지연의 전달 및 반사 계수 특성.

Fig. 2.3 (a) Circuit diagram of Series-Parallel-NGDC, (b) 3D plot of Series-Parallel according to the resistance and capacitance, and (c) transmission and reflection characteristic with respect to resistance.

그림 2.4 (a) Series-Parallel 공진구조 음의 군지연 회로의 시뮬레이션, (b) 전달 및 반사 계수 특성, (c) 군지연 특성

Fig. 2.4 (a) Simulation of Series-Parallel-NGDC, (b) transmission and reflection characteristic, and (c) group delay characteristic.

## 3. CMOS 음의 군지연 회로 설계

앞장에서 NGD의 단점으로는 삽입손실과 좁은 대역폭을 그래 프에서 볼 수 있다. 이러한 문제점을 본 논문에서는 동부0.11 um 공정을 이용하여 RFIC로 음의 군지연 회로를 설계하고, 제안된 WCDMA 상향 대역인 1.95 GHz에서 음의 군지연을 제공 할 뿐만 아니라, 수동 군지연 회로와는 달리 동작 주파수에서 이득을 가지는 회로를 설계하였다.

## 3.1 전송선로 이론

전송선로 이론은 많은 방면에서 필드 해석과 기본적인 회로이론 사이를 연결해 주는 역할을 하므로 초고주파 회로해석에 있어 매우 중요하다. 전송선로에서 전파의 전달현상은, 회로이론의 확장 또는 맥스웰 방정식의 특성화로부터 다루어 질 수있다.

#### (1) 전송선로에 대한 집중 정수소자 회로모델

회로이론과 전송선로 이론의 주된 차이점은 전기적인 크기이다. 회로해석에서는 회로망의 물리적인 크기가 파장에 비하여 훨씬 작지만, 전송선로는 그 크기가 한 파장 길이의 극히일부 또는 수 파장에 해당된다. 이처럼 전송선로는 분산 정수

회로망이며, 이 회로망에서 전압과 전류들은 선로 전체에 걸쳐 크기와 위상이 변화될 수 있다. 그림 3.1(a)에 나타낸 바와 같이 전송선로는 자주 2선식 선로로서 도시적으로 표현되는데, 그 이유는 TEM파가 전파되는 전송선로들은 항상 최소 2개의도체를 포함하고 있어야 하기 때문이다. 그림 3.1(a) 선로의 한짧은 구간인 길이  $\Delta z$  는 그림 3.1(b)에 나타낸 바와 같이 집중 정수회로로 모델링 될 수 있으며, 여기서 R, L, G, C는 선로의 단위 길이당의 크기로서 아래와 같다.

그림 3.1 전송선로의 길이 증가에 따른 전압 및 전류의 정의 및 등가회로 (a) 전압 및 전류의 정의 (b) 집중정수 등가회로

Fig. 3.1 Voltage and current definitions and equivalent circuit for an incremental length of transmission line. (a) voltage and current definitions (b) lumped-element equivalent circuit.

R: 양쪽 도체에 대한 단위 길이당 직렬 저항 $[\Omega/m]$

L: 양쪽 도체에 대한 단위 길이당 직렬 인덕턴스[H/m]

G: 단위 길이당 병렬 컨덕턴스[S/m]

C: 단위 길이당 병렬 캐패시턴스[F/m]

직렬 인덕턴스 L은 두 도체들의 전체 자기 인덕턴스 값을 나타내며, 반면에 병렬 캐패시턴스 C는 두 도체들이 근접하여 있음을 기인된다. 직렬 저항 R은 도체의 유한한 도전율에 기인한 저항 값을 나타내며, 반면에 병렬 컨덕턴스 G는 도체들사이에 있는 매질 내에서의 유전체 손실에 기인한다. 그림 3.1(b)의 회로에 키르히호프 전압법칙을 적용하면,

$$\upsilon(z,t) - R\Delta z i(z,t) - L\Delta z \frac{\partial i(z,t)}{\partial t} - \upsilon(z + \Delta z,t) = 0$$

(12)

반면에 키르히호프 전류법칙을 적용하면,

$$i(z,t) - G\Delta z \upsilon(z + \Delta z, t) - C\Delta z \frac{\partial \upsilon(z + \Delta z, t)}{\partial t} - i(z + \Delta z, t) = 0 \quad (13)$$

식 (12)과 식 (13)을  $\Delta z$ 로 나누고,  $\Delta z \rightarrow 0$  과 같이 극한을 취하면 다음의 미분 방정식을 얻는다.

$$\frac{\partial \upsilon(z,t)}{\partial z} = -Ri(z,t) - L\frac{\partial i(z,t)}{\partial z} \tag{14}$$

$$\frac{\partial i(z,t)}{\partial z} = -G(z,t) - C\frac{\partial v(z,t)}{\partial z} \tag{15}$$

이들 방정식은 전송선로 방정식의 시간 영역의 형태이다. 코사인 페이저(cosine-based phasors)를 갖는 정현적인 정상상 태(sinusoidal steady-state equation)에 대하여 식 (14)와 식 (14)를 간단히 하면,

$$\frac{dV(z)}{dz} = -(R + j\omega L)I(z) \tag{16}$$

$$\frac{dI(z)}{dz} = -(G + j\omega C)V(z) \tag{17}$$

와 같이 나타낼 수 있다.

### (2) 전송 선로상의 전파 전달

식 (14)와 식 (15)의 두 방정식을 연립하여 풀면 V(z)와 I(z)에 대한 파동방정식을 얻을 수 있다.

$$\frac{d^2V(z)}{dz^2} - \gamma^2V(z) = 0 \tag{18}$$

$$\frac{d^2I(z)}{dz^2} - \gamma^2I(z) = 0 \tag{19}$$

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(20)

여기서  $\Gamma$  식 (16)와 식 (17)의 두 방정식을 연립하여 풀면 V(z)와 I(z)에 대한 파동방정식을 얻을 수 있다.

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{-\gamma z}$$

(21)

$$I(z) = I_0^+ e^{-\gamma z} + I_0^- e^{-\gamma z}$$

(22)

여기서,  $e^{-r_z}$  항은 +z 방향으로 전파하는 파를 나타내며,  $e^{+r_z}$  항은 -z 방향으로 전파하는 파를 나타낸다. 식 (22)의 전압을 식 (16)에 대입하면 선로상의 전류를 얻는다.

식 (22)와 비교하면 특성 임피던스(characteristic impedance) Z₀를 다음과 같이 정의 할 수 있다.

$$Z_0 = \frac{R + j\omega L}{\gamma} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(23)

이를 선로상의 전압과 전류로 표현하면,

$$\frac{V_0^+}{I_0^+} = Z_0 = \frac{-V_0^-}{I_0^-} \tag{24}$$

따라서, 식 (22)은 다음 식의 형태로 쓸 수 있다.

$$I(z) = \frac{V_0^+}{Z_0} e^{-\gamma z} - \frac{V_0^-}{Z_0} e^{+\gamma z}$$

(25)

시간영역에서 전압파형은 다음과 같이 표현된다.

$$v(z,t) = |V_0^+|\cos(\omega t - \beta z + \phi^+)e^{-\alpha z} + |V_0^-|\cos(\omega t + \beta z + \phi^-)e^{-\alpha z}$$

(26)

#### (3) 무손실 선로

위의 해는 손실효과를 포함하고 있는 일반적인 전송선로에 대한 것이었으며, 전파상수와 특성 임피던스가 복소수로 되어 있음을 볼 수 있다. 그러나 대부분의 실제 경우에 있어서, 선로상의 손실은 매우 작으며, 무시될 수 있으므로 위의 결과 식은 간략 화할 수 있다. 식 (20)에서 R=G=0으로 놓으면 전파상수는

$$\gamma = \alpha + j\beta = j\omega\sqrt{LC} \tag{27}$$

$$\beta = \omega \sqrt{LC}, \ \alpha = 0 \tag{28}$$

무손실의 경우 예상했던 바와 같이 감쇠상수 a 는 영이 된다. 4(20)의 특성 임피던스는

$$Z_0 = \sqrt{\frac{L}{C}} \tag{29}$$

로 로 되어 실수 값이 된다. 무손실 전송선로의 전압과 전류에 대한 일반해는 다음과 같이 쓸 수 있다.

$$V(z) = V_0^+ e^{-j\beta z} + V_0^- e^{+j\beta z}$$

(30)

$$I(z) = \frac{V_0^+}{Z_0} e^{-j\beta z} + \frac{V_0^-}{Z_0} e^{+j\beta z}$$

(31)

## 3.2 전송 매트릭스

전압과 전류가 마이크로파 회로망 내의 다수의 지점에서 정의되면, 회로이론에서 나타나는 임피던스 or 어드미턴스 매트릭스를 사용하여 터미널 혹은 포트에 나타나는 양들을 서로연관 지을 수 있으며, 본질적으로 그 회로망을 매트릭스 형태로 표현할 수 있게 된다. 결합기 or 필터와 같은 수동소자의설계할 때 유용하게 쓰인다. 본 논문에서는 IC의 CMOS MOSFET과 수동소자(R, L, C)를 이용하여 수식적으로 분석하고, 임의의 NGD 시간을 얻을 수 있는 일반적 설계 식을 유도하였다.

## (1) ABCD 매트릭스

Z, Y 그리고 S 파라미터는 임의의 포트 수를 갖는 초고주파 회로망을 특정 짓는데 사용될 수 있지만 실질적으로 많은 초고주파 회로망은 두 개 혹은 그 이상의 포트를 갖는 회로망의 직렬연결로 구성되어 있다. 이 경우 각각의 2포트 회로망에 대해 2×2 전송, 혹은 ABCD 매트릭스를 정의하는 것이 간편하다. 두 개 혹은 그 이상의 포트를 갖는 회로망이 직렬로 연결되어 있을 때 ABCD 매트릭스는 각각의 2포트 회로망의 ABCD 매트릭스를 곱함으로써 쉽게 구할 수 있다.

그림 3.2 (a) 2포트 회로망, (b) 2포트 회로망의 직렬연결 Fig. 3.2 (a) A-two-port network, (b) a cascade connection of two-port networks.

2포트 회로망에 대한 ABCD 매트릭스는 그림 3.2(a)에 나타 나낸 것과 같이 전체 전압과 전류에 의해 다음과 같이 정의된다.

$$V_1 = AV_2 + BI_2$$

$$I_1 = CV_2 + DI_2$$

이것을 매트릭스 형태로 나타내면 다음과 같다.

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A & B \\ C & D \end{bmatrix} \begin{bmatrix} V_2 \\ I_2 \end{bmatrix} \tag{32}$$

식 (32)의 좌변은 회로망의 포트 1에서의 전압과 전류를 나타내고 우변은 포트 2에서의 전압과 전류를 나타낸다.

그림 3.2(b)에서 보인 바와 같이 2개의 2포트 회로망이 직렬로 연결되어 있으면 각각의 ABCD 매트릭스는

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A_1 & B_1 \\ C_1 & D_1 \end{bmatrix} \begin{bmatrix} V_2 \\ I_2 \end{bmatrix}$$

(33)

$$\begin{bmatrix} V_2 \\ I_2 \end{bmatrix} = \begin{bmatrix} A_2 & B_2 \\ C_2 & D_2 \end{bmatrix} \begin{bmatrix} V_3 \\ I_3 \end{bmatrix} \tag{34}$$

가 된다. 식(34)을 식 (33)에 대입하면

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A_1 & B_1 \\ C_1 & D_1 \end{bmatrix} \begin{bmatrix} A_2 & B_2 \\ C_2 & D_2 \end{bmatrix} \begin{bmatrix} V_3 \\ I_3 \end{bmatrix}$$

$$(35)$$

가 되어 직렬로 연결된 2개의 회로망의 ABCD 매트릭스는 각각의 2포트를 나타내는 ABCD 매트릭스의 곱과 같다. 매트 릭스의 곱의 순서는 매트릭스의 곱이 일반적으로 교환법칙이 성립되지 않으므로 회로망이 정렬되어 있는 순서와 같아야 한 다.

ABCD 매트릭스 표현의 유용성은 기본적인 2포트 회로망에 대한 ABCD 매트릭스의 라이브러리를 형성하여 이렇게 간단한 2포트 회로망을 빌딩 블록으로 하여 직렬로 연결함으로써 보다 복잡한 초고주파 회로망을 구성하는데 적용할 수 있다는 것이다. 표 3.1은 사용하기에 편리한 몇 개의 2포트 회로망과 그의 ABCD 매트릭스를 나열한 것이다.

## 표 3.1 몇몇 유용한 2포트 회로의 ABCD 파라미터

Table 3.1 The ABCD parameters of some useful two-port circuits

| Circuit                       | ABCD Par                              | ameters                                                         |

|-------------------------------|---------------------------------------|-----------------------------------------------------------------|

| o Zo                          | A = 1                                 | B = Z                                                           |

| 00                            | C = 0                                 | D = 1                                                           |

| •                             | A = 1                                 | B = 0                                                           |

| · Y                           | C = Y                                 | D = 1                                                           |

| 0                             | $A = \cos \beta I$                    | $B = jZ_0 \sin \beta I$                                         |

| Z <sub>0</sub> , β            | $C = jY_0 \sin \beta l$               | $D = \cos \beta l$                                              |

| N:1                           | NON YOU                               |                                                                 |

| }{E                           | A = N $C = 0$                         | $B = 0$ $D = \frac{1}{N}$                                       |

| Y <sub>3</sub>                | $A = 1 + \frac{\gamma_2}{\gamma_3}$   | R _ 1                                                           |

| Y <sub>1</sub> Y <sub>2</sub> | $C = Y_1 + Y_2 + \frac{Y_1 Y_2}{Y_3}$ | $B = \frac{1}{Y_3}$ $D = 1 + \frac{Y_1}{Y_3}$                   |

| $\circ$ $Z_1$ $Z_2$ $\circ$   | $A = 1 + \frac{Z_1}{Z_3}$             | $B = Z_1 + Z_2 + \frac{Z_1 Z_2}{Z_1}$                           |

| Z <sub>3</sub>                | $C = \frac{1}{Z_3}$                   | $B = Z_1 + Z_2 + \frac{Z_1 Z_2}{Z_3}$ $D = 1 + \frac{Z_2}{Z_3}$ |

### (2) Z 매트릭스

그림 3.3에 표시된 것과 같이, 2포트 네트워크를 직렬로 접속된 경우, Z 파라미터로 전체 Z 파라미터를 찾을 수 있다. 식은(36)와 같이 나타낼 수 있다.

그림 3.3 일반적인 어플리케이션을 사용하여 직렬로 접속한 Z 파라미터

Fig. 3.3 Series connection using z parameters and a typical application.

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} V_1^a & V_1^b \\ V_2^a & V_2^b \end{bmatrix} \begin{bmatrix} Z_{11}^a + Z_{11}^b & Z_{12}^a + Z_{12}^b \\ Z_{21}^a + Z_{21}^b & Z_{22}^a + Z_{22}^b \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

(36)

#### (3) Y 매트릭스

그림 3.4에 표시된 것과 같이, 2포트 네트워크를 병렬로 접속된 경우, Y 파라미터로 전체 Y 파라미터를 찾을 수 있다. 식은(37)와 같이 나타낼 수 있다.

그림 3.4 일반적인 어플리케이션을 사용하여 병렬로 접속한 Y 파라미터

Fig. 3.4 Shunt connection using y parameters and a typical application.

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} I_1^a & I_1^b \\ I_2^a & I_2^b \end{bmatrix} \begin{bmatrix} Y_{11}^a + Y_{11}^b & Y_{12}^a + Y_{12}^b \\ Y_{21}^a + Y_{21}^b & Y_{22}^a + Y_{22}^b \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

(37)

### 3.3 CMOS 음의 군지연 증폭기 설계

앞의 2.2절의 그림 2.2에서 음의 군지연의 단점인 삽입손실을 확인할 수 있었다. 이러한 문제점을 해결하고자 본 논문에서는 MOSFET과 수동소자를 결합하여 제시한다.

#### (1) MOSFET & 수동 소자 결합

본 논문에서는 동부 0.11um공정을 사용하였고, 동작 주파수는 1.95 GHz이다. MOSFET과 수동소자를 이용하여 음의 군지연 증폭기 설계를 한다.

그림 3.5에서 본 논문에서 제안하는 기본구조의 회로도이다.

그림 3.5 제안하는 기본 회로도.

Fig. 3.5 Basic circuit diagram of the proposed.

그림 3.5에서 MOSFET과 수동소자 부분으로 먼저 나누어 수식적으로 분석을 한다. 먼저 수동 소자 의 입력 임피던스는 식 (38) 과 같이 나타 낼 수 있다.

$$Z_{in,pass} = \frac{1}{\frac{1}{R} + \frac{1}{j\omega L} + j\omega C} = \frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)}$$

(38)

식 (38)에서 구한 수동소자의 입력 임피던스를 표3.1을 이용하여 ABCD 매트릭스로 나타내면.

$$\begin{bmatrix} 1 & 0 \\ \frac{1}{R} + \frac{1}{j\omega L} + j\omega C \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ \frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)} & 1 \end{bmatrix}$$

(39)

식 (39)과 같이 표현할 수 있다. 여기서, MOSFOT과 수동소자를 결합하기 위해서는 앞 절 3.2.2의 Z 매트릭스를 이용하여야 한다. 그러므로 식 (39)의 ABCD 매트릭스를 Z매트릭스로 변환은 표 3.1을 사용하여 변환할 수 있다.

$$\begin{bmatrix}

\frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)} & \frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)} \\

\frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)} & \frac{\omega LR}{\omega L + jR(\omega^2 LC - 1)}

\end{bmatrix}$$

(40)

식 (40)은 Z 매트릭스의 수동소자를 나타낸 식이다.

MOSFET의 Z 매트릭스는 "Cadence" 라는 프로그램을 이 용하여 R은 MOSFET의 실수 성분, X는 MOSFET의 허수 성 분이라 표현하고, 수식 (41)과 같은 값을 추출할 수 있다. 이것을 수식으로 정리하면.

$$\begin{bmatrix} R_{11} + jX_{11} & R_{12} + jX_{12} \\ R_{21} + jX_{21} & R_{22} + jX_{22} \end{bmatrix}$$

(41)

수식 (41)과 같이 나타낼 수 있다.

이제 구분되었던 MOSFET과 수동소자 부분들을 하나의 매트릭스로 연결하기 하기 위해서, 전체 Z 매트릭스로 결합하게된다.

$$\begin{bmatrix} R_{11} + jX_{11} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} & R_{12} + jX_{12} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} \\ R_{21} + jX_{21} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} & R_{22} + jX_{22} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} \end{bmatrix}$$

(42)

전체 Z 매트릭스는 식 (42)과 같이 나타낼 수 있다.

전달 계수 또는 군지연 시간을 구하기 위해선 전체의 S 매트릭스가 필요하기 때문에 식 (42)의 전체 Z 매트릭스를 다시전체 S 매트릭스로 변환하게 되면, 수식 (43)을 이용하여 전달계수 또는 군지연 시간 수식을 전개하였다.

## 표 3.2 2포트 회로망 파라미터 사이의 변환

Table 3.2 Conversions between two-port network parameters

|                                        | is                                                                                                                        | Z                                                                                    | М                                                                             | ABCD                                            |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|

| SII                                    | Sn                                                                                                                        | $\frac{(Z_{11} - Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}}{\Delta Z}$                       | $(V_0 - V_{11})(V_0 + V_{22}) + V_{12}V_{21}$<br>$\Delta Y$                   | $\frac{A+B/Z_0 - CZ_0 - D}{A+B/Z_0 + CZ_0 + D}$ |

| \$12                                   | \$12                                                                                                                      | $\frac{2Z_{12}Z_0}{\Delta Z}$                                                        | $\frac{-2r_{12}r_0}{\Delta r}$                                                | $\frac{2(AD - BC)}{A + B/Z_0 + CZ_0 + D}$       |

| S21                                    | is,                                                                                                                       | $\frac{2Z_{21}Z_{0}}{\Delta Z}$                                                      | $\frac{-2r_{21}r_0}{\Delta r}$                                                | $\frac{2}{A+B/Z_0+CZ_0+D}$                      |

| Sz                                     | 252                                                                                                                       | $\frac{(Z_{11}+Z_0)(Z_{22}-Z_0)-Z_{12}Z_{21}}{\Delta Z}$                             | $\frac{(J_0+Y_{11})(J_0-Y_{22})+Y_{12}Y_{21}}{\Delta Y}$                      | $\frac{-A+B/Z_0-CZ_0+D}{A+B/Z_0+CZ_0+D}$        |

| ZII                                    | $Z_0 \frac{(1 + S_{11})(1 - S_{22}) + S_{12}S_{21}}{(1 - S_{11})(1 - S_{22}) - S_{12}S_{21}}$                             | Z)1                                                                                  | n n                                                                           | * 0                                             |

| Z <sub>12</sub>                        | $\frac{2\delta_{12}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}}$                                                                  | Z <sub>12</sub>                                                                      | $\frac{-y_{12}}{ y }$                                                         | AD - BC                                         |

| 221                                    | $\frac{z_{0}}{(1-s_{11})(1-s_{22})-s_{12}s_{21}}$                                                                         | $Z_{21}$                                                                             | $\frac{-\hat{x}_{21}}{ \mathcal{V} }$                                         | -10                                             |

| 222                                    | $z_0 \frac{(1-S_{11})(1+S_{22})+S_{12}S_{21}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}}$                                         | $z_{m}$                                                                              | $\frac{r_{31}}{ F }$                                                          | a   0                                           |

| $r_{\rm H}$                            | $I_0 \frac{(1-\delta_{11})(1+\delta_{22})+\delta_{12}\delta_{21}}{(1+\delta_{11})(1+\delta_{22})-\delta_{12}\delta_{21}}$ | Z <sub>22</sub><br> Z                                                                | ¥11                                                                           | 0 8                                             |

| Y <sub>12</sub>                        | $I_0 \frac{-2\beta_{12}}{(1+\beta_{11})(1+\beta_{22})-\beta_{12}\beta_{21}}$                                              | $\frac{-z_{12}}{ z }$                                                                | F12                                                                           | BC - AD                                         |

| $F_{21}$                               | $r_0 \frac{-2S_{21}}{(1+S_{11})(1+S_{22}) - S_{12}S_{21}}$                                                                | $-\frac{Z_{21}}{ Z }$                                                                | 721                                                                           | 17 81                                           |

| Fzz                                    | $r_0\frac{(1+S_{11})(1-S_{22})+S_{12}S_{21}}{(1+S_{11})(1+S_{22})-S_{12}S_{21}}$                                          | $\frac{Z_{11}}{ Z }$                                                                 | ra,                                                                           | *   a                                           |

| -                                      | $\frac{(1+S_{11})(1-S_{22})+S_{12}S_{21}}{2S_{21}}$                                                                       | $\frac{Z_{11}}{Z_{21}}$                                                              | -122<br>721                                                                   | ×                                               |

| 88                                     | $Z_0 \frac{(1 + S_{11})(1 + S_{22}) - S_{12}S_{21}}{2S_{21}}$                                                             | $\frac{ Z }{Z_{21}}$                                                                 | 723                                                                           | 88                                              |

| C                                      | $\frac{1}{z_0} \frac{(1 - S_{11})(1 - S_{22}) - S_{12}S_{21}}{2S_{21}}$                                                   | $\frac{1}{Z_{21}}$                                                                   | $\frac{- Y }{T_{23}}$                                                         | Ü                                               |

| Q                                      | $\frac{(1-\delta_{11})(1+\delta_{22})+\delta_{12}\delta_{21}}{2\delta_{21}}$                                              | $\frac{z_{22}}{z_{21}}$                                                              | $\frac{-y_{11}}{r_{21}}$                                                      | ٩                                               |

| $ Z  = Z_{11} Z_{22} - Z_{12} Z_{21};$ | $ T  = F_{11} T_{22} - F_{12} F_{21};$                                                                                    | $\Delta Y = (Y_{11} + Y_0)(Y_{22} + Y_0) - Y_{12}Y_{21};  \Delta Z = (Z_{11} + Z_0)$ | $\Delta Z = (Z_{11} + Z_0)(Z_{22} + Z_0) - Z_{12}Z_{21}; \qquad Y_0 = 1/Z_0.$ |                                                 |

$$\begin{bmatrix}

\frac{(Z_{11}-Z_0)(Z_{22}+Z_0)-Z_{12}Z_{21}}{(Z_{11}+Z_0)(Z_{22}-Z_0)-Z_{12}Z_{21}} & 2Z_{12}Z_0 \\

\frac{2Z_{21}Z_0}{(Z_{11}+Z_0)(Z_{22}-Z_0)-Z_{12}Z_{21}} & \frac{(Z_{11}+Z_0)(Z_{22}-Z_0)-Z_{12}Z_{21}}{(Z_{11}+Z_0)(Z_{22}-Z_0)-Z_{12}Z_{21}}

\end{bmatrix} (43)$$

$$S_{21} = \frac{2Z_{0} \left( R_{21} + jX_{21} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} \right)}{\left( R_{11} + jX_{11} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} + Z_{0} \right) \left( R_{22} + jX_{22} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} + Z_{0} \right)} - \left( \left( R_{12} + jX_{12} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} \right) \left( R_{21} + jX_{21} + \frac{\omega LR}{\omega L + jR(\omega^{2}LC - 1)} \right) \right)$$

$$(44)$$

$$\begin{split} S_{21} &= \frac{2Z_0R_{21}\omega L - 2Z_0X_{21}\omega^2RLC + 2Z_0X_{21}R + 2Z_0\omega RL + 2jZ_0X_{21}\omega L + 2jZ_0R_{21}\omega^2RLC - 2jZ_0R_{21}R}{R_{11}R_{22}\omega L + R_{11}Z_0\omega L - X_{11}X_{22}\omega L + R_{22}Z_0\omega L + Z_0^2\omega L - R_{12}R_{21}\omega L + X_{12}X_{21}\omega L - R_{11}X_{22}\omega^2RLC} \end{split} \tag{44-1}$$

$$-R_{22}X_{11}\omega^2RLC - X_{11}Z_0\omega^2RLC - X_{22}Z_0\omega^2RLC + R_{12}X_{21}\omega^2RLC + R_{21}X_{12}\omega^2RLC + R_{11}X_{22}R \\ +R_{22}X_{11}R + X_{11}Z_0R + X_{22}Z_0R + R_{12}R_{21}R - R_{12}X_{21}R - R_{21}X_{12}R + jX_{11}Z_0\omega L + jX_{22}Z_0\omega L \\ -jR_{12}X_{21}\omega L - jR_{21}X_{12}\omega L + jR_{11}R_{22}\omega^2RLC + jR_{11}Z_0\omega^2RLC - jX_{11}X_{22}\omega^2RLC + jR_{22}Z_0\omega^2RLC \\ +jZ_0^2\omega^2RLC - jR_{12}R_{21}\omega^2RLC + jX_{12}X_{21}\omega^2RLC - jR_{11}R_{22}R - jR_{11}Z_0R + jX_{11}X_{22}R - jR_{22}Z_0R \\ -jZ_0^2R - jX_{12}X_{21}R + jR_{11}X_{22}\omega L + jR_{22}X_{11}\omega L \end{aligned}$$

전달 계수 특성의 식이 식(44-1)에 자세히 나와 있다. 분자 분모에 실수파트 또는 허수파트로 나누어서 전개하였다.

여기서, X1=분자의 실수성분, X2=분자의 허수성분, X3=분모의 실수성분 그리고 X4=분모의 허수성분을 나타내고 있다.

$$\begin{split} \tau &= -\frac{d\phi}{d\omega} = -\frac{1}{1 + \left(\frac{X_2}{X_1}\right)^2} \cdot \frac{X_1 \frac{dX_2}{d\omega} - X_2 \frac{dX_1}{d\omega}}{X_1^2} + \frac{1}{1 + \left(\frac{X_4}{X_3}\right)^2} \cdot \frac{X_3 \frac{dX_4}{d\omega} - X_4 \frac{dX_3}{d\omega}}{X_1^2} \\ &= -\frac{X_2^{'} X_1 - X_2 X_1^{'}}{X_1^2 + X_2^2} + \frac{X_3^{'} X_4 - X_3 X_4^{'}}{X_3^2 + X_4^2} \end{split}$$

$$\tau = -\frac{\left(2Z_{0}\left(X_{21}L + R_{21}\omega RLC\right)\right)\left(2Z_{0}\left(R_{21}\omega L - X_{21}\omega^{2}RLC + X_{21}R + \omega RL\right)\right) - \left(2Z_{0}\left(X_{21}\omega L + R_{21}\omega^{2}RLC - R_{21}R\right)\right)\left(2Z_{0}\left(R_{21}L - 2X_{21}\omega RLC + RL\right)\right)}{\left(2Z_{0}\left(R_{21}\omega L - X_{21}\omega^{2}RLC + X_{21}R + \omega RL\right)\right)^{2} + \left(2Z_{0}\left(X_{21}\omega L + R_{21}\omega^{2}RLC - R_{21}R\right)\right)^{2}} \\ \left(L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + X_{12}X_{21}\right) + 2\omega RLC\left(-R_{11}X_{22} - R_{22}X_{11} - X_{11}Z_{0} - X_{22}Z_{0} + R_{12}X_{21} + R_{21}X_{12}\right)\right) \\ \left(\omega L\left(X_{11}Z_{0} + X_{22}Z_{0} - R_{12}X_{21} - R_{21}X_{12} + R_{11}X_{22} + R_{22}X_{11}\right) + \omega^{2}RLC\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + X_{12}X_{21}\right)\right) \\ - \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} - R_{22}Z_{0} - Z_{0}^{2} - X_{12}X_{21}\right)\right) \\ - \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + X_{12}X_{21}\right) + \omega^{2}RLC\left(-R_{11}X_{22} - R_{22}X_{11} - X_{11}Z_{0} - X_{22}Z_{0} + R_{12}X_{21} + R_{21}X_{22}\right)\right) \\ - \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + R_{12}X_{21} - R_{21}X_{21}\right)\right) \\ + \left(\omega L\left(R_{11}X_{22} + R_{22}X_{11} + X_{11}Z_{0} + X_{22}Z_{0} + R_{12}X_{21} + R_{11}X_{22} + R_{22}X_{11}\right) + \omega^{2}RLC\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}X_{21} + R_{21}X_{21}\right)\right) \\ + \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + X_{12}X_{21}\right) + \omega^{2}RLC\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + R_{12}X_{21} + R_{21}X_{21}\right)\right) \\ + \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + Z_{0}^{2} - R_{12}R_{21} + R_{21}X_{21}\right)\right)^{2} \\ + \left(\omega L\left(R_{11}R_{22} + R_{11}Z_{0} - X_{11}X_{22} + R_{22}Z_{0} + R_{22}Z_{1} + R_{21}X_{21}\right)\right)^{2} \\ + \left(\omega L\left(R_{11}R_{22} + R_{22}X_{11} + X_{11}Z_{0} + X_{22}Z_{0} + R_{22}Z_{0} + R_{22}Z_{0} + R_{22}Z_{11} + R_{21}X_{21}\right)\right)^{2} \\ + \left(\omega L\left(R_{11}R_{22} + R_{22}Z_{0} - R_{12}X_{21} - R_{21}X_{21} + R_{21$$

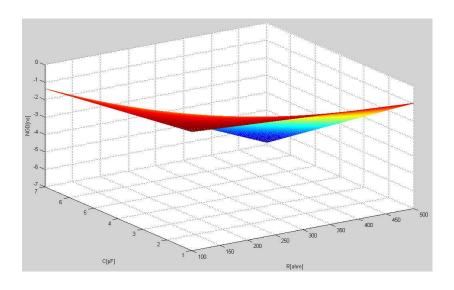

위의 식 (44)와 식 (45)은 너무 복잡하고 소자 값에 따른 전달 계수와 음의 군지연 시간특성 변화의 직관적인 이해를 돕기 위해 Matlab 프로그램을 이용하여 값을 비교하고 3차원 그래프로 나타내었다.

그림 3.5에서 각각 R=500 Ω, L=2 nH C=3.4 pF 였고, nmos의 width=5 u, finger의 개수는 5개로 설정하였다. 이때 시뮬레이션으로 얻어진 음의 군지연 시간이 약 -3 nsec 였고, 전달계수는 -15.5 dB 였다.

그림 3.5 (a) 제안하는 기본 회로도, (b) 전달 계수 및 군지연 특성.

Fig. 3.5 (a) Basic circuit diagram of the proposed, (b) transmission and group delay characteristic.

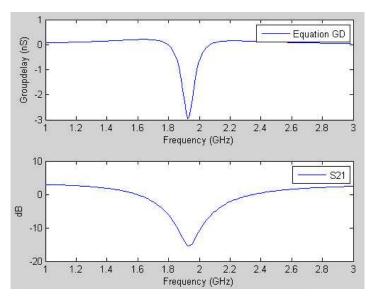

본 논문에서 제안된 회로 시뮬레이션 결과를 그림 3.5에 나타냈다. 식 (45)을 Matlab 프로그램을 이용하여 전달 계수 및 군지연 특성을 그림 3.6와 그림 3.7에 나타내었다. 시뮬레이션으로 얻어진 NGD가 -3 nsec, 전달계수는 -15.5 dB가 일치함을 확인할 수 있다.

그림 3.6 매트랩을 사용하여 나타낸 전달 계수 와 군지연 특성.

Fig 3.6 Transmission and group delay characteristics using Matlab.

그림 3.7 저항 값과 캐패시턴스에 따른 음의 군지연 시간 특성.

Fig 3.7 3D plot according to resistance and capacitance.

#### (2) Cascade 구조의 T매칭 음의 군지연 증폭기 설계

그림 3.6 에서 보면 음의 군지연의 특성이 나오는 것을 확인할 수 있지만, 단점인 삽입손실(IL)과 협대역도 확인할 수 있다. 이러한 문제점을 보안하기 위하여 본 논문에서는 MOSFET을 2단으로 이용하여 cascade 구조를 사용하였다. 그리고 회로의 안정도를 위해 MOSFET의 gate와 drain사이에 R, C feedback을 달아주었다. MOSFET의 gate쪽은 C로만 연결되어 있으므로 높은 임피던스로만 보이면 되기 때문에 layout상에서 넓은 면적을 차지하는 L보다 저항을 써서 면적을 조금 더 용이하게 설계하였다. 반사 계수를 위해 입/출력 쪽에 매칭네트워크를 달아주었다.

그림 3.8 Cascade 구조의 T매칭 네트워크를 사용한 음의 군지연 회로.

Fig 3.8 Negative Group Delay Circuit using T matching network of cascade structure.

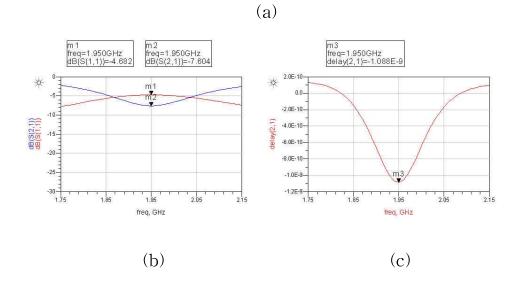

그림 3.9 Cascade 구조의 T매칭 네트워크의 (a) 반사 계수 특성들, (b) 전달 계수 및 군지연 특성.

Fig 3.9 T matching network of cascade structure (a) reflection characteristics, (b) transmission and group delay characteristic.

그림 3.8에서의 post simulation의 결과를 그림 3.9에 그래프로 나타내었다. MOSFET의 width=5 u, length=130 n, fingers=20로 설정하고, RC feedback의 R=1 KΩ, C=1 pF이다. 입/출력쪽에 매칭은 각각 T매칭을 이용하여서 동작 주파수에서의 각각의 반사 계수는 -16 dB이상으로 설계하였다. 전달 계수 특성은 8 dB, 군지연 시간은 -1 nsec을 얻을 수 있다.

## (3) 소스 직렬 부궤환 회로와 단락 공진 저항을 이용 한 CMOS 음의 군지연 회로 설계

그림 3.6 에서 보면 NGD의 단점인 삽입손실(IL)과 협대역 (narrow bandwidth)을 확인 할 수 있다. 그림 3.9의 음의 군지 연에 의해 동작 주파수에서 생기는 삽입손실은 극복 하였지만, 대역폭은 아직까지 협대역이다. 이러한 문제점을 보안하기 위하여 본 논문에서는 MOSFET의 source에 연결된 NGD를 각각 다른 주파수(1.93 GHz, 1.97 GHz)로 설정하였다.

앞 절에서 연결한 입/출력 T매칭은 군 지연 손실이 있으므로, 이번 절에서는 Shunt-Series매칭으로 바꿈으로써 수동 소자로 인한 군지연의 손실이 없을뿐더러, 작은 값이지만 음의군지연 값을 가진다. 그리고 넓은 대역폭을 가지는 매칭으로연결하였다. Shunt-Series매칭으로 R, C feedback 회로에 불필요하게 되어 여기서는 사용하지 않았다.

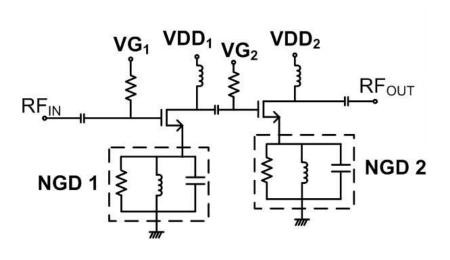

그림 3.10 동작 주파수가 다른 NGD1과 NGD2를 이용한 음의 군지연 회로.

Fig. 3.10 The operating frequency are different NGD1 and NGD2 using Negative Group Delay Circuit.

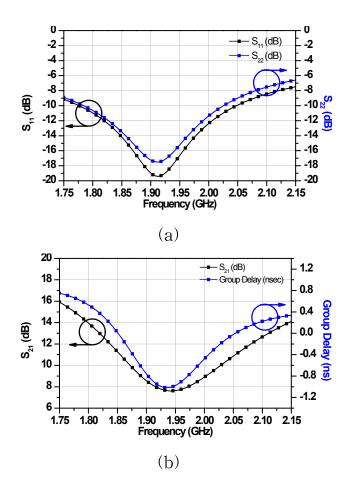

그림 3.10에 있는 NGD1, 2는 각각의 주파수가 다른 NGD1(1.93 GHz)와 NGD2(1.97 GHz)의 시뮬레이션 결과를 그림 3.11에서 확인할 수 있다. 앞 절에서 문제가 되었던 협대역을 보안하고자 동작 주파수를 달리하여 나타내었다.

그림 3.11 NGD1, NGD2의 전달 계수 및 군지연 특성.

Fig. 3.11 transmission and group delay characteristics of NGD1, NGD2.

그림 3.10에서 나타낸 NGD1과 NGD2의 회로도를 결합하여 그림 3.12처럼 나타내었고, 양단의 MOSFET사이의 매칭을 위 하여 양단사이에 중간층 매칭을 MIM cap을 써서 완벽한 매칭 은 아니지만, 군지연의 손실을 최소화하기 위해 사용 되었다.

그림 3.12 Cascade 구조의 기본 회로도.

Fig. 3.12 Basic network of cascade structure.

그림 3.13은 그림 3.12의 시뮬레이션 결과를 나타내었다. 그림 3.9와 비교 하였을 때, bandwidth가 확연하게 늘어남을 확인할 수 있다. 전달계수 특성은 8.4±0.8 dB(1.886 - 2.032 GHz), 군지연 특성은 -2.07±0.25 nsec(1.886 - 2.032 GHz)로 bandwidth는 146 MHz이다.

그림 3.13 Cascade 구조의 기본 회로도의 전달 계수와 군지연 특성.

Fig 3.13 Transmission and group delay characteristic of basic cascade structure.

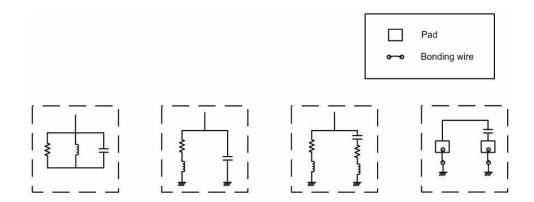

기본적으로 제안한 음의 군지연은 그림 3.14 첫 번째 회로와 같고, 본 논문에서 최종적으로 제안하는 NGD는 마지막 회로와 같다. CMOS 공정의 레이아웃에서 인덕터가 넓은 면적을 차지하며 내부 저항에 따른 삽입 손실 때문에 낮은 Q지수를 갖는다. 이러한 이유로 본 논문에서는 공정상에서 제공하는 인덕터를 쓰지 않고, 본딩 와이어(Bonding-wire)를 이용하여 구현한다. 본딩 와이어의 등가회로는 L, R이 직렬로 연결되어 있다. 이때 R값은 매우 작은 값이므로 공정상의 L보다는 상대적으로 큰 Q지수를 가질 수 있다.

그림 3.14 음의 군지연 회로도 변화순서

Fig. 3.14 NGD circuit change procedured.

앞 절에서 설명한 그림 2.1(a) Shunt-Series의 입/출력 매칭을 사용하여 넓은 반사 계수 특성을 얻을 수 있다.

T매칭단 같은 경우에는 수동소자자체에 군지연의 손실이 있지만, 제안된 매칭단 같은 경우에는 군지연의 손실이 없을 뿐만 아니라 음의 군지연 값도 가질 수 있는 매칭단이 된다.

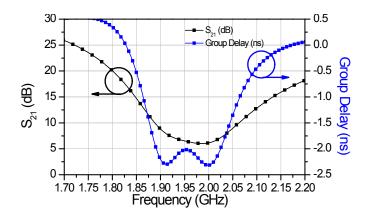

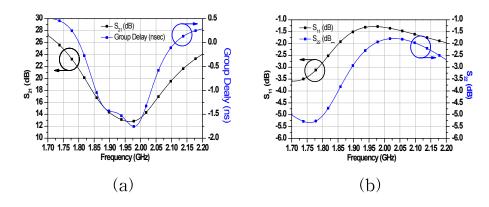

그림 3.15와 그림 3.16을 비교해보면 Shunt-Series 매칭단으로 인해 전달계수가 감소하였지만, 음의 군지연의 값, 음의 군지연의 대역폭, 각각의 반사 계수 그리고 안정도의 특성들이확연하게 좋아진 것을 그래프를 비교하여 알 수 있다.

그림 3.15 매칭된 cascade 구조 Shunt-Series의 (a) 전달 계수 및 군지연 특성, (b) 각각의 반사 계수들, (c) 안정도.

Fig. 3.15 Shunt-Series matching of cascade structure (a) transmission and group delay characteristics, (b) Each of the reflection coefficients and (c) Stability.

그림 3.16 매칭이 없는 cascade 구조 Shunt-Series의 (a) 전 달 계수 및 군지연 특성, (b) 반사 계수 특성, (c) 안정도.

Fig. 3.16 Shunt-Series without matching of cascade structure (a) transmission and group delay characteristics, (b) Each of the reflection coefficients and (c) Stability.

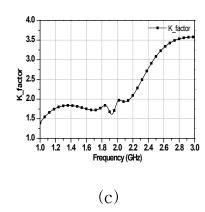

그림 3.17은 본 논문에서 제안한 구조도이다. 2개의 MOSFET을 cascade 구조를 이용하여 음의 군지연의 단점인 삽입손실을 상쇄하고 양의 전달 계수 특성을 가지도록 설계하였다. 입/출력 단에 반사 계수를 위해서 각각의 매칭 네트워크를 Shunt-Series 매칭단으로 설계하였다. 이때, 매칭은 물론이거니와 군지연의 손실 없이, 음의 군지연을 가지는 매칭단을 설계하였다.

MOSFET의 소스에 연결되어있는 수동 소자의 R과 L은 본 딩 와이어로 구현하여 회로의 사이즈를 최소화하였다. 마지막 으로 MOSFET 양단사이에 중간층 매칭과 군지연 손실을 둘다 고려하여 MIM cap을 써서 매칭과 군지연 손실을 최소화하여 설계 하였다.

그림 3.17 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연의 전체 회로도.

Fig. 3.17 Overall structure of CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance.

그림 3.18 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연의 전체 회로도의 (a) 전달 계수 및 군지연 특성, (b) 반사 계수 특성, (c) 안전도.

Fig. 3.18 Overall structure of Overall structure of CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance. (a) transmission and group delay characteristics, (b) reflection characteristics and (c) stability.

# 표 3.3 동작 주파수에서의 특성. $(V_{DD}$ =1.2 V, $V_{G}$ =0.6 V, $I_{ds}$ =11.5 mA)

Table 3.3 Characteristics of the operating frequency(1.95 GHz).

| Symbol                  | Values                 |

|-------------------------|------------------------|

| S <sub>21</sub> [dB]    | 4.55±2.6               |

| GD [nsec]               | -1.02±0.2              |

| Bandwidth [MHz]         | 244 MHz                |

|                         | (1.836 GHz ~ 2.08 GHz) |

| $S_{11} / S_{22} [dB]$  | -15.5 / -19            |

| Size [um <sup>2</sup> ] | 773 × 800              |

- 4. 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 제작 및 측정결과.

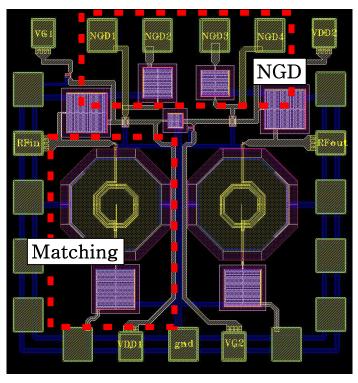

- 4.1 제안한 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 레이아웃.

그림 4.1 제안된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 layout.

Fig 4.1 Layout of proposed CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance.

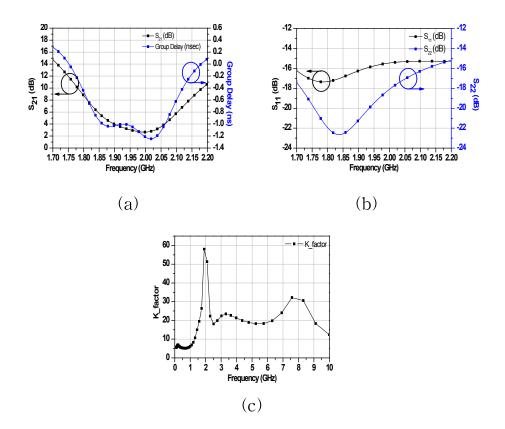

본 논문에서 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로는 동부 0.11  $\mu$ m 공정을 이용하여 제작 및 구현하였다. 이 장에서는 음의 군지연 제작을 위한 레이아웃과 제작된 회로의 측정 결과에 대하여 다룰 것이다. 그림 4.1은 설계한 레이아웃 회로의 크기는 0.78 × 0.8  $mm^2$ 이며, 본딩 패드를 포함한 전체 크기이다.

# 4.2 제안한 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 측정 및 분석.

동작 주파수 대역은 W-CDMA 상향 대역인 1.92 GHz ~ 1.98 GHz 이며, 그림 4.2는 실제 동부 0.11  $\mu$ m 공정으로 설계된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS음의 군지연 회로의 현미경 사진이다.

그림 4.2 제작된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로.

Fig 4.2 Fabricated CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance.

제작된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 입력 전력 레벨은 -10 dBm이며, 공급 전압은  $1.2~\rm V$  이며,  $V_{DD}=1.2~\rm V$ ,  $V_{G}=0.6~\rm V$ ,  $I_{ds}=11.5~\rm mA$  이다.

그림 4.3 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 (a) 전달 계수 및 군지연 특성, (b) 반사 계수 특성들.

Fig 4.3 CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance of (a) transmission and group delay characteristics, (b) reflection characteristics.

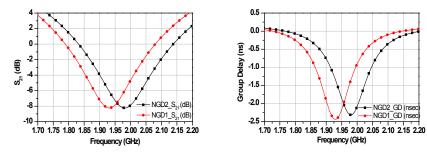

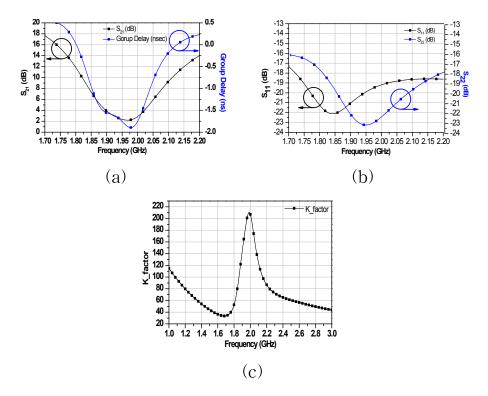

그림 4.3은 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 전달 계수와 군지연 특성이다.

측정된 특성들은 표4.1에 정리해 두었다.

표 4.1 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 특성.

Table 4.1 Characteristics of the measurement CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance(1.98 GHz).

| Symbol                  | Values                                      |  |

|-------------------------|---------------------------------------------|--|

| S <sub>21</sub> [dB]    | -2.93±1.57                                  |  |

| GD [nsec]               | $-0.8 \pm 0.2$                              |  |

| Bandwidth [MHz]         | 244 MHz                                     |  |

|                         | $(1.836 \text{ GHz} \sim 2.08 \text{ GHz})$ |  |

| $S_{11} / S_{22} [dB]$  | -16.5±2.5 / -11.25±0.75                     |  |

| Size [um <sup>2</sup> ] | 773 × 800                                   |  |

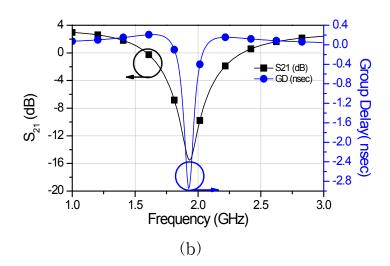

그림 4.4은 시뮬레이션과 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 전달 계 수와 군지연 특성을 비교한 그래프이다.

그림 4.4 시뮬레이션 결과와 측정 결과의 (a) 전달 계수 및 군지연 특성, (b) 반사 계수 특성들.

Fig 4.4 Simulation results with the measurement results of (a) transmission and group delay characteristics, (b) reflection characteristics.

표 4.2 측정된 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 시뮬레이션 결과 와 측정 결과 비교.

Table 4.2 Comparing the simulation results with the measurement results of CMOS negative group delay circuit using source series feedback circuit and shunt resonating resistance(1.98 GHz).

| Symbol                                 | Simulation results                           | Measurement results     |

|----------------------------------------|----------------------------------------------|-------------------------|

| S <sub>21</sub> [dB]                   | 4.7±2                                        | -2.93±1.57              |

| GD [nsec]                              | -1.025±0.225                                 | -0.8±0.2                |

| Bandwidth                              | 250                                          | 244                     |

| [MHz]                                  | $(1.832 \text{ GHz} \sim 2.082 \text{ GHz})$ | (1.836 GHz ~ 2.08 GHz)  |

| S <sub>11</sub> / S <sub>22</sub> [dB] | -16.15±0.85 / -19.55±3.05                    | -16.5±2.5 / -11.25±0.75 |

표 4.2는 본 논문에서 제안한 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로의 시뮬레이션 결과와 측정 결과를 비교한 것이다. 측정 결과가 시뮬레이션 결과에 비해 전달 계수 특성이 감소된 차이를 보이고 있다. 이것은 layout상의 MOSFET에서 제공되는 가드링을 연결하지 못하여, chip에 바이어스 인가할 때, MOSFET의 pn접합이 깨져버려서 그 현상으로 current path가 생긴다. 그로 인해 MOSFET의 pn

접합이 깨져 Drain에만 바이어스를 인가할 때 일부의 current가 흘러서 정상적인 MOSFET의 동작을 하지 못한다. 그로 인해 시뮬레이션 대비 전달 계수가 낮다.

## 5. 결론.

기존의 음의 군지연 회로는 기저대역에서 특성을 나타내었다. 하지만, 응용 프로그램이 한정적으로 바라볼 수 있다. 그리고 다른 연구 분야와 비교하여 RFIC에서 CMOS 공정을 사용하여 음의 군지연 네트워크를 설계하는 것이 첫 번째 시도로 보인다. 제안하는 소스 직렬 부궤환 회로와 단락 공진 저항을 이용한 CMOS 음의 군지연 회로는 W-CDMA 상향 대역인 1.95 GHz(1.92 GHz ~ 1.98 GHz) 대역에서 설계 되었으며, 전달 계수 특성은 -2.93±1.57 dB, 군지연 특성은 -0.8±0.2 nsec이고, 이때의 대역폭은 244 MHz(1.836 GHz ~ 2.08 GHz) 그리고 각각의 반사 계수 특성은 -11 dB 이상으로 측정 하였다.

CMOS 공정의 layout상에서 인덕터가 넓은 면적을 차지하며, 내부 저항에 따른 삽입 손실 때문에 낮은 Q지수를 갖는다. 이러한 이유로 공정상의 인덕터를 쓰지 않고, Q지수가 높은 본당 와이어(Bonding-wire)를 구현함으로 본당 인덕터의 값에따라 동작 주파수가 변하므로 동작 주파수를 정확하게 설정하지 못하였다. 그리고 레이아웃상 가드링 문제점이 되었는데, 다음 공정을 통해 미비 되었던 레이아웃상 가드링 문제와 최적화를 시켜, 이미 제작 중에 있다. 가드링 문제점을 보완한다면, 매우 우수한 음의 군지연 증폭기를 이용하여 초고주파 송,

수신 시스템의 군지연 신호를 상쇄시키는 블록에 유용하게 사용될 수 있을 것이다.

### REFERENCES

- [1] L. Brillouin, and A. Sommerfeld, Wave Propagation and Group Velocity, Academic Press Network, 1960.

- [2] Kenington P.B, Wilinson R.J., and Marvill J.D., "Power Amplification Techniques for Linear TDMA Base Station," *IEEE Global Telecommunication Conf.*, vol. 1, pp. 74–78, Dec. 1992.

- [3] M. Kitano, T. Nakanishi, K. Sugiyama, "Negative Group Delay and Superluminal Propagation: An Electronic Circuit Approach," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 9, no. 1, pp. 43–51, Jam. 2003.

- [4] S. Lucyszyn, I. D. Robertson and A. H. Aghvami, "Negative gorup delay synthesizer," *IET Electron. Lett.*, col. 29, no. 9, pp. 798–800. Apr. 1993.

- [5] Yong-Chae Jeong, Young-Jean Song, In-Ju Oh, and Chul-Dong Kim, "A Novel Adaptive Feedforward Amplifier Using an Analog Controller," *Microwave Journal*, vol. 46, no. 4, pp. 76-85, Apr. 2003.

- [6] Yong-Chae Jeong, "A Feedforward Power Amplifier with Loops to Reduce Rx Band Noise and Intermodulation Distortion," *Microwave Journal*, vol. 45, no. 1, pp. 80-91, Jan. 2002.

- [7] J. F. Woodly, et. al., "Negative group velocity and group delay in left-handed media," *Physical Review E.*, vol. 70, 2004.

- [8] D. Solli, R. Y. Chiao, "Superluminal effects and negative delays in electronics, and their application." *Physical Review E*, Issue 5, pp. 056601 1-4, Nov. 2002.

- [9] Blaise Ravelo "An FET-Based Microwave Ative Circuit with Dual-Band Negative Group Dealy," *Journal of Microwaves, Optoelectronics and Electromagnetic Application*, Vol. 10, No. 2, pp. 355–366. Dec. 2011.

- [10] David M. Pozar, *Microwave engineering*, Third Edition, John Wiley & Sons, N.Y., 1998.

- [11] H. Choi, Y. Jeong, C. D. Kim, and J. S. Kenney, "Efficiency enhancement of feedforward amplifiers by employing a negative group delay circuit", *IEEE Tran. Microwave Theory Tech.*, vol. 58, no. 5, pp. 1116–1125, May. 2010.

- [12] David M. Pozar, *Microwave engineering*, Third Edition, John Wiley & Sons, N.Y., 1998.

- [13] Guillermo Gonzalez, Microwave Transistor Amplifiers Analysis and Design, 2nd ed. Prentice Hall, Inc. 1984.

- [14] S. C. Cripps, *RF power amplifiers for wireless communications*, 2nd ed. Artech House, Inc. 2006.

- [15] Heungjae Choi, Kyungju Song, Chul Dong Kim, and Yongchae Jeong, "Synthesis of Negative Group Delay Time Circuit," *Asia Pacific Microwave Conference Proceeding*, B5–08. Dec. 2008.

- [16] Heungjae Choi, Yonggyu Kim, Yongchae Jeong, and Chul Dong Kim, "Synthesis of Reflection Type Negative Group Delay Circuit Using Transmission Line Resonator," *Europeon Microwave Conference*. pp. 902–905. Sep. 2009.

- [17] B. Ravelo, A. Perennec, and M. Le Roy, "Synthesis of Broadband Negative Group Delay Active Circuits," in *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 2177–2180, Jun. 2007.

- [18] H. Noto, K. Yamauchi, M. Nakayama, and Y. Isota, "Negative Droup Delay Circuit for Feed-Forward Amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 1103–1106, June, 2007.

- [19] H. Choi, Y. Jeong, C. D. Kim, and J.S. Kenney, "Bandwidth enhancement of an analog feedback amplifier by employing a negative group delay ircuit," *Progress In Electromagnetics Research*, vol. 105, 253–272, 2010.