# CMOS 가변이득을 가지는 NB-IoT용 이중대역 저잡음 증폭기 설계

2018년 2월 22일

전 북 대 학 교 대 학 원

전 자 정 보 공 학 부

구 자 건

# CMOS 가변이득을 가지는 NB-IoT용 이중대역 저잡음 증폭기 설계

A Design of NB-IoT Dual Band CMOS Low Noise Amplifier with Variable Gain

2018년 2월 22일

전 북 대 학 교 대 학 원

전자정보공학부

구 자 건

# CMOS 가변이득을 가지는 NB-IoT용 이중대역 저잡음 증폭기 설계

지도교수 정 용 채

이 논문을 공학 석사 학위논문으로 제출함.

2017년 11월 06일

전 북 대 학 교 대 학 원

전자정보공학부

구 자 건

### 구자건의 석사학위논문을 인준함.

| 위원장 | 전북대학교 | 교수 | 임 동 구 | (인) |

|-----|-------|----|-------|-----|

| 위원  | 전북대학교 | 교수 | 손 해 원 | (인) |

| 위원  | 전북대학교 | 교수 | 정 용 채 | (인) |

2017년 12월 15일

전 북 대 학 교 대 학 원

### 목 차

#### ABSTRACT

| 1. | 서론                                      | . 1 |

|----|-----------------------------------------|-----|

| 2. | 저잡음 증폭기 이론                              |     |

|    | 2.1 잡음 지수                               | . 3 |

|    | 2.2 비선형 특성                              | . 5 |

|    | 2.3 CMOS MOSFET의 잡음 모델                  | . 7 |

|    | 2.4 저잡음 증폭기                             | 10  |

| 3. | 제안하는 가변이득 저잡음 증폭기 설계                    |     |

|    | 3.1 저잡음 증폭기 시뮬레이션                       | 21  |

|    | 3.2 제안된 저잡음 증폭기                         | 25  |

|    | 3.3 제안된 가변이득 증폭기                        | 29  |

|    | 3.4 제안된 저잡음 가변이득 증폭기                    | 35  |

|    | 제안된 CMOS 가변이득을 가지는 저잡음 증폭기의 제작 및<br>정결과 | ]   |

|    | 4.1 제안된 CMOS 가변이득 저잡음 증폭기의 레이아웃         | 41  |

|    | 4.2 제안하는 CMOS 가변이득 저잡음 증폭기의 측정 결과       | 43  |

| 5. | 결론                                      | 50  |

| 6. | 참고무헌                                    | 52  |

### 그 림 목 차

| 그림 | 1.1 세계 IoT 시장 성장 추이                        | 1  |

|----|--------------------------------------------|----|

| 그림 | 1.2 무선 통신 송수신 시스템                          | 2  |

| 그림 | 2.1 직렬로 연결된 시스템                            | 4  |

| 그림 | 2.2 MOSFET의 채널                             | 8  |

| 그림 | 2.3 공통 소스 저잡음 증폭기                          | 11 |

| 그림 | 2.4 공통 소스 저잡음 증폭기의 잡음 모델                   | 12 |

| 그림 | 2.5 Shunt-shunt 부궤한 저잡음 증폭기                | 14 |

| 그림 | 2.6 공통 게이트 저잡음 증폭기                         | 16 |

| 그림 | 2.7 공통 게이트 저잡음 증폭기의 잡음 모델                  | 17 |

| 그림 | 2.8 소스 축퇴 저잡음 증폭기                          | 18 |

| 그림 | 2.9 게이트 단에 인덕터를 추가한 소스 축퇴 저잡음 증폭기          | 19 |

| 그림 | 3.1 소스 축퇴 저잡음 증폭기                          | 21 |

| 그림 | 3.2 소스 축퇴 저잡음 증폭기의 시뮬레이션 결과                | 22 |

| 그림 | 3.3 공통 게이트 저잡음 증폭기                         | 23 |

| 그림 | 3.4 공통 게이트 저잡음 증폭기의 시뮬레이션 결과               | 23 |

| 그림 | 3.5 Shunt-shunt feedback 저잡음 증폭기           | 24 |

| 그림 | 3.6 Shunt-shunt feedbakc 저잡음 증폭기의 시뮬레이션 결과 | 24 |

| 그림 | 3.7 인버터 구조의 저잡음 증폭기                        | 25 |

| 그림 | 3.8 제안하는 저잡음 증폭기의 회로도                      | 26 |

| 그림 | 3.9 다중게이트 회로의 동작 원리                        | 27 |

| 그림 | 3.10 포화 영역에서의 g3 상쇄 기법                     | 27 |

| 그림 | 3.11 MOSFET 조정 가변 이득 증폭기                   | 30 |

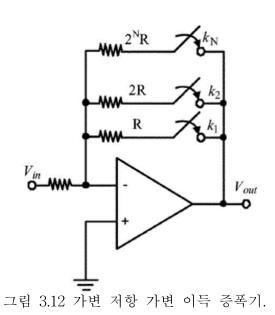

| 그림 | 3.12 가변 저항 가변 이득 증폭기                       | 30 |

| 그림 | 3.13 Current steeling 회로를 이용한 가변 이득 증폭기    | 31 |

| 그림 | 3.14 Cascode 증폭기                         | 32  |

|----|------------------------------------------|-----|

| 그림 | 3.15 Current steering 회로                 | 34  |

| 그림 | 3.16 출력저항에 따른 입력 임피던스의 변화                | 34  |

| 그림 | 3.17 전압에 따른 입력 임피던스의 변화                  | 34  |

| 그림 | 3.18 제안하는 가변 이득을 가지는 저잡음 증폭기             | 35  |

| 그림 | 3.19 Current steering 회로                 | 36  |

| 그림 | 3.20 제안하는 저잡음 증폭기의 시뮬레이션 결과              | 36  |

| 그림 | 3.21 제안하는 가변 이득 증폭기의 S21 특성(1단)          | 37  |

| 그림 | 3.22 제안하는 가변 이득 증폭기의 S21 특성(3단)          | 37  |

| 그림 | 3.23 제안하는 가변 이득 증폭기의 선형성 특성              | 38  |

| 그림 | 3.24 제안하는 가변이득 저잡음 증폭기의 S21 시뮬레이션 결과     | 40  |

| 그림 | 3.25 제안하는 가변이득 저잡음 증폭기의 잡음 지수 시뮬레이션 결과 . | 40  |

| 그림 | 4.1. 제안하는 회로의 레이아웃                       | 41  |

| 그림 | 4.2. 제안하는 회로의 실제 사진                      | 43  |

| 그림 | 4.3. 제안하는 회로의 S21 측정 결과                  | .44 |

| 그림 | 4.4. 제안하는 회로의 삽입손실 특성                    | 44  |

| 그림 | 4.5. 제안하는 회로의 잡음지수 측정 결과                 | 45  |

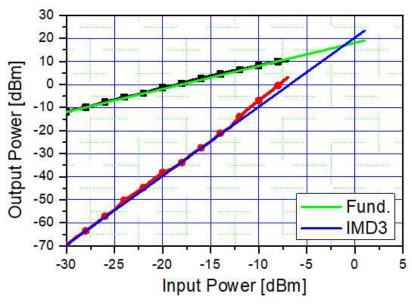

| 그림 | 4.6. 제안하는 회로의 선형성 측정결과(저주파 대역)           | 47  |

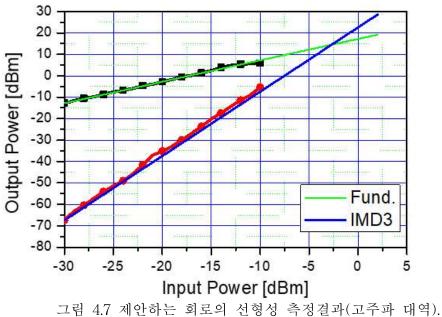

| 그림 | 47 제안하는 히루의 서형성 측정결과(고주파 대역)             | 47  |

### 표 목 차

| 丑 | 2.1 | 저잡음 증폭기의 | 비교 |            | 20 |

|---|-----|----------|----|------------|----|

| 丑 | 4.1 | 제안하는 회로의 | 이득 | 특성(저주파 대역) | 48 |

| 丑 | 4.2 | 제안하는 회로의 | 이득 | 특성(고주파 대역) | 48 |

| 丑 | 4.3 | 제안하는 회로의 | 특성 | 정리         | 49 |

| 丑 | 4.4 | 기존 논문들과의 | 회로 | 비교         | 49 |

#### **ABSTRACT**

# A Design of NB-IoT Dual Band CMOS Low Noise Amplifier with Variable Gain

Jageon Koo

Department of Electronics and Information Engineering

Chonbuk National University

Since RFIC CMOS technology is a good candidate among the circuit miniaturization methods, a research study on the implementation of RF Front-end circuits using CMOS technology is essential. In this paper presents the design of NB-IoT dual band CMOS low noise amplifier with variable gain. Proposed low noise amplifier is designed to the inverter-based resistive feedback amplifier and multiple gate technic is appled for high linearity. Also, variable gain amplifier is design with cascode amplifier and current steeling circuit is applied for the varied the gain. The proposed circuit was implemented in the TSMC 0.18 RF CMOS process. The circuit size is  $400 \times 260 \ \mu \text{m}^2$ without the bonding pad. The measurement results shown that the gain, gain step, and noise figure are 17 dB, 2 dB, and less than 2 dB, respectively, at the operating frequency of 729 ~ 960 and 1805  $\sim 2170$  Mhz. In the range of 729  $\sim 960$  MHz at the low band, the output P1dB and OIP3 are 11 dBm and 16 dBm, respectively. In the range of 1805 ~ 2170 Mhz at the high band the output P1dB and OIP3 are 7 dBm and 14 dBm, respectively.

Keywords: CMOS integrated circuits, low noise amplifier, variable gain amplifier.

#### 1. 서 론

향후 IT 분야의 최고 화두는 단연 '무선 센서 네트워크'(wireless sensor network)라고 할 수 있다. 이러한 기술은 사람과 사물, 사물과 사물이 언제, 어디서나 하나로 연결되는 무선 센서 네트워크이며 시공을 넘나드는 정보 교환을 이상적으로 수행 할 수 있도록 하는 컴퓨팅 네트워크라고도할 수 있다. 최근 들어 무선 센서 네트워크는 온/습도 과닐와 같은 단순한 기능의 저전력 모니터링 서비스에서 의료 서비스, 해안의 지진, 수질오염 및 산부 감시 모니터링 시스템, 스마트 그리드, 스마트 빌딩과 같은 높은 신뢰성 및 넓은 통신 영역이 요구되는 서비스 영역까지 확장되고 있다. 그 응용 분야 및 경제 효과는 무궁무진 하지만, 이를 현실화하기 위해서는 센서 시스템의 높은 전력 소모 및 소형화 기술 및 가격을 반드시 줄여야 한다. 특히, 전체 전력 소모 중 50~85%는 무선 전송을 위한 라디오에서 소모되고 있기에 극소 전력을 소모하는 초저가 초소형 라디오 개발이 필수적이다.

이러한 무선 센서 네트워크의 발달과 함께 LTE(Long Term Evolution) 주파수를 기반으로 한 NB-IoT(NarrowBand-Internet of Things)가 큰 성장을 이루고 있다. 그림 1.1은 세계 IoT 시장 성장 추이를 나타내고 있으며, 이 그래프를 통해서 IoT 기술은 연평균 26%씩 고성장 하며 2020년에는 1조불 규모를 상회할 것으로 예측되어진다. 이에 맞춰서 국내 IoT 시장도 22년까지 연평균 29.1 %의 고 성장세를 유지하여 시장규모가 약 22조원을 상회할 것으로 전망되어지고 있다.

그림 1.1 세계 IoT 시장 성장 추이.

Fig. 1.1 Global IoT market growth trend.

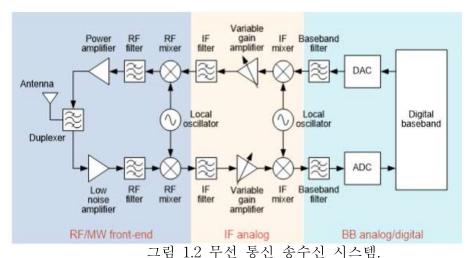

무선통신 시스템에서 사용되는 송수신 시스템은 그림. 1.2와 같이 나타 낼 수 있다. 이 중에 수신기에서 가장 큰 전력을 소모하고 주요 성능을 결정짓는 부분은 고주파 전단부(RF Front-end) 부분인 저잡음 증폭기 (Low noise amplifier)와 믹서(Mixer) 블록이다. 이러한 고주파 전단부에서는 고효율 및 고선형성을 요구한다. 또한 무선 전단부 뒤에 오는 회로보호를 위해서 동적 입력 신호 범위에 대해서 일정한 출력 전력을 제공하여야 한다. 이러한 조건 및 은 면적과 전력소모량의 요구에 따라 무선전단부를 Monolithic Microwave Integrated Circuit (MMIC) 또는 RF Integrated Circuit (RFIC)로 구현하는 연구가 활발히 이루어지고 있다[1]-[5]. 이러한 무선 전단부에서는 낮은 잡음 지수(Noise Figure)를 요구하며 회로 전체의 잡음 지수는 프리스 공식(Friis's equation)에 의해서 저잡음 증폭기에 가장 큰 영향을 받게 된다[6]. 또한 NB-IoT대역에서 사용되어지는 저잡음 증폭기는 높은 감도(Sensitivity)를 얻기 위해서 높은 이득(Gain)과 3 dB 미만의 잡음 지수를 가지고 있어야 한다.

본 논문에서는 가변이득을 가지는 NB-IoT용 이중대역 저잡음 증폭기설계에 대해서 연구하였다. 제시된 회로는 2 dB 미만의 낮은 잡음 지수와 2 dB 간격으로 가변이득을 가진다.

Fig. 1.2 Block diagram of RF transceiver system.

#### 2. 저잡음 증폭기 이론

#### 2.1 잡음지수

무선 통신 송수신 시스템에서 사용되어지는 증폭기는 크게 수신단의 저잡음 증폭기와 송신단의 전력증폭기(Power Amplifier)로 나눌 수 있다. 이중에서 수신단에 사용되어지는 저잡음 증폭기의 경우 가장 중요한 특성은 낮은 잡음지수를 가지는 것이다. 잡음지수는 어떤 시스템이나 회로 블럭을 신호가 통과하게 된다면, 얼마나 잡음이 추가되어지느냐를 나타내는 지표이다. 이러한 잡음지수는 신호 대 잡음비율(SNR: Signal to noise ration)을 가지고 계산을 할 수 있다[6].

$$SNR = \frac{Signal \, Power}{Noise \, Power} \tag{2.1}$$

SNR이란 신호 대 잡음비율을 의미하는 지표이며, 어떤 회로나 시스템을 신호가 통과하고 나면 항상 잡음이 늘어나기 때문에 출력 SNR은 입력 SNR보다 항상 작아지게 된다. 여기서 출력 SNR 대 입력 SNR의 비로 나타내게 되면 이것을 Noise Factor라 불리게 된다.

Noise Factor

$$(F) = \frac{SNR_{in}}{SNR_{out}}$$

(2.2)

여기서 구한 Noise Factor는 이상적인 증폭기에서는 1을 가지게 되지만 실제 회로에서는 1보다 큰 값을 가지며, Noise Factor를 dB 값으로 환산 을 하게 되면 이것을 잡음 지수(Noise Figure)라고 한다.

Noise Figure (NF) =

$$10\log F = 10\log \frac{SNR_{in}}{SNR_{out}}$$

(2.3)

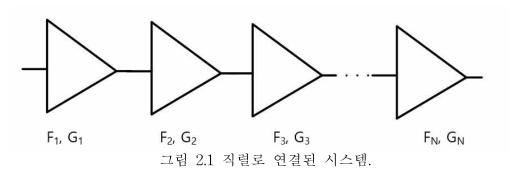

그림 2.1은 직렬(cascade)로 연결된 회로의 시스템 블록을 나타낸다. 이 러한 경우의 최종 출력 단에서의 잡음 지수는 아래의 수식을 통하여 계산 할 수 있다.

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \bullet \cdot \bullet + \frac{F_N - 1}{G_1 G_2 \cdot \bullet \cdot \bullet G_{N-1}}$$

(2.4)

식 (2.4)를 통해서 알 수 있듯이 최종 출력단의 잡음 지수는 첫 번째 단의 잡음지수에 의해서 가장 큰 영향을 받게 되고, 첫 번째 단의 전력이득이 크다면 두 번째 항의 값은 작아지게 되면서 잡음 지수에 큰 영향을 미치지 않게 된다. 그렇기 때문에 수신단 설계에 있어서 저잡음 증폭기는 최대한 낮은 잡음지수 및 큰 전력이득을 가지고 있어야 하며, 잡음지수를 줄이는 것이 무선 수신기의 수신감도를 결정하는 중요한 요소가 된다.

Fig. 2.1 Block diagram of cascade system.

#### 2. 2 비선형 특성

2단자 회로망에서 회로의 메모리(Memory) 부분을 무시한다면 회로의 입력과 출력의 관계는 동시성을 가진다. k라는 이득을 가진 증폭기에 입력 V가 통과를 하게 된다면 아래와 같은 식으로 나타낼 수 있다.

$$V_0 = k V_i \tag{2.5}$$

하지만 이것은 이상적인 환경에서의 입출력 관계이며, 실제 증폭기는 입력과 출력은 선형적인 관계를 가지고 이것을 수식적으로 표현하면 다음 과 같이 나타낼 수 있다.

$$V_0 = k_1 V_i + k_2 V_i^2 + k_3 V_i^3 + \dots (2.6)$$

위 두 식에서는 입력에 따른 출력의 위상 왜곡 특성은 고려하지 않았다. 하지만 강한 비선형 특성을 가지지 않는 회로에 대해서는 세 번째 항까지만 고려를 할 수 있다.

$$V_o = k_1 V_i + k_2 V_i^2 + k_3 V_i^3 \tag{2.7}$$

이때 입력 신호를  $V_i = A cos \omega_1 t$ 라 가정한다면 식(2.7)은 다음과 같이 나타낼 수 있다.

$$\begin{split} V_o &= k_1 (A cos \omega_1 t) + k_2 (A cos \omega_1 t)^2 + k_3 (A cos \omega_1 t)^3 \\ &= \frac{1}{2} k_2 A^2 + \left( k_1 A + \frac{3}{4} k_3 A^3 \right)_{\cos \omega_1 t} + \frac{1}{2} k_2 A^2_{\cos 2\omega_1 t} + \frac{1}{4} k_3 A^3_{\cos 3\omega_1 t} \end{split} \tag{2.8}$$

식 (2.8)을 통해 1-tone 신호가 증폭기에 인가되게 된다면 1-tone 주파수의 정수배의 신호가 동반되는 사실을 알 수 있다.  $k_3$ 가 음의 값을 가지게 된다면 출력은 선형 출력  $k_1A$ 의 값보다 감소하게 되므로 이득의 감소 또는 AM-to-AM 특성이라 할 수 있다. 또한 입력의 크기에 따른 출력의 위상 특성이 변화하는 것을 알 수 있는데 이것은 AM-to-PM 특성으로 볼 수 있으며 수식으로 나타내면 다음과 같다.

$$a = \frac{180}{\pi} \frac{d\theta_p}{d(10\log P_{in})} \tag{2.9}$$

여기서  $P_{in}$ 은 증폭기에 인가되는 입력 전력을 뜻하며  $\theta_p$ 은 입력 전력의 변화에 따른 위상변화, a는 입력에 대한 출력 상대 위상의 변화 정도를 나타낸다.

이러한 비선형 특성을 가지는 증폭기에 진폭이 같은  $V_i = A(\cos \omega_1 t + \cos \omega_2 t)$ 의 신호를 인가하게 되면 출력 신호는 다음과 같이 표현 할 수 있다.

$$\begin{split} V_o &= k_2 A^2 + k_2 A^2 \cos \left(\omega_1 - \omega_2\right) t + \left(k_1 A + \frac{9}{4} k_3 A^3\right) \cos \omega_1 t + \left(k_1 A + \frac{9}{4} k_3 A^3\right) \cos \omega_2 t \\ &+ \frac{3}{4} k_3 A^3 \cos \left(2\omega_1 - \omega_2\right) t + \frac{3}{4} k_3 A^3 \cos \left(2\omega_2 - \omega_1\right) t + k_2 A^2 \cos \left(\omega_1 + \omega_2\right) t \\ &+ \frac{1}{2} k_2 A^2 \cos 2\omega_1 t + \frac{1}{2} k_2 A^2 \cos 2\omega_2 t + \frac{3}{4} k_3 A^3 \cos \left(2\omega_1 + \omega_2\right) t \\ &+ \frac{3}{4} k_3 A^3 \cos \left(2\omega_2 + \omega_1\right) t + \frac{1}{4} k_3 A^3 \cos 3\omega_1 t + \frac{1}{4}$$

위의 식을 통해서  $2\omega_1$ ,  $2\omega_2$ ,  $3\omega_1$ ,  $3\omega_2$ 의 신호가 나오는 것을 확인 할 수있고 추가적으로  $\omega_1 \pm \omega_2$ ,  $2\omega_1 \pm \omega_2$ ,  $2\omega_1 \pm \omega_1$ 의 성분들이 나오는 것을 알 수있다. 이러한 성분을 혼변조 성분(Intermodulation distortion: IMD) 이며, 무선 통신 시스템에서 인접 채널에 영향을 주게 된다. 이러한 출력 성분들은 대부분 증폭기 출력단에 달리는 여파기를 통해서 충분히 제거를 할수 있지만,  $2\omega_1 \pm \omega_2$ ,  $2\omega_1 \pm \omega_1$ 와 같은 3차 혼변조(IMD3) 성분들은 여파기를 사용하여서 제거하기 어려우며[7], 이러한 3차 혼변조 시스템을 최대한 낮추게 된다면 고선형 증폭기를 설계를 할 수 있다.

#### 2. 3 CMOS MOSFET의 잡음 모델

CMOS를 이용한 저잡음 증폭기 설계를 하기 위해서는 MOSFET의 잡음 모델 분석이 이루어져야 한다. CMOS에서 사용되어지는 MOSFET의 잡음 소스(Noise Source)는 다음과 같다[8].

- 1. 채널내의 열 잡음(Thermal noise)

- 2. 플리커 잡음(Flicker Noise)

- 3. 저항성 폴리 게이트의 잡음

- 4. 기판의 기생저항에 의한 잡음

- 5. 역방향 다이오드의 누설 전류에 의한 샷 노이즈(Shot noise)

실제 회로설계에 있어서는 1번과 2번에 의한 잡음이 가장 많이 발생하게 된다.

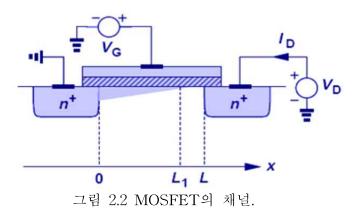

MOSFET의 게이트(Gate)에 전압이 걸리게 되면 MOSFET의 Psub에 있던 전자들이 전류가 흐를 수 있는 통로인 채널을 형성하게 되며 소스와 드레인의 전위차가 나지 않을 경우, 채널은 균질 저항으로 처리 될 수 있다. 이 경우 채널의 잡음은 식(2.10)과 같이 표현 할 수 있다.

$$i_d^2 = 4kTg_0 (2.10)$$

k: 볼츠만 상수(Boltzman constant),

T: 절대온도(Absolute temperature),

g<sub>0</sub>: 채널상수(@ V<sub>ds</sub>=0)

일반적으로 드레인 소스 전압은 OV보다 높고, 채널은 드레인 근처보다 소스 근처에서 전도성이 더 높아지게 된다. 결론적으로 채널은 균질 저항 이 아니게 되며, 잡음 지수를 계산하기 위해서는 채널을 아주 미세한 부 분으로 나눈 뒤 각 채널에서 생기는 잡음을 적분 식을 통해서 계산하여야 한다.

$$i_d^2 = 4kT \frac{\mu^2 W^2}{L^2 I_{DS}} \int_0^{V_{DS}} Q_n^2(V) dV$$

(2.11)

W: MOSFET의 channel width,

L: MOSFET의 channel length,

μ: Effective chaneel mobility,

$I_{DS}$ : 드레인 소스 전류

$Q_n(x)$ 의 식은 다음과 같이 표현 할 수 있다.

$$Q_n(x) = C_{ox}(V_{GS} - V_T(x) - V(x))$$

(2.12)

$C_{ox}$  게이트와 산화막(Oxide) 사이의 단위 커패시턴스,

$V_{7}(x)$ : x지점의 문턱 전압

V(x): 채널 전압

또한 MOSFET의 동작 영형은 linear region  $(V_{DS} < V_{GS} - V_T)$ , saturation point  $(V_{DS} = V_{GS} - V_T)$ , 그리고 saturation region  $(V_{DS} > V_{GS} - V_T)$ 로 나눌 수 있으며, saturation region에서의 MOSFET의 잡음 식은 다음과 같이 표현 할 수 있다.

$$i_d^2 = 4kt \frac{2}{3}\mu C_{ox} \frac{W}{L} (V_{GS} - V_T) = 4kT \frac{2}{3}g_m \qquad (2.13)$$

$g_m$ : MOSFET의 transconductance

Fig. 2.2 Channel of MOSFET.

하지만 위 식은 기판(Substrate)효과를 무시하고 순수한 채널의 열 잡음을 나타내며 실제 열 잡음은 기판에 의한 잡음까지 추가되므로 더 높은 값을 가지게 된다. 따라서 기판의 잡음까지 추가하여서 MOSFET의 열 잡음을 계산하게 되면 다음과 같은 식으로 표현을 할 수 있다.

$$i_d^2 = 4kt\gamma g_m \tag{2.14}$$

$\gamma$  값은 트랜지스터의 파라미터와 바이어스 조건에 의해서 결정되어 진다.  $\gamma$  값을 결정하기 위해서는 수치적 접근(Numerical approach)이 필요하며, 일반적인 CMOS  $0.18~\mu{\rm m}$  공정에서의  $\gamma$  값은 약 0.67에서 1 사이의 값을 가지게 된다.

플리커 노이즈는 능동 소자가 가지고 있는 고유의 잡음으로서, 주파수에 반비례하기 때문에 1/f로도 불리게 된다. 또한 MOS 트랜지스터는 표면 전도(surface conduction) 메커니즘으로 인해서 모든 능동 반도체 중에서 가장 높은 플리커 노이즈를 가지게 된다. MOSFET의 플리커 노이즈는 다음과 같은 식으로 표현할 수 있다.

$$Flickernoise = \frac{K}{C_{ox}WLf}$$

(2.15)

#### 2. 4 저잡음 증폭기

저잡음 증폭기는 수신기 첫 단에 위치하기 때문에 뒷 단의 연결되는 회로의 잡음 영향을 최소화하기 위해서 최소한의 잡음과 충분한 이득을 가져야 한다. 또한 큰 신호에 대한 왜곡(Distortion)이 작아야 하며, 신호가최대로 통과 할 수 있도록 입출력 정합이 필요하다. 따라서 저잡음 증폭기를 설계함에 있어서 주요 고려사항은 다음과 같이 나타낼 수 있다.

- 1. 낮음 잡음 지수

- 2. 높은 이득(*S*<sub>21</sub>)

- 3. 임피던스 정합(S<sub>11</sub>, S<sub>22</sub>)

- 4. 높은 선형성(P<sub>1dB</sub>, IIP3)

- 5. 낮은 전력소모

하지만 이 모든 조건들은 서로가 trade-off 관계를 이루므로 적절한 최 적화를 필요로 한다. 이 중에서도 입력 단을 50 Ω에 정합을 시키면서 낮 은 잡음지수와 전력소모를 가지게 하는 것이 중요한다. 본 절에서는 저잡 음 증폭기의 몇 가지 토플로지(Topology)에 대해서 설명한다.

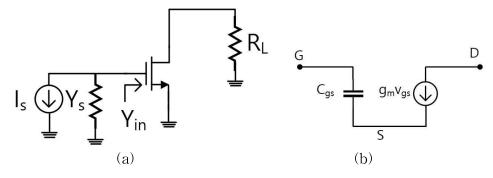

#### (1) Common-Source LNA

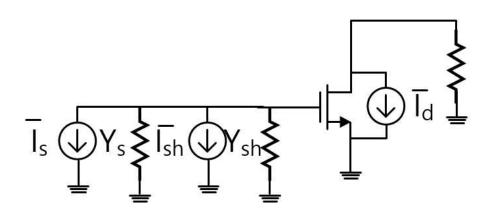

그림 2.3은 common-source 저잡음 증폭기의 회로도 및 소신호 등가 모델이다. 입력단은  $50~\Omega$  정합을 하기 위해서 입력단에서 들여다 본 어드미턴스 값은  $Y_s = Y_{in}$ 의 조건을 만족하여야 한다. 협대역 정합을 하기 위해서는 게이트 앞단에 인덕터를 사용하여 정합을 하며,

$$Y_{in} = \frac{1}{R_{sh}} + j \left( \omega C_{gs} - \frac{1}{\omega L_{sh}} \right) = \frac{1}{R_{sh}} = \frac{1}{50} \quad \text{at} \quad \omega_0^2 = \frac{1}{L_{sh} C_{gs}}$$

(2.16)

광대역 정합을 하기 위해서는 게이트 앞단에  $50~\Omega$  저항을 사용하여서 정합을 하게 되며 이 경우  $\frac{1}{R_{\perp}}\gg\omega C_{gs}$  라고 가정한다.

$$Y_{in} = \frac{1}{R_{sh}} + j\omega C_{gs} \approx \frac{1}{R_{sh}} = \frac{1}{50}$$

(2.17)

잡음 지수를 계산할 때에는 게이트에 사용한 저항 및 MOSFET에 잡음 소스를 삽임 함으로써 계산을 할 수 있다. 잡음 모델을 포함한 common-source 저잡음 증폭기의 회로도는 그림 2.4와 같이 표현 할 수 있다. 이 회로도를 이용하여서 잡음 지수를 계산하게 되면 다음과 같이 나타날 수 있다.

그림 2.3 공통 소스 저잡음 증폭기: (a)회로도와 (b) 소신호 등가회로.

Fig. 2.3 Common source LNA: (a)schematic and (b)small signal model.

$$\overline{i_{o,s}^2} = \overline{i_o^2} \frac{g_m^2}{(G_s + G_{sh})^2}$$

Shunt 저항에 의한 잡음은

$$\overline{i_{o,sh}^2} = \overline{i_{sh}^2} \frac{g_m^2}{\left(G_s + G_{sh}\right)^2}$$

이며, MOSFET에 의한 잡음은 다음과 같은 식으로 나타낼 수 있다.

$$\overline{i_{o,d}^2} = \overline{i_d^2}$$

또한 각 전류원의 잡음은 다음과 같은 식으로 나타낼 수 있다.

$$\begin{split} \overline{i_s^2} &= 4kTG_s \triangle f \\ \overline{i_{sh}^2} &= 4kTG_{sh} \triangle f \\ \overline{i_d^2} &\approx 4kT\gamma g_m \triangle f \end{split}$$

그림 2.4 공통 소스 저잡음 증폭기의 잡음 모델.

Fig. 2.4 Noise model of common source LNA.

여기서 입력 정합이 되어있다면  $G_s$ = $G_{sh}$ 이다. 위에서 구한 식을 가지고 최종 적인 잡음 값을 계산하면 다음과 같다.

$$F = 1 + \frac{\overline{i_{o,sh}^2}}{\overline{i_{o,s}^2}} + \frac{\overline{i_{o,d}^2}}{\overline{i_{o,s}^2}} = 1 + 1 + \frac{\overline{i_d^2}}{\overline{i_s^2} \frac{g_m^2}{\left(G_s + G_{sh}\right)^2}} = 2 + \frac{\overline{i_d^2}}{\overline{i_s^2} \frac{g_m^2}{\left(G_s + G_{sh}\right)^2}}$$

위 식에서 출력단의 로드 저항은 noiseless로 가정을 하였으며, 게이트 폴리 저항에 의한 잡음은 편의상 고려하지 않았다. 위의 식으로부터 저잡음 증폭기의 noise factor은 다음과 같은 식으로 표현할 수 있으며,

$$F = 2 + 4\gamma \frac{G_s}{g_m} = 2 + \frac{4\gamma}{g_m R_s} \tag{2.18}$$

저잡음 증폭기의 이득은 다음과 같이 표현할 수 있다.

$$A = -g_m R_L \left( \frac{R_{sh}}{R_s + R_{sh}} \right) = \frac{-g_m R_L}{2} \tag{2.19}$$

Common-source 저잡음 증폭기의 경우 입력단의 shunt 저항으로 인해서 광대역 정합을 할 수 있어서 광대역 설계에 적합하다. 하지만 높은 잡음 지수와 입력단에 연결되어 있는 shunt 저항에 의해서 입력 신호가 감소하고 잡음이 증가하는 것을 알 수 있다.

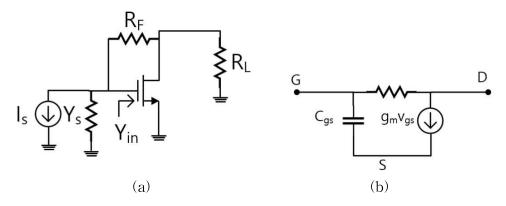

#### (2) Shunt-Shunt Feedback LNA

그림 2.5는 shunt 부궤한 저잡음 증폭기의 회로도 및 소신호 등가 모델이다. 이 경우에도 입력 정합이 되어 있어야 하므로 입력단에서 들여다본 임피던스 값이  $50\ \Omega$ 이 되어야 한다. 협대역 정합을 위해서는 입력단에 인던터를 연결하여 MOSFET의 기생 커패시터( $C_{gs}$ )와 공진을 시키게된다. 이 경우 입력 어드민터스는,

$$Y_{in} = \frac{1 + g_m R_L}{R_F + R_L} + j \left( \omega \, C_{gs} - \frac{1}{\omega L_{sh}} \right) = \frac{1 + g_m R_L}{R_F + R_L} = \frac{1}{50}$$

광대역 정합을 위해서는  $(1+g_mR_{\!\scriptscriptstyle L})/(R_{\!\scriptscriptstyle F}+R_{\!\scriptscriptstyle L})\!\gg\omega C_{\!\scriptscriptstyle as}$ 가정하면,

$$Y_{in} = \frac{1 + g_m R_L}{R_F + R_L} = \frac{1}{50}.$$

여기서  $R_F\gg R_s, R_F\gg R_L, g_mR_F\gg 1$ 이라 가정하면, 저잡음 증폭기의 잡음 지수는 다음과 같이 계산 될 수 있다.

그림 2.5 Shunt-shunt 부궤한 저잡음 증폭기: (a)회로도와 (b) 소신호 등가회로.

Fig. 2.5 Shunt-shunt feedback LNA: (a)schematic and (b)small signal model.

$$F > 1 + \frac{R_s}{R_F} \left( 1 + \frac{1}{g_m R_s} \right)^2 + \frac{\gamma}{g_m R_s} \tag{2.20}$$

또한 저잡음 증폭기의 이득은 다음과 같이 표현할 수 있다.

$$A = -g_m(R_F \parallel R_L) \tag{2.21}$$

shunt-shunt feedback 저잡음 증폭기의 경우 부하 저항이 입력 정합에 영향을 미치며 피드백 저항으로 인하여 추가 잡음을 발생 시킨다. 또한 높은 주파수에서 사용하기 위해서는  $C_{gs}$ 값을 상쇄시키기 위해서 shunt 인덕터가 필요하다. 하지만 낮은 주파수대역에서 광대역 증폭기로 사용하기용이하다. 또한 잡음을 최소화하기 위해서는  $R_F\gg R_s, g_mR_F\gg 1$  조건을 만족하여야 한다.

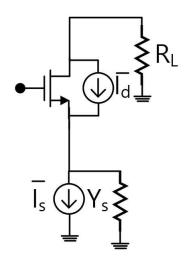

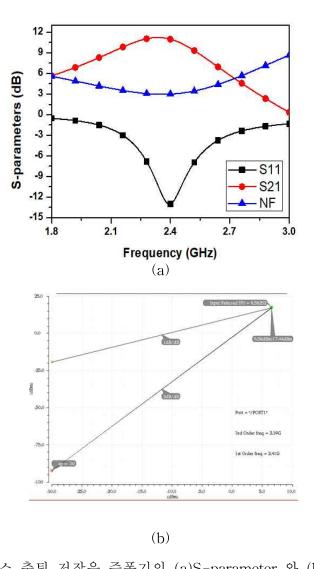

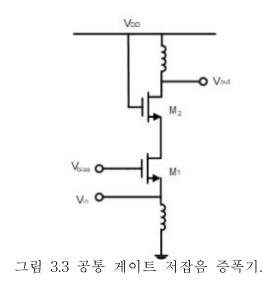

#### (3) Common-Gate LNA

공통 게이트 저잡음 증폭기의 경우 게이트 단에 DC 바이어스만을 연결하고 입력을 소스단에서 인가한다. 회로의 입력 어드미턴스는  $g_m\gg\omega C_{gs}$ 를 가정하면 다음과 같이 표현 할 수 있다.

$$Y_{in} = g_m = \frac{1}{50}$$

그림2.7은 잡음 모델을 추가한 회로도이다. 이 회로를 각 잡음 소스가 생성하는 잡음을 계산하면,

그림 2.6 공통 게이트 저잡음 증폭기: (a)회로도와 (b) 소신호 등가회로. Fig. 2.6 Common-Gate LNA: (a)schematic and (b)small signal model.

위 식을 통해서 회로의 잡음을 계산하면,

$$F pprox 1 + rac{\overline{i_d^2}}{\overline{i_s^2}} \left(rac{G_s}{g_m}

ight)^2$$

입력단 정합이 되었다면 회로의 잡음 지수는,

$$F > 1 + \gamma \tag{2.22}$$

회로의 이득은,

$$A = g_m R_L \tag{2.23}$$

공통 게이트 저잡음 증폭기의 경우 디바이스 크기와 바이어스 전류를 적절히 선택하면서 입력 정합을 할 수 있다. 또한 입력에서 출력으로의 위상 반전이 없으며 여분의 소자를 사용하지 않고도 입력 정합을 할 수 있다. 하지만 일부 어플리케이션의 경우 잡음 지수가 너무 높게 나오는 단점이 존재 한다.

그림 2.7 공통 게이트 저잡음 증폭기의 잡음 모델.

Fig. 2.7 Noise model of common-Gate LNA.

#### (4) Inductor Degeneration LNA

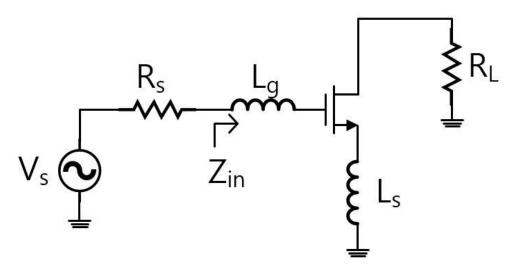

그림 2.8은 인덕터 축퇴 저잡음 증폭기를 나타낸다. 이 저잡음 증폭기의 경우 입력단에서 들여다본 입력 임피던스를 다음과 같이 표현을 할 수 있다.

$$Z_{in} = \frac{g_m L_s}{C_{qs}} + j \bigg( \omega L_s - \frac{1}{\omega C_{qs}} \bigg)$$

위 식을 통해서 알 수 있듯이 입력단에서 들여다 본 임피던스의 경우실수 부분은 인덕턴스와 커패시턴스로 이루어져 있다. 그러므로 회로에부가적인 저항을 달지 않고도 입력 정합을 할 수 있으며 부가적으로 달리는 저항으로 인한 잡음 증가를 감소시킬 수 있다. 하지만 인덕터와 MOSFET의  $C_{gs}$ 이 공진을 하는 경우에 한해서만 입력 정합이 이루어지때문에 광대역 회로에는 부적절하다.

그림 2.8 소스 축퇴 저잡음 증폭기.

Fig. 2.8 Source degeneration LNA.

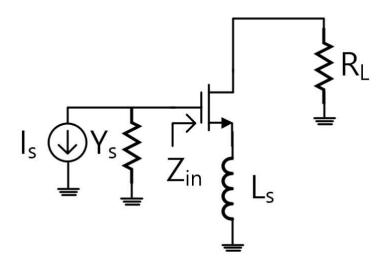

그림 2.9는 인덕터 축퇴 저잡음 증폭기 게이트 단에 인덕터를 추가한 회로이다. 이 회로의 입력 임피던스는,

$$Z_{in} = \frac{g_m L_s}{C_{qs}} + j \bigg[ \omega \big(L_g + L_s\big) - \frac{1}{\omega \, C_{qs}} \bigg] \label{eq:Zin}$$

이며 여기에서  $L_s$ 는 원하는 입력 저항을 제공하도록 사용되었다. 또한 게이트에 달려있는 인덕터로 인해서 원하는 동작 주파수에서 입력 정합을 할 수 있다. 일반적으로 소스단에 달려있는 인덕터는 본딩 인덕터로 대체할 수 있으며, 게이트 단에 달려 있는 인덕터의 경우 나선형 인덕터 (Spiral inductor) 또는 외부 인덕터(Off-chip inductor)로 구현 할 수 있다.

그림 2.9 게이트 단에 인덕터를 추가한 소스 축퇴 저잡음 증폭기.

Fig. 2.9 Source degeneration LNA with gate inductor.

인덕터 축퇴 저잡음 증폭기의 잡음 지수를 구하게 되면,

$$\begin{array}{ll} \overline{v_{o,d}^2} \! = \! \overline{i_d^2} R_L^2 & \overline{i_d^2} \! \approx \! 4kT \! \gamma g_m \Delta f \\ \overline{v_{o,s}^2} \! = \! \overline{v_s^2} \, G_m^2 \, R_L^2 & \overline{v_s^2} \! = \! 4kT \! R_s \Delta f \end{array}$$

총 잡음 지수는,

$$F = 1 + \frac{\overline{i_d^2} R_L^2}{\overline{v_s^2} Q_{in}^2 g_m^2 R_L^2} > 1 + \frac{\gamma}{g_m R_s} \frac{1}{Q_{in}^2}$$

(2.24)

회로의 이득은 다음과 같이 표현 할 수 있다.

$$A \approx -G_m R_L \tag{2.25}$$

인덕터 축퇴 저잡음 증폭기의 경우 협대역 입력 정합을 가지고 아주 좋은 잡음 지수를 가지고 있으며 가장 널리 사용되어지는 저잡음 증폭기이다. 또한 회로의 잡음지수를 좋게 하기 위해서는 인덕터의 Q-지수도 고려를 하여야 한다.

표 2.1 저잡음 증폭기의 비교.

Table. 2.1 Comparison of low noise amplifier.

|              | Zin                               | $F_{50\Omega}$                                                                                   | Gain                  | NF        |

|--------------|-----------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|-----------|

| Common       | $R_{sh}$                          | $2 + \frac{4\gamma}{g_m R_s}$                                                                    | $-\frac{g_m R_L}{2}$  | 10        |

| source       |                                   | $g_m n_s$                                                                                        | 2                     | dB        |

| Common       | $1/g_m$                           | 1.1.                                                                                             | a R                   | 4.7       |

| Gate         | $1/g_m$                           | $1+\gamma$                                                                                       | $g_m R_L$             | dB        |

| Feedback     | $ \frac{R_F + R_L}{1 + g_m R_L} $ | $\left 1 + \frac{R_s}{R_F} \left(1 + \frac{1}{g_m R_s}\right)^2 + \frac{\gamma}{g_m R_s}\right $ | $-g_m R_L$            | 5.9<br>dB |

| Inductor     |                                   | 2 (                                                                                              |                       |           |

| source       | $rac{g_m L_s}{C_{\!gs}}$         | $1+\frac{\gamma}{2}\frac{1}{r^2}$                                                                | $-G_{\!\!\!m}R_{\!L}$ | 1.8       |

| degeneration | $C_{gs}$                          | $1+rac{1}{g_mR_s}rac{1}{Q_{in}^2}$                                                             | III L                 | dB        |

#### 3. 제안하는 가변이득 저잡음 증폭기 설계

#### 3. 1 저잡음 증폭기 시뮬레이션

앞 장에서 여러 가지 저잡음 증폭기에 대해서 이론적인 분석을 하였다. 분석된 회로를 CMOS TSMC 018  $\mu$ m 공정을 이용하여서 직접 설계를 하 였으며 각 회로에 대한 특성은 다음과 같이 나타난다.

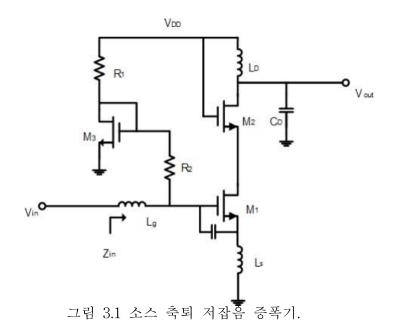

소스 축퇴 저잡음 증폭기는  $M_3$ 와  $R_1$ 을 이용한 전류 미러링(Current mirror) 방식을 통해서 게이트 전압을 인가하였다. 또한 입력 신호가 전류 미러 회로로 들어가지 않게 하기 위해서  $R_2$ 저항을  $M_3$ 의 게이트와  $M_1$ 의 게이트 사이에 연결을 하였다.

Fig. 3.1 Source degeneration LNA.

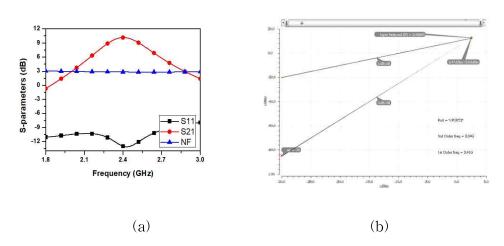

그림 3.2 소스 축퇴 저잡음 증폭기의 (a)S-parameter 와 (b) IIP3 특성. Fig. 3.2 Source degeneration LNA simulation results: (a)S-parameters and (b)IIP3.

공통 게이트 저잡음 증폭기는 큰 이득을 얻기 힘들다는 단점이 존재한다. 따라서 기존의 공통 게이트 드레인 단에 MOSFET을 cascode 형태로쌓아서 설계를 하였다.

Fig. 3.3 Common gate LNA.

그림 3.4 공통 게이트 저잡음 증폭기의 (a)S-parameter 와 (b) IIP3 특성.

Fig. 3.4 Common source LNA simulation results: (a)S-parameters and (b)IIP3.

Shunt-shunt feedback 저잡음 증폭기의 경우 앞 장에서 구현한 그대로 설계를 진행 하였다.

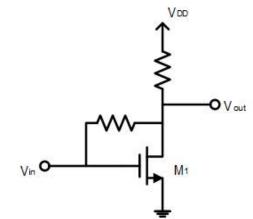

그림 3.5 Shunt-shunt feedback 저잡음 증폭기.

Fig. 3.5 Shunt-shunt feedback LNA.

그림 3.6 Shunt-shunt feedbakc 저잡음 증폭기의 (a)S-parameter 와 (b) IIP3 특성.

Fig. 3.6 Shunt-shunt feedback LNA simulation results: (a)S-parameters and (b)IIP3.

#### 3. 2. 제안된 저잡음 증폭기

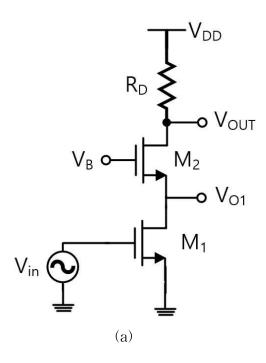

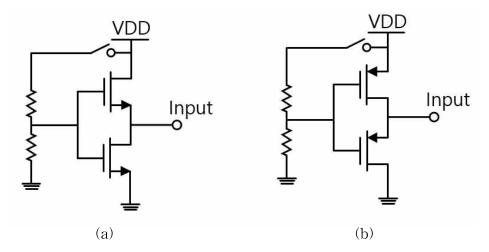

그림3.7은 inverter 구조의 저잡음 증폭기이다. 기존의 분석된 저잡음 증폭기의 경우 MOSFET이 하나로 이루어져 있으므로 충분히 큰 이득을 내지 못하는 단점이 있었다[7]-[10]. 하지만 인버터 구조의 저잡음 증폭기를 설계하게 된다면 전류 재사용(Current reuse)방식을 사용하게 됨으로써 낮은 전력 소모로 큰 이득을 가질 수 있다. 또한 부궤한 회로를 통해 넓은 주파수 대역에 대한 입력 정합을 할 수 있다.

저잡음 증폭기는 수신단의 가장 앞에 위치를 하기 때문에 저잡음 증폭기 앞단에 달리는 안테나와의 연결로 인하여 50 Ω 정합이 필요하다. 앞장에서 구한 입력 어드미턴스 식은 다음과 같다.

$$Y_{in} = \frac{1 + g_m R_L}{R_F + R_L} = \frac{1}{50}$$

하지만 인버터 구조에서의 트랜스컨덕턴스는 NMOS의 트랜스컨덕턴스와 PMOS의 트랜스 컨덕턴스 합으로 이루어진다. 이로 인해서 인버터 구조의 저잡음 증폭기의 입력 어드미턴스는 다음과 같이 표현할 수 있다.

그림 3.7 인버터 구조의 저잡음 증폭기.

Fig. 3.7 Low noise amplifier based on inverer.

$$Y_{in} = \frac{1 + G_m R_L}{R_F + R_L} = \frac{1}{50}$$

where  $G_M = g_{mn} + g_{mp}$

또한 위에서 구한  $G_M$  값을 가지고 인버터 구조의 저잡음 증폭기의 이 득을 구하게 되면 다음과 같이 표현을 할 수 있다.

$$A = -G_m(R_F \parallel R_L) \tag{3.1}$$

또한 저잡음 증폭기의 가장 중요시 되는 성능 중 하나는 잡음 지수이다. 인버터 구조의 저잡음 증폭기의 잡음 지수를 수식적으로 계산을 하면다음과 같이 표현할 수 있다.

$$NF = 1 + \frac{1}{R_s} \left( \frac{2}{3G_M} + \frac{1}{R_F G_M^2} \right) \left( 1 + G_M \left( \frac{R_s}{R_s + R_F} \right) \right)^2$$

(3.2)

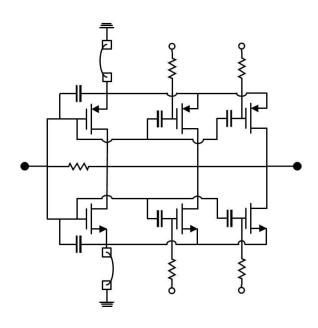

그림 3.8 제안하는 저잡음 증폭기의 회로도.

Fig. 3.8 Schematic of proposed LNA.

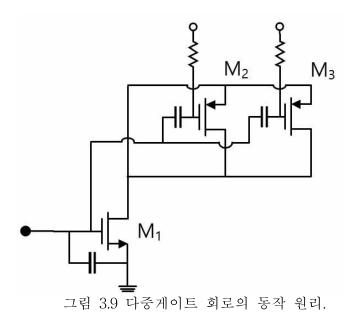

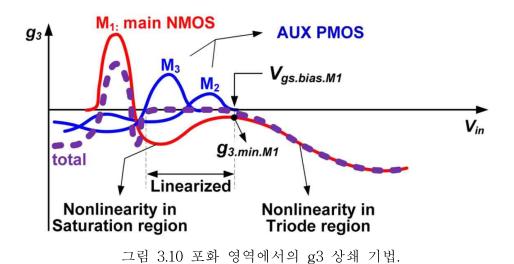

Fig. 3.9 Operation principle of multiple gate circuit.

Fig. 3.10 g3 cancellation in the saturation region.

하지만 앞에서 구한 잡음 지수의 경우 단순히 저잡음 증폭기 부분의 잡음 지수만 구한 것이다. 이번 연구에서는 저잡음 증폭기 뒷단에 가변 증폭기를 연결을 할 것이기 때문에 좀 더 정밀한 잡음 지수 계산이 필요하다. 저잡음 뒷단에 증폭기가 연결되어있다고 가정을 한 후에 잡음 지수를 구하게 되면 다음과 같이 표현을 할 수 있다.

$$\begin{split} & \overline{i_{out,R_s}^2} = \frac{g_{m3}^2(1 - R_f(g_{m1} + g_{m2}))^2}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} \overline{v_{R_s}^2} \\ & = \frac{g_{m3}^2(1 - R_f(g_{m1} + g_{m2}))^2}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} 4kTR_s \\ \overline{i_{out,1}^2} = \frac{g_{m3}^2 R_f^2 \left(\omega^2 C_{gs1}^2 R_s^2 + \left((g_{m1} + g_{m2}) R_s + 1\right)^2\right)}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} \overline{i_{R_f}^2} \\ & = \frac{g_{m3}^2 R_f^2 \left(\omega^2 C_{gs1}^2 R_s^2 + \left((g_{m1} + g_{m2}) R_s + 1\right)^2\right)}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} \frac{4kT}{R_f} \\ \overline{i_{out,2}^2} = \frac{g_{m3}^2 \left(\omega^2 C_{gs1}^2 R_s^2 R_f^2 + \left(R_s + R_f\right)^2\right)}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} \left(\overline{i_{d_1}^2} + \overline{i_{d_2}^2}\right) \\ & = \frac{g_{m3}^2 \left(\omega^2 C_{gs1}^2 R_s^2 R_f^2 + \left(R_s + R_f\right)^2\right)}{(1 + R_s(g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f)^2 + \omega^2 (C_{gs1} R_s + C_{gs3} (R_s + R_f))^2} 4kT\gamma (g_{m1} + g_{m2})} \\ \overline{i_{out,3}^2} = \overline{i_{d_3}^2} + \overline{i_{R_p}^2} = 4kT \left(\gamma g_{m3} + \frac{1}{R_D}\right) \end{aligned}$$

이 식을 통해서 전체 잡음 지수를 구하게 되면 다음과 같이 나타낼 수 있다.

$$\begin{split} NF &= 1 + \frac{\overline{i_{out,1}^2}}{\overline{i_{out,R_s}^2}} + \frac{\overline{i_{out,2}^2}}{\overline{i_{out,R_s}^2}} + \frac{\overline{i_{out,R_s}^2}}{\overline{i_{out,R_s}^2}} \\ &= 1 + \frac{R_f \left(\omega^2 C_{gs1}^2 R_s^2 + ((g_{m1} + g_{m2})R_s + 1)^2\right)}{\left(1 - R_f (g_{m1} + g_{m2})\right)^2 R_s} + \frac{\left(\omega^2 C_{gs1}^2 R_s^2 R_f^2 + (R_s + R_f)^2\right) \gamma (g_{m1} + g_{m2})}{\left(1 - R_f (g_{m1} + g_{m2})\right)^2 R_s} \\ &\quad + \frac{\left(1 + R_s (g_{m1} + g_{m2}) - \omega^2 C_{gs1} C_{gs3} R_s R_f\right)^2 + \omega^2 \left(C_{gs1} R_s + C_{gs3} (R_s + R_f)\right)^2}{(1 - R_f (g_{m1} + g_{m2})^2 R_s} \end{split}$$

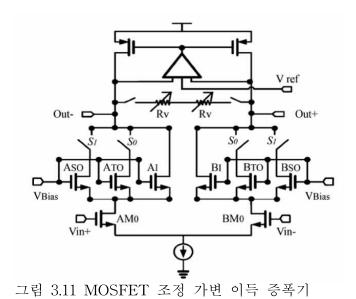

#### 3. 3 제안된 가변이득 증폭기

무선 전단부에서 많이 사용되어지는 가변이득 증폭기는 여러 범위에서 들어오는 입력 신호에 대해서 일정한 출력 전력 값을 가지게 해주는 역할을 한다[11]-[15]. 만약 입력 신호가 매우 큰 신호가 들어왔는데 낮은 입력 신호와 같은 이득을 가지고 증폭을 시켜서 뒷단에 보내주게 된다면 뒷단에서는 큰 입력 신호 때문에 회로 성능에 영향을 받을 수 있다.

이러한 가변 이득 증폭기는 무선 전단부 시스템에서만 사용되어지는 것이 아닌 인공위성의 온도 조절 시스템 [15], 페이지 어레이 레이더 시스템과 능동 위상 변환기에 사용되어진다[11]. 하지만 기존의 가변이득 증폭기의 경우 MOSFET에 스위치를 직접 연결하여서 MOSFET의 width를 변화시켜 가면서 가변 이득을 가지도록 설계되어서 스위치의 on/off 상태에따른 입력 정합이 변하고 너무 많은 스위치를 사용하여서 회로의 면적을 많이 차지 한다는 단점이 있었다[16]. 또한, 회로의 부궤한 부분에 저항을 연결하고 이 저항과 저항 앞단에 스위치를 연결하여 저항 값을 변화하면서 가변 이득을 만들어 냈으나, 저항이 추가되는 만큼 회로의 잡음 지수가 증가하게 되어서 수신단 회로에 사용하기에는 부적절 하였다[17].

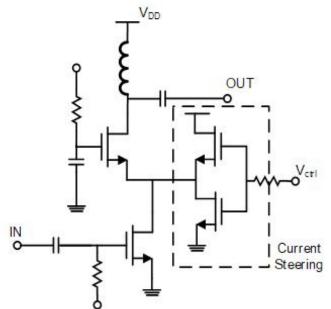

본 논문에서는 입력단의 정합에 영향을 최소화 하고 스위치 개수를 최소로 하기 위해서 current steering 기술을 이용한 가변 이득 증폭기를 제안한다. MOSFET을 cascode 형태로 구성을 하여서 충분한 이득 값을 가지고, cascode로 구성된 MOSFET사이에 current steering 회로를 연결함으로써 회로의 이득을 조절 할 수 있으며, 부가적인 저항이 들어가지 않기 때문에 회로의 잡음 지수에도 최소한의 영향을 미친다.

Fig. 3.11 Variable gain amplifer with variation MOSFET's width.

Fig. 3.12 Variable gain amplifier with variable resistor.

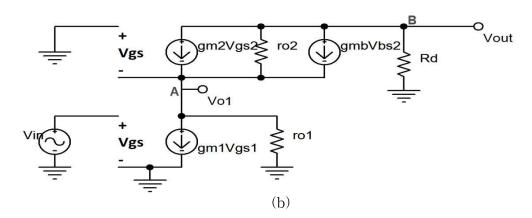

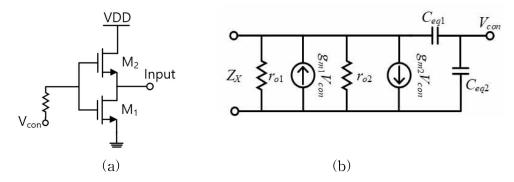

그림3.13은 제안하는 가변 이득 증폭기의 회로도이다. 가변 이득 증폭기는 공통 게이트 증폭기와 공통 소스 증폭기를 cascode로 연결을 하여서 설계되었다. 회로의 분석을 위해서 각 회로에 대한 소신호 등가 회로를 그린 후 소신호 등가 회로를 통해서 회로 분석을 진행하였다. 처음으로 회로의 전체 이득을 구하기 위해서 cascode 증폭기의 소신호 등가회로를 그림 3.14와 같이 나타내었다. 소신호 등가 회로 분석 방식을 통해서 회로의 이득을 구하면 식(3.3)과 같이 나타낼 수 있다.

$$\begin{array}{l} A_v \approx -g_{m1}[\left(1+g_{m2}r_{o2}\right)r_{o1}+r_{o2}] \\ \approx -g_{m1}r_{o1}g_{m2}r_{o2} \end{array} \tag{3.3}$$

위 수식으로부터 회로의 전체적인 이득은 공통 게이트 증폭기인  $M_2$ 에 의해서 큰 영향을 받으며, 공통게이트 회로의 파라미터 값을 변화 시키게 된다면 회로의 전체적인 이득을 변화 시킬 수 있음을 알 수 있다.

그림 3.13 Current steering 회로를 이용한 가변 이득 증폭기.

Fig. 3.13 Variable gain amplifier with current steering.

그림 3.14 Cascode 증폭기: (a)회로도, (b) 소신호 등가모델.

Fig. 3.14 Cascode amplifier: (a)schematic, (b) small signal model.

그림3.15는 current steering 회로의 회로도 및 소신호 등가회로이다. Current steering회로의 입력단에서 들여다 본 입력 임피던스를  $Z_X$ 라고 한다면 다음과 같은 식(3.4)로 나타낼 수 있다.

$$Z_X = \frac{r_{o1}r_{o2}(C_{eq1} + C_{eq2})}{r_{o1}r_{o2}C_{eq1}(g_{m2} - g_{m1} - sC_{eq1}) + (C_{eq1} + C_{eq2})(r_{o1} + r_{o2} + r_{o1}r_{o2}sC_{eq1})}$$

(3.4)

여기에서  $C_{eql}=C_{gsl}+C_{gdl}$ ,  $C_{eql}=C_{gsl}+C_{gdl}$  이다. 위 수식으로부터 제안된 회로의 전체이득을 계산하게 된다면 다음과 같이 나타 낼 수 있다.

$$A_{v,tot} \approx -g_{m1}r_{o1}g_{m2}(r_{o2} \parallel Z_X)$$

(3.5)

제안하는 가변이득 증폭기는 current steering 회로의 출력 저항 $(r_o)$ 을 변화 시키면서 가벽이득을 얻을 수 있으며  $V_{gs}$ 값을 변화시키게 된다면 식(3.6)과 같이 출력저항 값을 변화시킬 수 있다.

$$r_o = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th})} \tag{3.6}$$

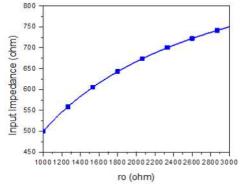

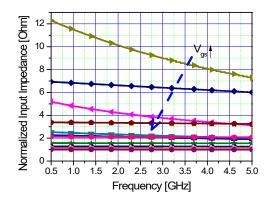

위 식으로부터  $V_{gs}$  값이 증가를 하게 된다면 MOSFET의 출력 저항이 작아진다는 것을 알 수 있다. 그림3.16은 출력 저항의 변화에 따른 current steering 회로의 입력 임피던스를 나타낸 그래프이다. 그림에서 알 수 있듯 출력 저항 값이 커짐에 따라 입력 임피던스도 같이 증가를 하게 된다. 또한 그림3.17은  $V_{gs}$ 의 변화에 따른 정규 화된 입력 임피던스 값을 나타낸다. 이 그래프로부터  $V_{gs}$  값이 증가를 하게 된다면 회로의 입력 임피던스는 작아진다는 것을 알 수 있다. 따라서 current steering 회로의  $V_{gs}$ 값을 증가시킨다면 입력 임피던스가 작아지면서 회로의 이득이 작아진다는 것을 알 수 있다.

그림 3.15 Current steering 회로: (a)회로도, (b)소신호 등가 회로.

Fig. 3.15 Current steering circuit: (a)schematic (b)small signal model.

그림 3.16 출력저항에 따른 입력 임피던스의 변화.

Fig. 3.16 Variation of input impedance according to  $r_o$ .

그림 3.17 전압에 따른 입력 임피던스의 변화.

Fig. 3.17 Variation of input impedance according to  $V_{gs}$ .

#### 3. 4 제안된 저잡음 가변이득 증폭기

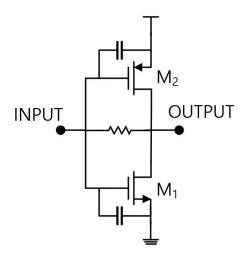

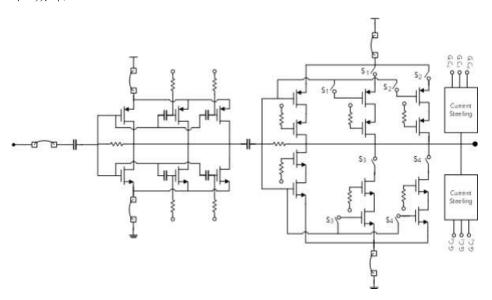

그림3.18은 제안하는 저잡음 가변이득 증폭기의 전체 회로도이다. 제안하는 회로는 앞단에 다중 게이트를 이용한 저잡음 증폭기와 current steering 회로가 달린 cascode 증폭기로 구성되어 진다. cascode 증폭기는 더 높은 전압 이득을 가지기 위해서 NMOS cascode 증폭기와 PMOS cascode 증폭기로 구성되어 진다. NMOS와 PMOS가 cascode로 구성되어 집으로써 전류 재사용 기법을 사용할 수 있으며, 적은 전력을 소모하면서 높은 전압 이득을 가질 수 있다. 또한 current steering 회로 역시 그림 3.19처럼 NMOS 쪽에 달린 회로는 NMOS를 이용하여 회로를 설계하였으며, PMOS쪽에 달린 회로는 PMOS를 이용하여 설계 하였다. 하지만 current steering 회로는 전류 소모량이 많다는 단점이 존재하기 때문에 current steering 회로만을 이용하여서 이득을 가변하지 않고, cascode 증폭기의 MOSFET width를 같이 조절을 하며 가변이득을 가지게 하였다. MOSFET width를 조절하여 가변이득을 얻게 된다면 전력 소모량도 줄일수 있다.

그림 3.18 제안하는 가변 이득을 가지는 저잡음 증폭기.

Fig. 3.18 Proposed LNA with variable gain.

그림 3.19 Current steering 회로: (a)NMOS, (b)PMOS.

Fig. 3.19 Current steering circuit with: (a)NMOS, (b)PMOS.

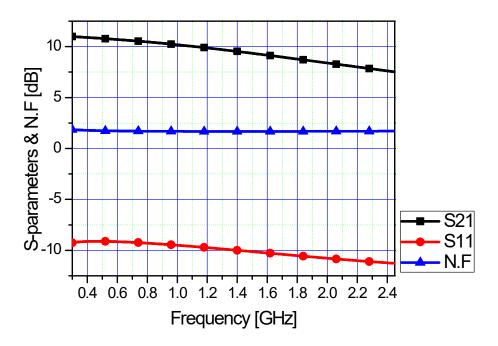

그림 3.20 제안하는 저잡음 증폭기의 시뮬레이션 결과.

Fig. 3.20 Simulation results of proposed LNA.

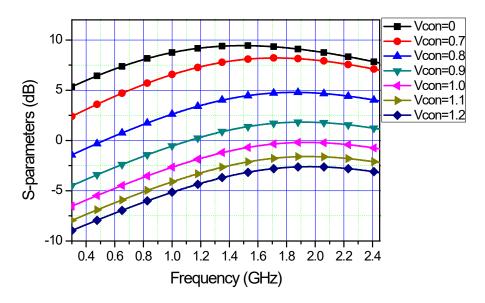

그림 3.21 제안하는 가변 이득 증폭기의 S21 특성(1단).

Fig. 3.21 S21 characteristics of proposed VGA(1stage).

그림 3.22 제안하는 가변 이득 증폭기의 S21 특성(3단).

Fig. 3.22 S21 characteristics of proposed VGA(3stage).

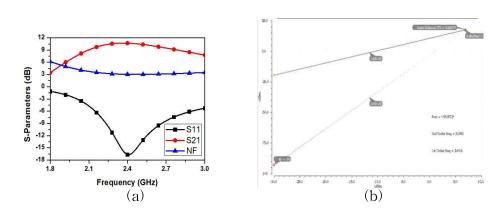

그림3.20은 저잡음 증폭기의 시뮬레이션 결과이다. 저잡음 증폭기의 경우 전 영역에서 2 dB 미만의 낮은 잡음지수를 가지고 있으며 1.2 GHz 미만의 주파수에서는 약 10 dB 이상의 이득을 가지고 있다. 높은 주파수 대역에서 이득이 감소를 하는 것을 최대한 줄이기 위해서  $S_{11}$  특성을 고주파 대역에서 더 낮은 값을 가지도록 설계를 진행 하였다.

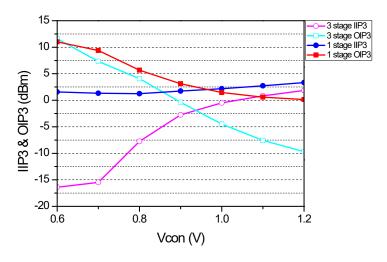

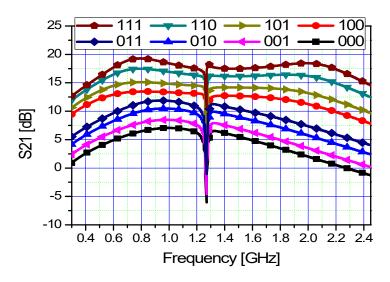

그림3.21과 그림3.22는 가변이득 증폭기의 시뮬레이션 결과이다. 그림 3.21은 가변이득 증폭기를 1단만 가지고 설계를 진행한 결과이며 그림3.22는 가변 이득 증폭기를 cascade 형태로 3단을 연결한 결과이다. 가변이득 증폭기의 경우 저잡음 증폭기에서 낮은 주파수 대역에서는 이득이 높지만 높은 주파수 대역으로 가게 되면 이득이 감소하는 특성을 상쇄시키기 위해서 낮은 주파수 대역에서의 이득이 높은 주파수 대역에서의 이득보다조금 낮은 값을 가지도록 설계를 하였다. 또한 가변이득 증폭기를 cascade 형태로 설계를 하게 된다면 더 높은 전압이득 및 더 넓은 가변이득 범위를 가질 수 있다. 또한 그림3.23은 가변 이득 증폭기의 IIP3 및 OIP3 특성을 나타내고 있다. 1단만 사용하는 경우의 IIP3는 거의 일정하지만 3단을 사용한 경우 IIP3 특성이 좋지 않은 점을 고려하여서 이번 설계에서는 가변 이득 증폭기를 1단만 가지고 설계를 진행하였다.

그림 3.23 제안하는 가변 이득 증폭기의 선형성 특성.

Fig. 3.23 Linearity characteristic of proposed VGA.

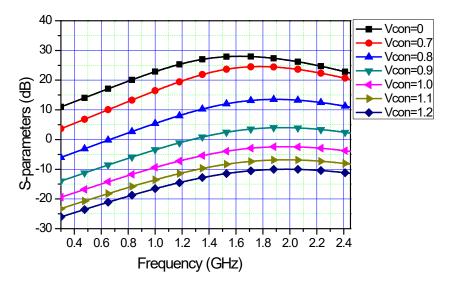

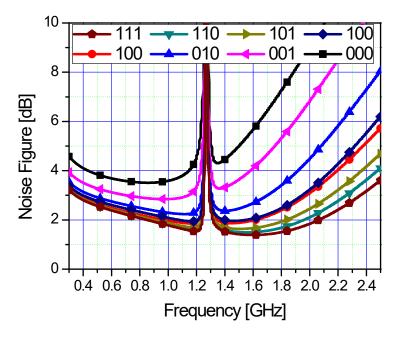

그림3.24와 그림3.25는 제안하는 저잡음 증폭기와 가변이득 증폭기를 연결하여서 시뮬레이션 한 결과이다. 그림3.24는 제안된 회로에 대한 S21 (이득)을 나타낸 결과이다. 낮은 주파수 대역에서는 약 20 dB의 이득을 가지고, 높은 주파수 대역에서는 약 18 dB의 이득을 가지고 있다. 또한 gain code(G.C)에 따라서 2 dB의 이득차를 가지는 것을 알 수 있다. 그림 3.25는 제안된 회로의 잡음 지수를 나타낸 결과이다. 그래프에서 알 수 있듯이 NB-IoT 대역(729 MHz ~ 960 MHz, 1805 MHz ~ 2170 MHz)에서 2 dB 미만의 잡음지수를 가진다. 또한 이득의 감소에 따라서 가변 이득 증폭기의 잡음지수가 높아져 이득이 감소하면 감소할수록 잡음지수가 올라가는 것을 확인 할 수 있다.

그림 3.24 제안하는 가변이득 저잡음 증폭기의 S21 시뮬레이션 결과. Fig. 3.24 S21 simulation of proposed variable gain LNA.

그림 3.25 제안하는 가변이득 저잡음 증폭기의 잡음지수 시뮬레이션 결과.

Fig. 3.25 NF simulation results of proposed variable gain LNA.

- 4. 제안된 CMOS 가변이득을 가지는 저잡음 증폭기의 제작 및 측정결과

- 4.1 제안된 CMOS 가변이득 저잡음 증폭기의 레이아웃

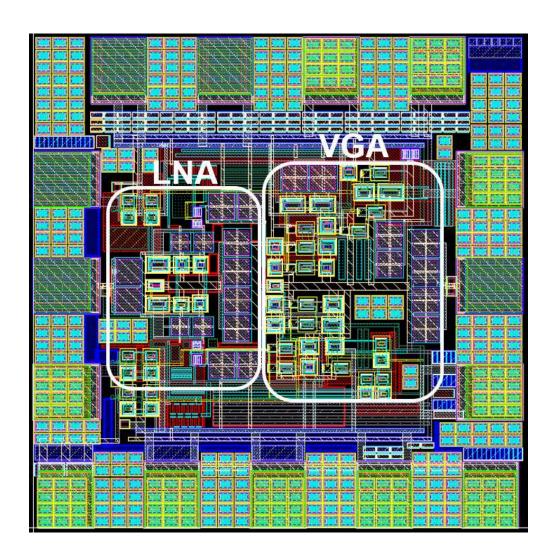

그림 4.1 제안하는 회로의 레이아웃.

Fig. 4.1 Layout of proposed circuit.

본 논문에서 제안하는 CMOS 가변이득을 가지는 저잡음 증폭기는 TSMC사의 RF  $0.18~\mu m$  공정을 이용하여 설계 및 제작하였다. 제안된 회로는 Cadence사의 spectre 프로그램을 이용하여 시뮬레이션 하였으며, virtuoso 프로그램을 이용하여 레이아웃을 진행하였다. 그림4.1은 제안하는 회로의 레이아웃 사진이다. 설계된 회로의 레이아웃 크기는 본딩 패드를 포함하면  $600 \times 600~\mu m^2$  이며 본딩 패드를 제외한 코어(Core) 부분은  $400 \times 260~\mu m^2$ 의 크기를 가진다.

#### 4.2 제안하는 CMOS 가변이득 저잡음 증폭기의 측정 결과

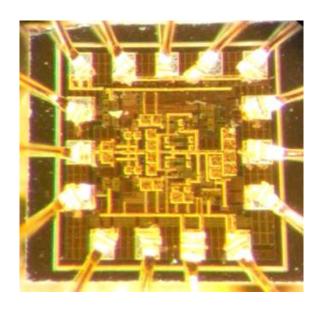

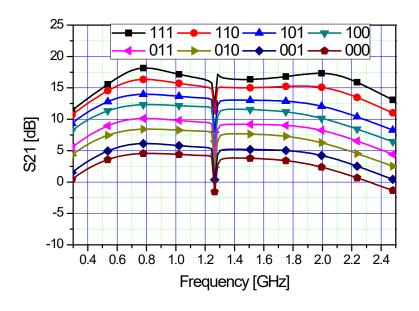

그림4.2는 제작된 회로를 현미경을 이용하여 촬영한 사진이다. 제작된 칩을 pcb와 연결을 위해서 본딩 와이어를 이용하였다. 회로의 측정을 위해 제작된 pcb는 epoxy 기판(ɛr = 4.4, tand = 0.02, h = 0.787 mm)을 이용하여 제작되었다. 제작된 회로는 네트워크 분석기(Network Analyzer 8720D), 신호 분석기(Spectrum Analyzer MXA N9020A), 신호 발생기(Signal Generator ESG E4438C),와 잡음 지수 측정기(Noise Figure Meter 8970B)를 이용하여서 측정을 하였다. 그림4.3은 회로의 S21(이득)의 측정결과 이다. 729 ~ 960 MHz 대역에서는 약 1 dB 이내의 이득 편차를 가지고 있으며 1805 ~ 2170 MHz 대역에서는 0.7 dB 이내의 이득 편차를 가지고 있다. 또한 각 대역에서 2∓0.5 dB 스텝을 가지는 가변 이득 특성을 보인다.

그림 4.2 제안하는 회로의 실제 사진.

Fig. 4.2 Photo of proposed circuit.

그림 4.3 제안하는 회로의  $S_{21}$  측정 결과.

Fig. 4.3  $S_{21}$  measurement results of proposed circuit.

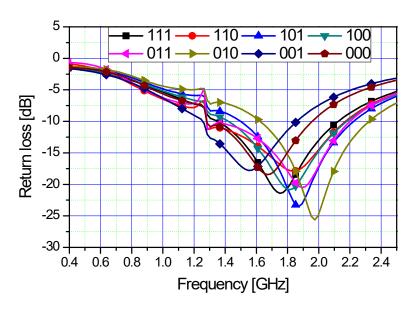

그림 4.4 제안하는 회로의 삽입손실 특성.

Fig. 4.4 Insertion loss measurement results of proposed circuit.

그림4.4는 제안된 회로의 삽입 손실을 나타낸 그래프이다. MOSFET의 기생성분이 고주파로 가면 갈수록 회로의 이득에 많은 영향을 미치기 때문에 입력단 정합을 고주파쪽에서 하여서 저주파와 고주파 사이에 이득의 편차를 최대한 줄이고자 하였다. 저주파 대역에서는 약 -5 dB의 삽입 손실을 가지고 고주파 대역에서는 -10 dB 미만의 삽입 손실을 가진다. 또한 가변 이득에 대해서 삽입 손실은 큰 변화를 하지 않는 것을 확인 할수 있다.

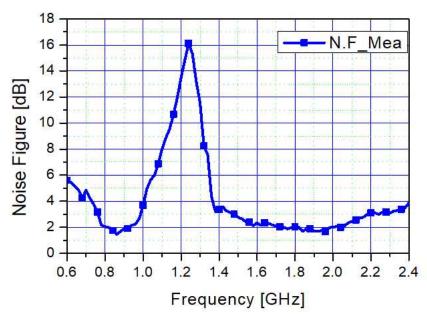

그림4.5는 제안된 회로의 잡음 지수 측정 결과이다. 잡음 지수는 회로가 가장 큰 이득을 가지고 있을 때(G.C: 111)를 기준으로 측정을 진행하였다. 잡음 지수는 이득이 감소하면 증가를 하게 되며, 저주파 및 고주파 동작 영역에서 약 2 dB 미만의 잡음 지수를 가지고 있는 것을 알 수 있다.

그림 4.5 제안하는 회로의 잡음지수 측정 결과.

Fig. 4.5 NF measurement result of proposed circuit.

그림4.6과 그림4.7은 제안된 회로의 선형성을 측정한 결과이다. 저주파수 대역은 880 MHz, 고주파수 대역은 1.9 GHz 대역에 대해서 선형성을 측정 하였다. 저주파수 대역에서의 경우 입력  $P_{1dB}$ 는 -7 dBm 출력  $P_{1dB}$ 는 11 dBm을 가졌으며 OIP3의 경우 16 dBm을 가졌다. 고주파수 대역의 경우 입력  $P_{1dB}$ 는 -10 dBm 출력  $P_{1dB}$ 는 7 dBm을 가졌으며 OIP3의 경우 14 dBm을 가졌다.

측정 된 결과를 표4.1과 표4.2에 정리를 하였다. 고주파수 대역에서는 회로의 기생성분이 저주파수 대역에 비해서 회로에 영향을 많이 미치게 되면서 전체적인 성능이 저주파수대역에 비해서 약간 감소를 하였다.

그림 4.6 제안하는 회로의 선형성 측정결과(저주파 대역).

Fig. 4.6 Linearity measurement result of propsoed circuit(Low band).

Fig. 4.7 Linearity measurement result of propsoed circuit(High band).

## 표 4.1 제안하는 회로의 이득 특성(저주파 대역).

Table 4.1 Gain characteristic of proposed circuit(Low band).

| Freq.    | 729-960    | Gain Step 729-960 |            | Gain Step |  |

|----------|------------|-------------------|------------|-----------|--|

| G.C      | [MHz] Mea. | Mea.              | [MHz] Sim. | Sim.      |  |

| 111 [dB] | 18.01      |                   | 19.15      |           |  |

| 110 [dB] | 16.26      | 1.75              | 17.39      | 1.76      |  |

| 101 [dB] | 13.94      | 2.32              | 15.07      | 2.32      |  |

| 100 [dB] | 12.32      | 1.62              | 13.45      | 1.62      |  |

| 011 [dB] | 10.11      | 2.21              | 11.76      | 1.69      |  |

| 010 [dB] | 8.43       | 1.68              | 10.2       | 1.56      |  |

| 001 [dB] | 6.11       | 2.32              | 8.26       | 1.94      |  |

| 000 [dB] | 4.56       | 1.55              | 6.77       | 1.49      |  |

# 표 4.2 제안하는 회로의 이득 특성(고주파 대역).

Table 4.1 Gain characteristic of proposed circuit(High band).

| Freq.    | 1.8-2.17   | Gain Step | 1.8-2.17   | Gain Step<br>Sim. |  |

|----------|------------|-----------|------------|-------------------|--|

| G.C      | [GHz] Mea. | Mea.      | [GHz] Sim. |                   |  |

| 111 [dB] | 17.24      |           | 18.30      |                   |  |

| 110 [dB] | 15.26      | 1.98      | 16.42      | 1.88              |  |

| 101 [dB] | 12.45      | 2.81      | 13.68      | 2.74              |  |

| 100 [dB] | 10.58      | 1.87      | 11.82      | 1.86              |  |

| 011 [dB] | 8.60       | 1.98      | 8.11       | 3.71              |  |

| 010 [dB] | 6.68       | 1.92      | 6.52       | 1.59              |  |

| 001 [dB] | 4.60       | 2.08      | 4.30       | 2.22              |  |

| 000 [dB] | 2.80       | 1.8       | 2.81       | 1.49              |  |

표 4.3 제안하는 회로의 특성 정리.

Table 4.3 Summarize characteristic of proposed circuit.

|                               | 880 MHz | 1900 MHz |

|-------------------------------|---------|----------|

| N.F [dB]                      | 1.67    | 1.72     |

| Output P <sub>1dB</sub> [dBm] | 11      | 7        |

| OIP3 [dBm]                    | 16      | 14       |

| P <sub>DC</sub> [mW]          | 7.8     | 7.8      |

표 4.4 기존 논문들과의 회로 비교.

Table 4.4 Performances comparison with conventional researches.

| Ref.         | fs<br>[GHz] | BW<br>[GHz] | ΔGain<br>[dB] | Gmax<br>[dB] | OIP3<br>[dBm] | Input<br>P1 dB | N.F<br>[dB] |

|--------------|-------------|-------------|---------------|--------------|---------------|----------------|-------------|

| [14]         | 5.2         | 1.5         | 8             | 20           |               | -15            | 3.5         |

| [15]         | 9.00        | 4           | 20            | 12.5         |               | 0              |             |

| [16]         | 3.50        | <1          | 16            | 7            |               | -10            | 7           |

| [17]         | 2.5         | 0.8         | 45            | 47           | 5.3           | -32            | 0.81        |

| This<br>work | 0.84        | 0.24        | 16            | 18           | 16            | -7             | 1.67        |

|              | 1.98        | 0.37        | 16            | 17.2         | 14            | -10            | 1.72        |

## 5. 결론

본 논문에서는 NB-IoT 대역에서 사용가능한 CMOS 가변이득을 가지는 저잡음 증폭기에 대해서 설계를 하였다. 저잡음 증폭기의 경우 다중 게이트를 이용하여서 높은 선형성을 가지며 인버터 형식으로 설계를 하였으며 전류 재사용 방식을 통해서 낮은 전력소모로도 높은 이득을 가지게 설계되었다. 또한 저잡음 증폭기는 시뮬레이션 결과 1.5 dB 미만의 낮은 잡음지수를 가진다. 또한 가변이득을 가지기 위해서 current steering 회로를 사용하여서 회로가 가변이득을 가질 수 있도록 설계 하였으며, 저잡음 증폭기 뒷단의 연결함으로써 잡음 지수에도 큰 영향을 미치지 않게 설계하였다. 저잡음 증폭기의 뒷단에 달린 증폭기의 경우 NMOS와 PMOS를 cascode 형태로 설계를 진행하여서 저잡음 증폭기와 마찬가지로 전류 재사용 방법으로 낮은 전력으로도 높은 이득을 가질 수 있도록 설계를 하였다. 또한 가변이득 증폭기 단을 cascade 형태로 연결을 하게 된다면 더높은 이득과 더 넓은 가변 범위를 가질 수 있다.

설계된 회로는 NB-IoT 대역인 729 ~ 960 MHz와 1805 ~ 2170 MHz 대역에서 2 dB 미만의 잡음지수와 17 dB 이상의 이득을 가지고 2 dB 간격의 이득 변화 폭을 가진다. 또한 회로의 선형성을 측정하기 위해서  $P_{1dB}$  및 OIP3 특성을 보았으며 낮은 주파수 대역에서는 출력  $P_{1dB}$ 가 11 dBm, OIP3는 16 dBm을 보였으며, 높은 주파수 대역에서는 출력  $P_{1dB}$ 가 7 dBm, OIP3는 14 dBm을 가졌다. 설계된 회로는 높은 선형성과 낮은 잡음 지수를 가직고 있으며 전력소모도 8 mW 미만으로 낮은 전력을 소모하는 것을 알 수 있다. 제안된 회로는 여러 무선 전단부에도 적용이 가능하다.

제안하는 회로는 CMOS 공정을 사용하여 설계하였으며, 이는 회로 면적 및 회로 제작비용을 줄 일 수 있을 것으로 기대된다. 또한 CMOS를 이용하여서 설계를 하였기 때문에 기저대역의 회로 및 디지털 단 회로와 칩하나만을 가지고도 구현이 용이하다. 또한 설계된 회로는 입력단의 정합지점을 바꾼다면 NB-IoT 대역뿐만 아니라 다른 여러 대역의 무선 통신전단부 회로로 사용이 가능하다.

## 6. 참고문헌

- [1] A. Zolfaghari, A. Chan, and B. Razavi, "Stacked inductors and transformers in CMOS technology," *IEEE Journal of Solid-State Circuit*, vol. 36, no. 4, pp. 620–628, Apr. 2001.

- [2] H. Darabi, "A blocker filtering technique for SAW-less wireless receivers," *IEEE Journal of Solid-stage Circuit*, vol. 42, no. 12, pp. 2766–2773, Dec. 2007.

- [3] V. Aprin, "A new method of TX leakage cancelation in W/CDMA and GPS receivers," in Proc. IEEE RFIC Symp., pp. 87–90, 2008.

- [4] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, and M. Kuijk, "Low-area active-feedback low-noise amplifier design in scaled digital CMOS," *IEEE Journal of Solid-Stage Circuit*, vol. 43, no. 11, pp. 2422–2433, Nov. 2008.

- [5] B. K. Kim, D. Im, J. Choi, and K. Lee "A highly linear 1 GHz 1.3 dB NF CMOS low-noise amplifier with complementary transconductace linearization," *IEEE Journal of Solid-Stae Circuit*, vol. 49, no. 6, pp. 1286–1302, Jun. 2014.

- [6] Guillermo Gonzalez, Microwave Transistor Amplifiers Analysis and Design, 2nd ed. Prentice Hall, Inc. 1984.

- [7] D. Im, I. Nam, H. Kim, and K. Lee, "A wideband CMOS low noise amplifier employing noise and IM2 distortion cancellation for a digital TV tunner," *IEEE Journal of Solid-State Circuit*, vol. 44, no. 3, pp. 686-698, Mar. 2009.

- [8] D. Im, H. Kim, and K. Lee, "A CMOS resistive feedback differential low-noise amplifier with enhanced loop gain for digital TV tunner applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 11, pp. 2633–2642, Nov. 2009.

- [9] S. E. Rosenbaum, C. Baringer, and L. E. Larson, "Design of a high dynamic-range variable-gain-amplifier for a DBS tuner front-end," in Proc. 1st Annu. UCSD Wireless Commun. Conf., San Diego, CA, Mar.1998, pp. 83-89.

- [10] B. J. Edward, D. R. Helms, R. S. Webb, and S. Weinreb, "W-band active transmit and receive phased array antennas," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Orlando, FL, May 1995, vol. 3, pp. 1095–1098.

- [11] S. A. Mitilineos, G. K. Mitropoulos, and C. N. Capsalis, "A new active RF phase shifter using variable gain, drain voltage controlled pHEMTs: A 2.4-GHz ISM implementation," *IEEE Microwave Wireless Component Letters*, vol. 15, no. 7, pp. 454-456, Jul. 2005.

- [12] S. Y. Kang, Y. Jang, I. Y. Oh, and C. S. Park, "A 2.16 mW low power digitally-controlled variable gain amplifier," *IEEE Microwave Wireless Component Letters*, vol. 20, no. 3, pp. 172–174, Mar. 2010.

- [13] Q. H. Duong, Q. Le, C. W. Kim, and S. G. Lee, "A 95-dB linear lowpower variable gain amplifier," *IEEE Transaction on Circuits and Systems. I*, vol. 53, no. 8, pp. 1648–1657, Aug. 2006.

- [14] M. D. Tsai, R. C. Liu, C. S. Lin, and H.Wang, "Alow-voltage fully-integrated 4.5-6 GHz CMOS variable gain low noise amplifier," in Proc.33th Eur. Microw. Conf., Munich, Germany, Oct. 2003, pp. 13-16.

- [15] Q. Chaudhry, R. Alidio, G. Sakamoto, and T. Cisco, "An SiGe MMIC variable gain cascode amplifier," *IEEE Microwave Wireless Components. Letters*, vol. 12, no. 11, pp. 424–425, Nov. 2002.

- [16] K. Nishikawa and T. Tokumitsu, "An MMIC low-distortion variable gain amplifier using active feedback," *IEEE Transactions on Microwave Theory and Techniques*, vol. 43, no. 12, pp. 2812–2816, Dec. 1995.

- [17] M. A. Masud, H. Zirath, and M. Kelly, "A 45 dB variable gain low noise MMIC amplifier," *IEEE Transactions on Microwave Theory and Techniques*, vol 54, no.6, pp. 2848–2855, Jun. 2006.