# NMOS 래치구조의 차동지연 셀을 이용한 풀 스윙 CMOS 전압 제어 링 발진기의 설계

\*최 장 홍 , 정 용 채 , 정 항 근 , 황 인 갑\* , 박 진 구\*\*

전북대학교 전자정보공학부

\* 전주대학교 전기전자정보통신공학부

\*\* LG 정보 통신

# Design of a Full-Swing CMOS Ring-Type VCO Using a Differential Delay Cell with NMOS Latch

Jang-Hong Choi, Yong-Chae Jeong, Hang-Geun Jeong, In Gap Hwang\*, Jin-Gu Park Dept. of Electronics & Information Engineering, Chonbuk National Univ.

\* Dept. of Electrical and Electronic Eng., Jeonju Univ.

\*\* LG Information and Communications

E-mail: jhchoi@iclab.chonbuk.ac.kr

### Abstract

A CMOS ring-type oscillator IC whose oscillation frequency rang from 940MHz to 1050MHz is presented in this paper. The proposed VCO was designed for full swing operation to reduce phase noise and to make it easy to integrate into frequency synthesizers. Frequency tuning circuit was analyzed and verified through simulation. With an active area of 0.13mm<sup>2</sup>, the test chip which includes two drivers of 50 ohm loads consumes 75mW at maximum frequency from 2.5V supply.

# I. 서론

무선 통신 시스템의 고주파 전단부는 고주파 특성 이 우수하 GaAs 또는 바이폴라 진정회로가 주로 사용 증가로 인해 고주파 전단부를 CMOS 기술로 실용화하는 것이 가능할 것으로 예상되며 저주파 회로와 단 일침화하는것 또한 가능하리라 본다.

최근 이동 통신 시장의 급증으로 인해 사용 가능한 주파수 대역은 포화 상태에 이르고 있다. 이에 대한 해결책으로 동작 주파수를 높이거나, 채널 주파수의 간격을 줄여야 하는데 이와 같은 방안은 각 불록의 사양을 까다롭게 한다. 특히 전압 제어 발진기에서는 농작 주파수가 높아질수록 위상 잡음은 증가하고 채널긴격이 좁을수록 낮은 위상 잡음을 요구한다. 전압 제어 발진가는 전체 시스템의 성능을 좌우하는 불록 중 하나로 고주파 전단부에서 주파수 합성기의 한 부분으로 구성된다. 현재 대부분의 상용화된 주파수 합성기는 전압 제어 발진기와 그 이외의 불록을 모듈화하여 사용하고 있다. 이는 전체 시스템의 소형화, 제가화, 제전력화에 위배된다.

본 논문에서는 이와 같은 요구에 부용하기 위해 선

되어져 왔다. 이와 같은 공정 기술은 아날로그 회로에 서는 좋은 성능을 나타내지만, CMOS 공정 기술에 비 해 고가이며 일반적으로 저주파 대역에서 동작하는 회로와 단일칩화하는데는 불리하다. 이에 반해 CMOS 공정 기술은 채널 길이의 축소로 인한 차단주파수의 합세어 발전기를 단필함와 될 구 있는 양반으로 원개 방향을 제시하였고, 집 제작을 통해 가능성을 검증하 였다. 또한 주파수 가변회로에 대한 이론적인 해석을 수행하였다.

변환자 마리트 미국시됩스와 제이원인의 마라 현대 미밀라 NUE MOS 미국시티이고, M2는 제이

- 167 -

'ÙÀ1/2/

# Ⅱ. 발진기 동작원리 및 회로 설계

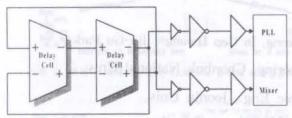

링 발진기는 인버터 체인을 궤환시켜 전체루프를 한 바퀴 돌았을 때 입출력 위상차가 180 \* 가 되면 발진 하는데, 이 위상차는 인버터 및 도선의 기생 커패시턴 스에 기인한다. 주파수 합성기에 사용되는 발진기의 가장 중요한 요소로는 주파수의 가변 범위, 위상 잡음, 전원 및 기판잡음, 입출력의 선형성이 있다 [1]. 일반적으로 전원 및 기판잡음을 제거 하기 위해서는 차동 구조로 설계되어야 한다. 본 논문의 설계된 링 발진기는 제작이 용이하며, 저전력 소비, 작은 면적이 가능한 인버터를 기본 지연 셀로 하는 2단 차동 링 발진기이다. 그림 1은 설계된 2단 링 발진기 타입의 VCO 블록도이다.

그림 1. VCO 블록도

#### A. VCO core 회로 설계

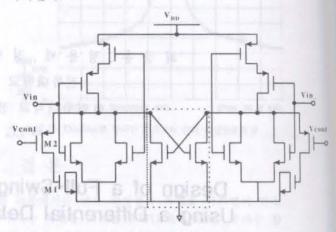

풀 스윙하는 링 발진기의 잡음해석은 어렵기 때문에 일반적으로 NMOS 또는 PMOS가 도통되었을 때의 각각의 트랜지스터에서 발생하는 열잡음으로 근사화 한다[2]. 따라서, NMOS 와 PMOS가 동시에 도통되는시간이 작고 천이시간이 짧을수록 위상 잡음은 줄어들수 있다. 설계된 발진기는 이러한 점을 고려하여 출력이 풀 스윙하고, 인버터의 천이 시간을 줄이기 위해그림 2에서 볼 수 있듯이 NMOS 래치를 삽입하였다. NMOS 래치는 천이 시간의 향상 뿐만 아니라 지연젤이 차동으로 동작할 수 있도록 한다.

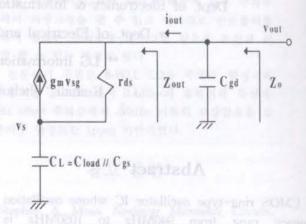

차동 지연센을 구성하는 방법으로 인버터의 PMOS 를 선형 영역에서 동작시켜 부하로 사용하는 방식[2]이 있는데 대부분 풀 스윙이 되지 않아 의도한 목적에 적합하지 않기 때문에 회로 설계방향에서 제외되었다. 본 논문에서는 빠른 신호천이를 위해 래치의 정궤환 [4]을 이용하는 구조를 선택하였고, 이를 위해 PMOS 전압에 따라 변하는 가변 저항 역할을 한다. 그림 2의 가변 부하 커패시턴스 회로의 소신호 등가회로는 그림 3과 같다. 여기서  $V_{\rm out}$ 은 그림 2의 M2의 쏘스 단자를 의미한다.

그림 2. 지연 셀 회로도

그림 3. 소신호 등가회로

그림 3의 Vs 단자에서 KCL 법칙을 적용하면

$$\frac{v_{out}}{v_s} = (s C_L r_{ds} + g_m r_{ds} + 1) \qquad (1)$$

이 되고, 드레인에서 바라본 임피던스를 구하기 위해 KCL을 적용하면.

$$i_{out} = \frac{s C_L v_{out}}{s C_L r_{ds} + g_m r_{ds} + 1}$$

(2)

$$z_{out} = r_{ds} + \frac{r_{ds} g_m + 1}{s C_L}$$

(3)

래치보다 더 좋은 회로 특성을 지닌 NMOS 래치를 NOR에 각각 연결하여 사용하였다. 지연 쌜은 NOR 두 개로 구성되어 있으며 차동으로 동작하는 인버터 회로 역할을 한다.

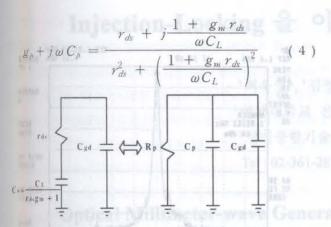

주파수 가변을 위해 그림 2의 M1과 M2를 이용해 출력에서 바라본 커페시턴스가 제어전압에 따라 변하 도록 하였다. M1은 MOS 커페시터이고, M2는 제어 이 된다. 식 ( 3 )으로부터 저항  $r_{ds}$  와 커페시터  $C_1$  /( $r_{ds}$   $g_m$  + 1)이 직렬연결 되었음을 알 수 있다. 출력임피던스  $Z_0$ 는  $Z_{out}$ 과  $C_{gd}$ 가 병렬 연결되어 있고,  $Z_{out}$ 을 저항과 커페시터의 병렬 연결된 등가회로로 표시하면그림 4와 같다.

그림 4의 Rp와 Cp를 구하면 다음 식과 같다.

- 168 -

그림 4. RC 직렬의 등가 병렬회로

$$g_h = \frac{r_{ds}}{r_{ds}^2 + \left(\frac{1 + g_m r_{ds}}{\omega C_L}\right)^2} \tag{5}$$

$$C_{p} = \frac{\frac{1 + g_{m} r_{ds}}{\omega^{2} C_{L}}}{r_{ds}^{2} + \left(\frac{1 + g_{m} r_{ds}}{\omega C_{L}}\right)^{2}}$$

(6)

식 (6) 에서  $r_{d_s} \ll \left(\frac{1+g_m\,r_{d_s}}{\omega\,C_L}\right)$ 이 되어 제어 전압이 낮아지면  $V_{sg}$ 가 커지고,  $g_{m}$ 이 커져  $C_{\nu}$ 가 작아진다. 따라서 발진 주파수는 제어 전압에 반비례하는 회로가된다. 반대의 경우 즉  $r_{d_s} \gg \left(\frac{1+g_m\,r_{d_s}}{\omega\,C_L}\right)$ 이 되면, 제어 전압이 낮아짐에 따라  $C_{\nu}$ 가 커져 발진기의 주파수가 낮아진다. 식 (5)의  $R_{\nu}$ 의 경우는  $r_{d_s} \ll \left(\frac{1+g_m\,r_{d_s}}{\omega\,C_L}\right)$ 이 되면, 전압이 낮아짐에 따라 점차 커지게 되고 ,  $r_{d_s} \gg \left(\frac{1+g_m\,r_{d_s}}{\omega\,C_L}\right)$ 인 경우에는 작아진다. 따라서  $r_{d_s}$ 값의 선택에 의해 주파수 가변방식이 결정된다.

그림 4의  $r_{ds}$ 는 게이트의 입력으로 제어 전압을 가지는 PMOS의 W/L 비에 의해 결정된다. PMOS의 W를 변화시켜  $r_{ds}$ 를 바꾸는 구조는 PMOS 드레인의 커 패시턴스가 커지게 되어 좋지 않다.

#### B. 쏘스 팔로워 회로

주화수 혼합기에서 사용되는 LO(Local Oscillator) 신

이 왜곡된다. 또한 쏘스 팔로워 출력이 커지게 되어 출력 임피던스를 50.0으로 만들기가 어려워진다. 따라 서 버퍼 출력신호 폭은 줄여주고 신호 레벨을 바꾸어 주는 부가회로가 필요하다.

쏘스 팔로워 출력 임피던스가 작기 때문에 전류가 커져 전력소모가 전체 발진기 회로의 40%이상을 차지한다. 또한 바이어스 회로의 면적도 커지게 되는 단점이 있다. 그림 5는 VCO의 간략화된 전체 회로도를 나타낸다.

그림 5. VCO 전체 회로도

## Ⅲ. 모의 실험 및 측정 결과

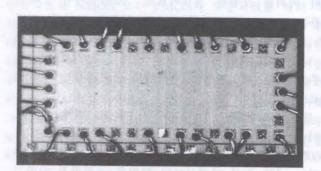

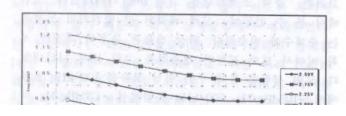

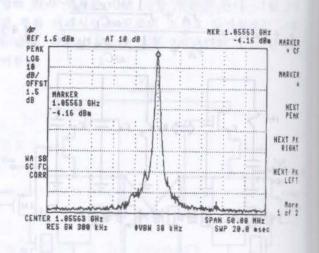

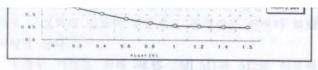

설계된 발진기는 0.25-  $\mu$ m CMOS 공정으로 제작되었다. 그림 6은 제작된 VCO의 다이 사진이다. 공급전압 2.5V에서 30mA의 전류를 소모하였는데 이는 출력단의 버퍼를 포함한 전류이므로 코어에서만 소비된전류는 40% ~ 50%정도 감소할 것으로 보인다. 그림7은 전원 및 제어 전압의 변화에 따른 주파수의 변화를 나타낸다. 그림 8은 측정된 주파수 스펙트럼을 보여주고 있다. 제어전압이 변하여도 출력파위는 =4dBm으로 측정되었다.

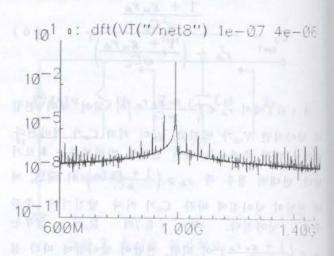

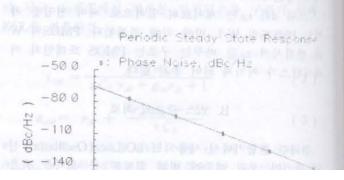

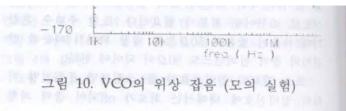

원래 의도했던 동작 주파수는 1.7GHz 대역 이였다. 그러나 실제 제작된 링 발전기는 940MHz ~ 1050MHz 영역에서 동작하였다. 이는 지연 셀에서 케 환되는 내부 도선 커패시터의 영향을 고려하지 않았기때문이다. 모의 실험에서 도선 커패시턴스의 영향을 고려한 출력 스펙트럼을 그림 9에 나타내었다. 그림에서 볼 수 있듯이 실제 제작된 링 발진기의 동작하는 주파수와 비슷하다. 위상 잡음은 추후에 측정할 계획 이여서 모의 실험한 결과만을 그림 10에 나타내었다. 모의 실험을 통해 구한 위상 잡음은 100~kHz 옵셋

호 크기가 작기 때문에 버퍼 회로의 큰 출력을 작은 신호로 바꾸어줄 회로가 필요하다. 또한 주파수 혼합 기에 사용된 발문이 50.Q으로 매칭 되었기 때문에 발 진기의 출력 임피던스도 50.Q이 되어야 한다.

쏘스 팔로워 입력신호가 풀 스윙하면 문턱전압 이 하의 입력신호에 대해서는 회로가 off되어 출력 파형 에서 -105dBc/Hz, 600-kHz 옵셋에서 -120dBc/Hz 이다.

韓田 주ル주 丹神

- 169 -

ÀÌÀü/TÙÀ1/2

위상 잡음을 줄이고 주파수 합성기의 다른 블록과의 단일칩화를 위해 풀 스윙 구조로 설계된 링 발진기를 제안하였고 이를 0.25  $\mu$ m CMOS 공정으로 제작하였으며 측정을 통하여 CMOS 주파수 합성기의 단일칩화의 가능성을 검증하였다. 또한 주파수 가변회로에 대한 이론적인 분석을 수행하였고 시뮬레이션을 통해 검증하였다. 설계된 발진기는 쏘스 팔로워에서 대부분의 전력을 소모하기 때문에 새로운 구조의 쏘스 팔로위가요구된다.

### 참 고 문 헌

- [1] Behzad Razavi, "Design of Monolithic Phase-Locked Loops and Clock Recovery Circuits -A Tutorial" IEEE Press, 1996.

- [2] Chan-Hong Park, Beomsup Kim, "A Low-Noise, 900-MHz VCO in 0.6- μ m CMOS" IEEE JSSC, vol. 34, pp. 586-591, May 1999.

- [3] Seog-jun Lee, Beomsup Kim, and Kwyro Lee, "A Novel High-Speed Ring Oscillator for Multiphase Clock Generation Using Negative Skewed Delay Scheme," IEEE JSSC, vol. 32, pp. 289-291, February 1997.

- [4] David Johns & Ken Martin, "Analog Integrated circuit Design," John Wiley & Sons, 1996.

그림 6. VCO 다이 사진

그림 8. 측정된 VCO의 주파수 스펙트럼

그림 9. 도선의 커패시턴스를 고려한 VCO의 스펙트럼 (모의 실험)

그림 7. 측정된 전원 전압 및 제어 전압에 따른 주파수 변화

- 170 -

ÀÌÀü/