TD6-4

The ou

wavefo

conduc

represe

condu

the an

ampli

maxii

betw

After

(fo)

max

## A NOVEL FREQUENCY DOUBLER USING FEEDFORWARD STRUCTURE AND DGS MICROSTRIP FOR FUNDAMENTAL AND HIGHER-ORDER COMPONENTS SUPPRESSION

#### HYO-A LEE

Dept. of Information and Communication Eng., Chonbuk Nat'l Univ., Korea E-mail: 35021004@mail.chonbuk.ac.kr

#### CHUL-WHAN LEE

Dept. of Information and Communication Eng., Chonbuk Nat'l Univ., Korea

### YONG-CHAE JEONG

Division of Electronics & Information Eng. and IDEC WG, Chonbuk Nat'l Univ., Korea

#### JONG-SIK LIM

Korean Intellectual Property Office, Korea

#### CHUL D. KIM

Sewon Teletech Inc., 1023, Kyounggi-Dong, Dongan-Gu, Anyang, Koyonggi, Korea

In this paper, a novel design concept of a frequency doubler using feedforward technique and defected ground structure(DGS) microstrip line is proposed. The feedforward loop plays a role of fundamental frequency suppression and DGS microstrip line suppresses over the 3<sup>rd</sup> order harmonic components. By using this new concept, the high suppression for the undesired signals could be achieved easily. The proposed technique is experimentally demonstrated in 1.85GHz to 3.7GHz frequency doubler. The output power of -3dBm at the frequency of 3.74GHz (2f<sub>o</sub>) is measured with 42.9dB suppression of the fundamental frequency signal (f<sub>o</sub>), 20.2dB suppression of the 3<sup>rd</sup> harmonic signal (3f<sub>o</sub>) and 29.7dB suppression of the 4<sup>th</sup> harmonic signal (4f<sub>o</sub>). The conversion loss of -2.34dB ~ -5.8dB at the bandwidth of 100MHz, the phase noise of -97.51dB/Hz(@10KHz) were measured.

## 1. Introduction

There is a demand for high stability and low phase noise signal source in microwave and millimeter-wave communication and radar systems. These sources can be easily obtained by multiplying low frequency signal that has high stability and low phase noise relatively. Generally multiplier include a fundamental component and harmonic components besides multiplied signal, so it makes serious problems when multiplier is operated with other microwave circuits such as mixer and amplifier and so on. To solve these problems, a quarterwavelength open stub or balanced multiplier design is used to suppress fundamental frequency component. But these methods show limitation of fundamental signal suppression about 25dB generally. Also a band pass filter can be used for suppression of the fundamental and several harmonic signals. But the insertion loss of a band pass filter causes multiplied signal level to diminishment of multiplied signal level, and impossible to make fully monolithic transceiver because of high Q-factor bandpass filter<sup>[1]</sup>[12].

In this paper, a new structure of doubler that suppresses fundamental frequency component and the 3<sup>rd</sup> order harmonic signals without band pass filter is proposed. Proposed method is composed of feedforward technique that can effectively suppress intermodulation distortion in power amplifier design and defected ground structure(DGS) microstrip line realized by etching a few dumb-bell shaped patterns on the ground plane of microstrip line. Feedforward technique is used to suppress the fundamental signal and DGS microstrip line is used to suppress 3<sup>rd</sup> order harmonic components.

### 2. Theory

## 2.1. General frequency doubler

1118

ent

by

the

to

The output current waveform to input voltage waveform of the transistor according to conduction angle is showed in figure 1. The tamonic signals generation to the bias is expresented by (1) and (2), where  $\alpha$  is conduction angle of input signal. Figure 2 shows the amplitudes of the DC to  $5^{th}$  harmonic signal. When the conduction angle is  $120^{\circ}$ , the implitude of the  $2^{nd}$  harmonic signal is maximum, therefore a bias point of transistor must be selected in the vicinity of pinch-off, between class B and C.

After the bias selection, the input and the output put have been matched by fundamental signal (6) and 2<sup>nd</sup> harmonic signal (2f<sub>o</sub>) respectively, to maximize the 2<sup>nd</sup> harmonic component in the output port.

$$I_{i} = \frac{1}{\pi} \int_{\frac{\alpha}{2}}^{\alpha} \frac{I_{max}}{1 - \cos \frac{\alpha}{2}} \left( \cos \omega t - \cos \frac{\alpha}{2} \right) \cos n\omega t \, d\omega t$$

(1)

$$I_{\pm} = \frac{1}{2\pi} \frac{I_{\max}}{1 - \cos\frac{\alpha}{2}} \left( 2\sin\frac{\alpha}{2} - \alpha\cos\frac{\alpha}{2} \right)$$

(2)

# 22 The frequency doubler using the feedforward structure

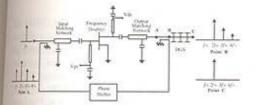

The feedforward technique is widely used to amove the intermodulation distortion in power implifier design and it has a wide operating frequency band and hardly oscillates because there is no feedback path. In this paper, the 1st kep scheme of feedforward technique has been used for fundamental frequency suppression and figure 3 shows block diagram of the doubler. Because active multiplier attenuates the findamental signal level theoretically, the indamental signal can be suppressed by disting the coupling coefficients of the multiplier and the phase constant of the phase librarily.

## 13The DGS microstrip line

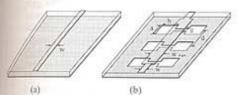

biting a few dumb-bell shaped patterns on the gound plane located just below microstrip line acquivalent to increase of serial inductance of tasmission line impedance. The width of the DOS microstrip line must be broader than that of the conventional microstrip line to maintain the secific characteristic impedance. That is

equivalent to increase of shunt capacitance of transmission line impedance. Increasing the series inductance and the shunt capacitance induces increase of phase constant and slow-wave effect. So the DGS microstrip line contributes to circuit downsizing. If we apply the DGS microstrip line at output terminal of frequency doubler, the harmonic signals over the 3<sup>rd</sup> order can be suppressed effectively due to low pass filtering characteristic of DGS microstrip line<sup>[5]</sup>.

# 2.4. The frequency doubler using the feedforward structure and the DGS

In this paper, the feedforward technique and the DGS transmission line are used to suppress over the 3<sup>rd</sup> order harmonics as well as fundamental frequency. Figure 3 shows the block diagram and the expectable frequency spectra. The structure of the DGS microstrip line is represented in figure 4. The defected cell parameters are a=4mm, b=3.5mm, d=9.3mm, g=0.5mm, w=2.38mm, w<sub>dgs</sub>=4.37mm. Adjusting the etching cell parameters, the DGS microstrip line controls the low-pass filtering characteristic under 2<sup>nd</sup> harmonic frequency. EM simulation is done with Ansoft HFSS v.8.0.

## 3. Experiment and Measured results

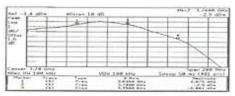

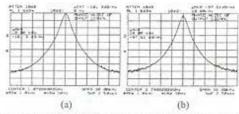

To show the validation of proposed frequency doubler, we designed frequency doubler multiplying 1.87GHz to 3.74GHz. The used transistor is ATF10136 MESFET of HP and the drain voltage is set 1.2V and the gate voltage is -1.25V to operate near pinch-off voltage region, between class B and C. Then we extracted the input and output matched points using the loadpull method and implemented matching circuits using ADS of Agilent. Figure 5 shows the output characteristic of the fabricated singleended frequency doubler, which spectra shows the fundamental frequency signal and over the 3rd order harmonic signals as well as the 2nd order multiplied signal. The single-ended doubler has -2.55dB conversion loss and -25.94dB suppression of the fundamental signal for 0dBm input signal. Figure 6 shows the output characteristic of the frequency doubler that suppresses the fundamental signal by applying the feedforward structure. The result shows that the fundamental frequency signal is suppressed about 42,2dB. Figure 7 shows the

fabrication characteristic of the DGS microstrip line. It shows low-pass filter characteristic that cut-off frequency is 4GHz and insertion loss is 0.4dB at 3.74GHz and attenuation value at 5.55GHz is more than 23dB. This means that the DGS microstrip line can terminate over the 3rd order harmonic signals. Figure 8 shows the characteristic of frequency doubler applying the feedforward structure and DGS microstrip line. For the input power of 0dBm, the output power level of frequency doubler is -3dBm with 42.9dB, 20.2dB and 29.7dB suppression of the fundamental, the 3rd harmonic and the 4th respectively. harmonic signal, Table summarizes signal levels of the fabricated frequency doubler. We can see the fundamental frequency signal level before using feedforward structure and after using feedforward structure. Figure 9 shows the conversion loss according to the frequency variation. The conversion loss is -2.9dB at the 3.74GHz and the variation of the conversion loss is -2.34dB(@3.71GHz) to -5.8dB (@3.79GHz), ±1.73dB within 100MHz bandwidth. Figure 10 shows the input and output phase noise characteristic of frequency Output phase noise measurement doubler. shows 97.51dBc/Hz (@10KHz offset) in case of input signal -101.3dB, which is better than the theoretical phase worse condition, 20logN = 20log(2) = 6dB, by 2.2dB. Maybe this result is due to elimination of the fundamental signal and matching of over the 3rd order harmonic signals. Figure 11 shows the photograph of the fabricated frequency doubler. The DGS structure is circled by dashed line. Table 2 summarizes the characteristics of the fabricated frequency doubler.

4. Conclusion

In this paper, the new design technique of the frequency doubler was proposed to obtain sources that have high stability and low phase noise. The fundamental frequency signal was suppressed by using feedforward structure and over the 3<sup>rd</sup> order harmonics were suppressed by using DGS structure. As a result, variations of suppression were 42.9dB, 19.2dB and 29.7dB for the fundamental, the 3<sup>rd</sup> order harmonic and the 4<sup>th</sup> order harmonic signal, respectively. Because the fabricated doubler consists of a transistor, diodes and hybrid circuits, overall circuits can be integrated in monolithic form. We expect that monolithic frequency doubler, that doesn't contain the fundamental and over 3<sup>rd</sup>

harmonics, can contribute to improve communication quality without any high () bandpass filter.

## Acknowledgements

The authors wish to acknowledge the assistance and support of the Agilent Technologies Kora Ltd. and the Ansoft Korea.

#### References

- [1] Donald G. Thomas, Jr. and G. R. Branner, "Optimization of Active Microwave Frequency Multiplier Performance Utilizing Harmonic Terminating Impedances," *IEEE Trans. Microwave Theory Tech.*, vol. MIT-44, no. 12, pp. 2617-2624, Dec 1996.

- [2] Staffan P. O. Bruce, Frank J. Beißwanger, I. F. Luy, Uwe Erben, "Design and Realization of a Millimeter-Wave Si/SiGe HBT Frequency Multiplier," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-46, no. 5, pp. 695-700, May 1998

- [3] N. Siripon, M. Chongcheawchamnan, and I. D. Robertson, "Novel Frequency Doubler using Feedforward for Fundamental Frequency Component Suppression," IEEE MTT-S Digest pp. 1345-1348, 2001.

- [4] Yong-Chae Jeong, "A Feedforward Power Amplifier with Loops that can reduce RX Band Noises as well as Intermodulation Distortion Signals," Microwave Journal, vol. 45, no. 1, pp. 80-91, Jan 2001.

- [5] Si-Gyun Jeong, Do-Kyeong Hwang, Yong-Chae Jeong, Chul-Dong Kim, "Amplifier design using λ/4 High Impedance Bias Line with Defect Ground Structure (DGS)," IEEE MTT-S, Digest, 2001.

Fig. 1. Output current waveform to conduction angle

Fig. 2. Amplitude comparison of the harmonic components to conduction angle

111

Fig. 3. Bloc ture ar

Fig. 4. (a)

Fig. 5. 0

Fig. 6. (

Fig. 7.

11111111

to improve at any high Q

e the assistance nologies Korea

R. Branner, Microwave ince Utilizing inces," IEEE vol. MTT-1996.

iβwanger, J. I Realization SiGe HBT E Trans. ITT-46, no.

man, and I.

y Doubler

indamental

on," IEEE

11.

ard Power educe RX odulation Journal,

g, Yong-Amplifier has Line )." IEEE

nents

Fig.3. Block diagram of doubler using feedforward structure and DGS

Fig. 4. (a) Layout of a standard microstrip line (b) Layout of DGS microstrip line

Fig. 5. Output characteristic of the fabricated frequency doubler

Fig. 6. Output characteristic of the frequency doubler using feedforward.

Fig. 7. Characteristic of the fabricated DGS microstrip line.

Fig. 8. Output characteristic of the frequency doubler using feedforward and DGS

Table 1.

Output characteristic of each doubler structure[dBm]

|                     | Pro    | P260  | Pin    | P <sub>4fs</sub> |

|---------------------|--------|-------|--------|------------------|

| Only Doubler        | -25/94 | -2.55 | -46.8  | -38.74           |

| F.F+ Doubler        | -68.1  | -2.64 | -46.24 | -40.08           |

| F.F+DGS<br>+Doubler | -68.88 | -3,02 | -66.02 | -68.45           |

Fig. 9. Conversion loss according to the frequency varia-

Fig. 10. Phase noise measurement results of the fabricated frequency doubler (a) input signal (b)output signal

Fig. 11. Photographs of the fabricated frequency doubler (a)Top view (b) Bottom view

Table 2. Output Characteristic of the frequency doubler

| Item                    | Results      | Unit |

|-------------------------|--------------|------|

| Frequency range         | 3.69 ~ 3.79  | GHz  |

| Bandwidth               | 100          | MHz  |

| Output power            | -2.345.8     | dBm  |

| Conversion loss         | -2.34 ~ -5.8 | dB   |

| P1dB                    | -1.5         | dBm  |

| Phase noise improvement | 2.2          | dB   |

| Current                 | 14           | mA   |

| Voltage                 | 1.2          | V    |