# Design of Group Delay Time Controller Based on a Reflective Parallel Resonator

Girdhari Chaudhary, Heungjae Choi, Yongchae Jeong, Jongsik Lim, and Chul Dong Kim

In this paper, a group delay time controller (GDTC) is proposed based on a reflection topology employing a parallel resonator as the reflection termination. The design equations of the proposed GDTC have been derived and validated by simulation and experimental results. The group delay time can be varied by varying the capacitance and inductance at an operating frequency. To show the validity of the proposed circuit, an experiment was performed for a wideband code division multiple access downlink band operating at 2.11 GHz to 2.17 GHz. According to the experiment, a group delay time variation of  $3\pm0.17$  ns over bandwidth of 60 MHz with excellent flatness is obtained.

Keywords: Group delay time controller, resonance circuit, varactor diode, variable inductor.

#### I. Introduction

In mobile communications systems, transmitter performance is mainly limited by nonlinearity of power amplifiers (PAs). To improve the nonlinear performance of PAs, various types of linearization techniques, such as digital/analog predistortion, feedforward, direct/indirect feedback, polar loop, and Cartesian loop, have been proposed [1]-[4]. To achieve a broadband linearization of PAs, group delay (GD) time matching as well as amplitude and out-of-phase matching are very important design issues on the operating frequency band. A coaxial cable or GD bandpass filter is used as a GD time matching component in the conventional linear PAs. The GD time controller circuit is beneficial for linearization of PAs.

There have been several efforts to design GD time adjustor (GDTA) circuits [5]-[14]. In [5], the GD synthesizer circuit is based on a reflection topology employing resistance, inductance, and capacitance (RLC) series circuits in MMIC technology. The GD circuit presented in [6] changes the RF paths to obtain the different fixed GD times using RF switches. However, the microwave GDTA circuits presented in [7], [8] can control the GD time but have too narrow bandwidth, few MHz, and a large circuit size. The feedforward linear PA using the narrowband GDTA showed the benefit of the GDTA circuit in the design and operation of linear PA [9].

The variable GD line presented in [10] consists of a directional coupler with a periodic varactor load. The GD time can be controlled by changing the coupling coefficient of the coupler during the varactor loads adjustment. However, the GD variation is very slight and the time delay flatness is in need of improvement. Likewise, the circuit presented in [11] has a low GD tuning range and a narrow operating bandwidth.

The literature surveys show some effort to design CMOS

Manuscript received Nov. 16, 2010, revised Oct. 4, 2011; accepted Dec. 5, 2011.

This work was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (2010-0011764).

Girdhari Chaudhary (phone: +82 63 270 2458, girdharic@jbnu.ac.kr) and Yongchae Jeong (ycjeong@jbnu.ac.kr) are with the Department of Electronics and Information Engineering, IT Convergence Research Center, Chonbuk National University, Jeonju, Rep. of Korea.

Heungjae Choi (ChoiH1@cardiff.ac.uk) is with the Center for High Frequency Engineering, Cardiff University, Cardiff. UK.

Jongsik Lim (jslim@sch.ac.kr) is with the Department of Electronics and Information Engineering, Soonchunhyang University, Asan, Rep. of Korea.

Chul Dong Kim (chuldkim@sewon-teletch.co.kr) is with Sewon Teletech Inc., Anyang, Rep. of Korea.

http://dx.doi.org/10.4218/etrij.12.0110.0689

variable GD lines [12], [13]. The approach discussed in [12] is based on a left-handed transmission line with cascaded metaloxide semiconductor (MOS) varactors and shunt inductors.

The CMOS reflection-type variable GD line at a *K*-band presented in [13] consists of a 3-dB directional coupler and two-parallel resonator loads at through and coupled ports of the coupler. These circuits have demonstrated wideband operation but very short tuning (only a few picoseconds) range of GD time.

Several microwave circuits, such as phase shifter, attenuator, and amplifier, have been demonstrated using reflection topology [14]-[16].

In this paper, a group delay time controller (GDTC) based on the reflection topology employing parallel inductance and capacitance (LC) resonator circuits as the reflection termination is proposed to overcome the very narrow frequency bandwidth limitation of the previously presented GDTA circuits. The design equations of the proposed GDTC have been derived and have been validated through experimentation.

## II. Design and Implementation

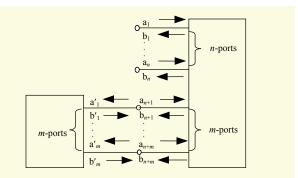

Figure 1 illustrates the port reduction method to derive the general design equation for the proposed GDTC circuit. By terminating the *m*-ports as a load network of (n+m)-ports, a new *S*-matrix of the reduced *n*-ports network can be obtained as

$$[S] = S'_{11} + S'_{12} [S_{L}^{-1} - S'_{22}]^{-1} S'_{21}, \qquad (1)$$

where  $S_L$  is the *S*-matrix of a network when *m*-ports are terminated with loads, and  $S'_{ii}$  is the *S*-matrix of the (n+m)-ports network [17].

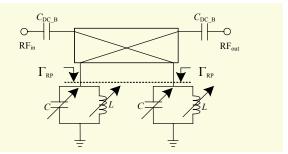

Figure 2 shows the proposed reflection type GDTC that consists of a 3-dB 90° hybrid coupler and LC parallel resonators as reflection termination. Since the through and the coupling ports of the hybrid coupler are terminated with parallel LC resonators, the  $S_L$ -matrix of the load network can be expressed as

$$\begin{bmatrix} S_{\rm L} \end{bmatrix} = \begin{bmatrix} \Gamma_{\rm RP} & 0\\ 0 & \Gamma_{\rm RP} \end{bmatrix}, \tag{2}$$

where  $\Gamma_{RP}$  is the input reflection coefficient of the LC parallel resonator termination. Assuming the coupler to be lossless, perfectly matched, and having infinite isolation, the new reduced *S*-matrix of the proposed 2-port GDTC circuit is obtained with an *S*-matrix of a 4-port coupler and (2), which is given as

$$\begin{bmatrix} S \end{bmatrix} = \begin{bmatrix} 0 & -j\Gamma_{\rm RP} \\ -j\Gamma_{\rm RP} & 0 \end{bmatrix}.$$

(3)

The input reflection coefficient of the LC parallel resonator termination can be expressed as

Fig. 1. Illustration of port-reduction method.

Fig. 2. Circuit diagram of proposed GDTC.

$$\Gamma_{\rm RP} = \frac{\left(Y_0 \omega L\right)^2 - \left(\omega^2 L C - 1\right)^2}{\left(Y_0 \omega L\right)^2 + \left(\omega^2 L C - 1\right)^2} + j \frac{2Y_0 \omega L \left(1 - \omega^2 L C\right)}{\left(Y_0 \omega L\right)^2 + \left(\omega^2 L C - 1\right)^2},$$

(4)

where  $Y_0$  is the termination admittance. Therefore, the transmission coefficient magnitude and phase of the proposed GDTC circuit are given as

$|S_{21}|$

$$=\sqrt{\left(\frac{2Y_{0}\omega L(1-\omega^{2}LC)}{(Y_{0}\omega L)^{2}+(\omega^{2}LC-1)^{2}}\right)^{2}+\left(\frac{(\omega^{2}LC-1)-(Y_{0}\omega L)^{2}}{(Y_{0}\omega L)^{2}+(\omega^{2}LC-1)^{2}}\right)^{2}},$$

(5)

$$\angle S_{21} = \tan^{-1} \left( \frac{\left( \omega^2 L C - 1 \right)^2 - \left( Y_0 \omega L \right)^2}{2 Y_0 \omega L \left( 1 - \omega^2 L C \right)} \right).$$

(6)

The GD gives a measure of how long it takes to traverse a system. Mathematically, it is defined as

$$\tau = -\frac{d\angle S_{21}}{d\omega}.$$

(7)

Therefore, the GD time of the proposed GDTC circuit is obtained using (6) and (7) as

$$\tau\Big|_{\omega=\omega_0} = -\frac{d\angle S_{21}}{d\omega}\Big|_{\omega=\omega_0} = \frac{4}{Y_0\omega_0^2 L} = 4Z_0C , \qquad (8)$$

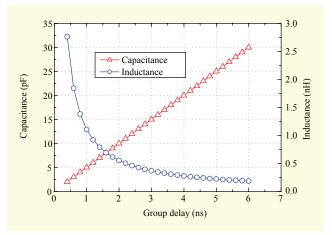

Fig. 3. Calculated value of capacitor and inductor for specific GD at 2.14 GHz.

where  $Z_0$  is the termination impedance. From (8), the GD time variations can be obtained by varying the inductance and capacitance, assuming a resonance condition at the operating frequency.

Figure 3 shows the calculated capacitance and inductance to obtain specific GD times at the operating frequency. As shown in Fig. 3, the GD time is proportional to capacitance and inversely proportional to the inductance.

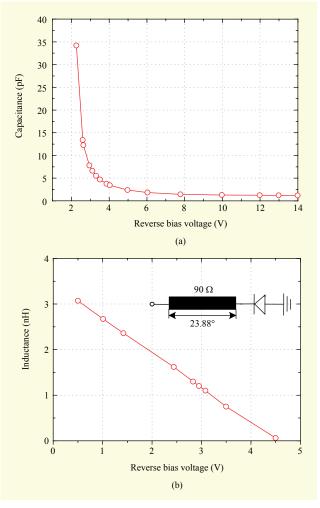

The required variable capacitance in this work was implemented with the varactor diode SMV1233-011LF of Skyworks, by controlling the reverse bias voltage. Similarly, the required variable inductance was obtained with the high impedance transmission line terminated with the varactor diode [8].

Figure 4 shows the measurement results of varactor diode and variable inductor at a frequency of 2.14 GHz. In this work, a 90- $\Omega$  high-impedance transmission line with electrical length of 23.88° is used to obtain the required variable inductance.

#### III. Simulation and Experimental Results

To show the validity of the proposed GDTC circuit, the simulation and experiment were performed for the wideband code division multiple access (WCDMA) downlink band operating at 2.11 GHz to 2.17 GHz.

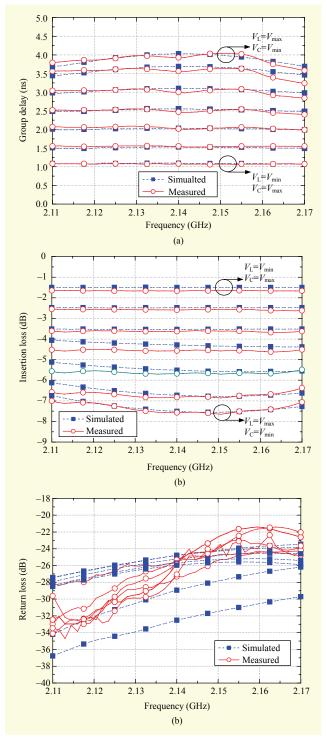

The simulation was done using ADS 2006A. In the simulation, the equivalent circuit of the varactor diode provided by the manufacturer was used. Figures 5(a), 5(b), and 5(c) show the simulated and measured GD time variation, the insertion loss characteristics, and return loss characteristics, respectively. The simulated GD time and the insertion loss variations are  $3\pm0.16$  ns and 5.9 dB within the excellent insertion loss flatness of 0.5 dB, respectively. The maximum return loss is -23.86 dB in the passband for the overall GD

Fig. 4. Measurement results at 2.14 GHz of (a) varactor diode and (b) variable inductor.

time variation range.

From the experiment, the GD variation of 3±0.17 ns over a 60-MHz bandwidth with the excellent insertion loss flatness is obtained. The insertion loss variation is 6 dB, which is due to the variation of the junction resistance in the varactor diode according to the control bias voltage variation. The insertion loss variation can be easily compensated with an automatic gain control amplifier in the linear PA system.

The insertion loss flatness is less than 0.57 dB at fixed GD and the maximum return loss is -22.18 dB in the passband for the overall GD variation range. The reverse bias voltage variations of the varactor diodes for inductance and capacitance are 0.01 V to 3.53 V and 3.69 V to 13.18 V, respectively.

If the insertion loss flatness higher than 0.57 dB can be accepted, larger GD time variation can be obtained. So, a trade-off among the GD variations, insertion loss, and GD flatness should be considered. A slight of difference in simulation and measurement results of return loss

Fig. 5. Simulated and measured results: (a) GD time variation, (b) insertion loss characteristics, and (c) return loss characteristics (bias voltage variation:  $V_{\rm L}$ : 0.01 V to 3.53 V and  $V_{\rm C}$ : 3.69 V to 13.18 V).

characteristics is due to connecting elements at varactor diodes.

Table 1 shows the performance comparison among the previously presented GDTCs and the proposed GDTC circuit.

Table 1. Performance comparison of proposed GDTC circuit.

|           | Frequency               | GD<br>variation | BW      | Proces          |

|-----------|-------------------------|-----------------|---------|-----------------|

| [7]       | 869 MHz to<br>894 MHz   | 1.0 ns          | 25 MHz  | PCB             |

| [8], [9]  | 908.5 MHz to<br>914 MHz | 3.0 ns          | 5.5 MHz | PCB             |

| [11]      | N/A                     | 1.0 ns          | N/A     | PCB             |

| [12]      | 18 GHz to<br>24 GHz     | 0.02 ns         | 6 GHz   | CMOS<br>0.18 μm |

| [13]      | 23 GHz to<br>25 GHz     | 0.087 ns        | 2 GHz   | CMOS<br>0.13 µm |

| This work | 2.11 GHz to<br>2.17 GHz | 3.0 ns          | 60 MHz  | РСВ             |

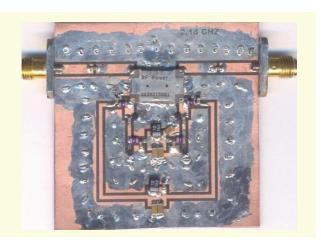

Fig. 6. Photograph of fabricated GDTC circuit.

The bandwidth of the proposed GDTC is much broader than those of the previous GDTCs within the microstrip technology. Figure 6 shows a photograph of fabricated GDTC circuit.

## **IV.** Conclusion

In this paper, a design of a reflective-type GDTC consisting of a 3-dB 90° hybrid coupler and reflective parallel resonators has been investigated. The general design equations of the proposed circuit are derived and validated through experimentation. The simulation and experiment were performed for the WCDMA downlink frequency operating at 2.11 GHz to 2.17 GHz. The GD time and insertion loss flatness are excellent within the operating band having  $3\pm 0.17$  ns of GD time variation.

The proposed GDTC circuit achieved the broadest bandwidth among the previously reported GD time circuits with an additional advantage of circuit size reduction. The proposed GDTC circuit is expected to play an important role in broadband communication systems for which critical GD time matching is required.

#### References

- S.C. Cripps, Advanced Techniques in RF Power Amplifiers Design, Norwood, MA: Artech House, 2006.

- [2] P.B. Kenington, *High Linearity RF Amplifier Design*, Norwood, MA: Artech House, 2000.

- [3] R.N. Braithwaite, "Positive Feedback Pilot System for Second Loop Control in a Feedforward Power Amplifier," *IEEE Trans. Circuits Syst.*, vol. 55, no. 10, Nov. 2008, pp. 3293-3305.

- [4] Y. Jeong et al., "A Feed-Forward Amplifier Using an Equal Group Delay Signal Cancellation Technique," *Microw. J.*, vol. 50, no. 50, Apr. 2007, pp. 126-134.

- [5] S. Lucyszyn and I.D. Roberton, "Analog Reflection Topology Building Blocks for Adaptive Microwave Signal Processing Applications," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 3, Mar. 1995, pp. 601-611.

- [6] I. Bhal and P. Bhartia, *Microwave Solid Circuit Design*, New York: Wiley, Apr. 2003.

- [7] S. Park et al., "Group Delay Adjustor Using Resonance Circuit with Varactor Diode," *IEEE Conf. Proc. Asian Pacific Microw.*, Dec. 2005, pp. 2176-2179.

- [8] S. Park, H. Choi, and Y. Jeong, "Microwave Group Delay Time Adjustor Using Parallel Resonator," *IEEE Microw. Wireless Comp. Lett.*, vol. 17, no. 2, Feb. 2007, pp. 109-111.

- [9] H. Choi and Y. Jeong, "Design of a Microwave Group Delay Time Adjustor and Its Application to a Feedforward Power Amplifier," *Microw. J.*, no. 51, no. 2, Feb. 2008, pp. 88-100.

- [10] J.D. Fredrick, Y. Wang, and T. Itoh, "A New Circuit Topology for Continuous Group Delay Synthesis," *IEEE Microw. Wireless Comp. Lett*, vol. 12, no. 3, Mar. 2002, pp. 85-87.

- [11] W. Tang and H. Kim, "Compact, Tunable Large Group Delay Line," *IEEE 10th Ann. Wireless Microw. Tech. Conf.*, Apr. 2009, pp. 1-3.

- [12] C. Kim et al., "A K-Band CMOS Voltage Controlled Delay Line Based on an Artificial Left-Handed Transmission Line," *IEEE Microw. Wireless Comp. Lett.*, vol. 18, no. 11, Nov. 2008, pp. 731-733.

- [13] P.C. Ko et al., "A 87 Pico-Second CMOS Variable Delay Line Incorporating the Parallel Resonator Loads in K-Band," *IEEE MTT-S IMS Digest*, June 2011, pp. 1-4.

- [14] D. Kim et al., "A Wide-Band Reflection-Type Phase Shifter at S-Band Using BST Coated Substrate," *IEEE Trans. Microw. Theory Tech.*, vol. 50, no. 12, Dec. 2002, pp. 2903-2909.

- [15] S. Nam et al., "Wideband Reflection Type MMIC Attenuator with Constant Phase," *Electron. Lett.*, vol. 34, no. 1, Jan. 1998, pp. 91-93.

- [16] K. Miyaguchi et al., "An Ultra-Broad-Band Reflection-Type

Phase-Shifter MMIC with Series and Parallel LC Circuits," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 12, Dec. 2001, pp. 2446-2452.

[17] H.-R. Ahn, Asysmmetric Passive Components in Microwave Integrated Circuits, Wiley, Sept. 2006.

**Girdhari Chaudhary** received his BE and MTech in electronics and communication engineering from Nepal Engineering College (NEC), Kathmandu, Nepal, and Malaviya National Institute of Technology (MNIT), Jaipur, India, in 2004 and 2007, respectively. He is currently working toward his PhD at

Chonbuk National University, Jeonju, Rep. of Korea. His research interests include multiband passive circuits, negative group delay filters, high efficiency power amplifiers, and RF energy harvesting systems.

Heungjae Choi received his BS, MS, and PhD in electronic engineering from Chonbuk National University, Jeonju, Rep. of Korea, in 2004, 2006, and 2011, respectively. He is currently a research associate with the Center for High Frequency Engineering, Cardiff University, Cardiff, UK. His current research

interests include highly efficient RF PA design, broadband linearization techniques, and active load-pull techniques for modulated waveform. He has authored or co-authored over 30 papers in international journals and conference proceedings. Dr. Choi received the Outstanding Achievement Award of the Student High-Efficiency Power Amplifier Design Competition at the IEEE MTT-S International Microwave Symposium in 2008 and the Consolation Prize at the Human Tech Thesis Prize Awards in 2010, sponsored by Samsung Electronics Company.

Yongchae Jeong received his BSEE, MSEE, and PhD in electronics engineering from Sogang University, Seoul, Rep. of Korea, in 1989, 1991, and 1996, respectively. From 1991 to 1998, he worked as a senior engineer with Samsung Electronics. Since 1998, he has been with the Division of Electronic Engineering,

Chonbuk National University, Jeonju, Rep. of Korea. From July 2006 to December 2007, he joined the Georgia Institute of Technology as a visiting research professor. Currently, he is a professor and associate dean of the College of Engineering, and a member of the IT Convergence Research Center at Chonbuk National University. He teaches and conducts research in the areas of microwave devices, basestation amplifiers, nonlinear device and system linearizing technology, and RFIC design. Dr. Jeong is a senior member of IEEE as well as a member of Korea Institute of Electromagnetic Engineering and Science (KIEES). He has authored or co-authored over 100 papers in international journals and conference proceedings.

Jongsik Lim received his BS and MS in electronic engineering from Sogang University, Seoul, Rep. of Korea, in 1991 and 1993, respectively, and his PhD from the School of Electrical Engineering and Computer Science, Seoul National University, in 2003. In 1993, he joined ETRI, Daejeon, Rep. of Korea, and was

with them for 6 years in the Satellite Communications Division as a senior member of the research staff. At ETRI, he was one of the key members in developing MMIC LNA and SSPA for the 20/30-GHz satellite transponder. From March to July in 2003, he worked in the Division of Information Technology Brain Korea 21 Project at Seoul National University as a post doctoral fellow. He also gave lectures in the graduate schools of Soonchunhyang University and Soongsil University. He worked as a patent examiner in the Korean Intellectual Property Office (KIPO) from July 2003 to September 2004. In September 2004, he re-joined ETRI and worked in the Antenna Technology Research Team/Radio Technology Group as a senior research member. Since March 2005, he has been a faculty member of the Department of Electrical and Communication Engineering, Soonchunhyang University, Rep. of Korea. His current research interests include the design of passive and active circuits for RF/microwave and millimeter-wave with MIC/MMIC technology, modeling of active devices, design of high-power amplifiers for mobile communications, applications of periodic structure to RF/microwave circuits, and modeling of passive structure having periodic structures. Dr. Lim is a member of IEEE, IEICE, and Korea Institute of Electromagnetic Engineering and Science (KIEES).

**Chul Dong Kim** received his BS in electronic engineering from Seoul National University, Seoul, Rep. of Korea, in 1971, and his PhD in electronic engineering from the University of Wisconsin in 1985. He is the president and CEO of Sewon Teletech, Inc., a company specializing in RF power amplifiers.