# Arbitrary Prescribed Wideband Flat Group Delay Circuits Using Coupled Lines

Girdhari Chaudhary<sup>10</sup>, Member, IEEE, and Yongchae Jeong, Senior Member, IEEE

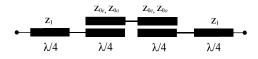

Abstract—This paper presents the analytical design of transmission-type arbitrary prescribed wideband flat group delay (GD) circuits (type-I and type-II) using  $\lambda/4$  coupled lines. The GD circuit type-I consists of two sections of coupled lines, whereas the GD circuit type-II consists of  $\lambda/4$  transmission lines (TLs) at input and output, in addition to coupled lines. The additional  $\lambda/4$  TLs at input-output ports in GD circuit type-II provide more freedom to obtain larger GD, as compared to type-I, without fabrication difficulties. The analytical analysis shows that the wideband flat GD response can be obtained by selecting the appropriate even- and odd-mode impedances of coupled lines and the characteristic impedance of TLs. To obtain the arbitrary prescribed wideband flat GD response, the closed-form analytical design equations are provided. For experimental validation of the proposed structures, prototypes of GD circuits (type-I and type-II) are designed and fabricated at the center frequency of 2 GHz. The measurement results agree well with the simulation and theoretical predicted results.

*Index Terms*—Analog radio-signal processing, arbitrary wideband flat group delay (GD) response, coupled lines, signal cancellation, transmission-type circuit.

## I. INTRODUCTION

**M** ICROWAVE circuits/filters that provide the desired group delay (GD) response with respect to frequency have various applications in communication systems including real-time analog radio-signal processing, RF self-interference cancellation in-band full-duplex radio, and signal cancellation in feed-forward amplifier [1]–[5]. The GD can be investigated by examining the frequency-dependent phase variation of transmitting scattering parameter, which can be mathematically defined as

$$\tau_g = -\frac{d\varphi}{d\omega}.\tag{1}$$

The flat GD in filters can be achieved by two approaches. The first one is to use an external all-pass GD circuits cascaded with a filter [6]–[21], which can increase circuit size and

Manuscript received June 27, 2017; revised August 30, 2017, October 25, 2017, and November 13, 2017; accepted November 19, 2017. Date of publication December 18, 2017; date of current version April 3, 2018. This work was supported by the Korean Research Fellowship Program through the National Research Foundation (NRF) of Korea funded by the Ministry of Science and ICT under Grant 2016H1D3A1938065 and in part by the Basic Science Research Program through the NRF of Korea funded by Ministry of Education, Science and Technology under Grant 2016R1D1A1B03931400. (*Corresponding author: Yongchae Jeong.*)

The authors are with the Division of Electronics Engineering, IT Convergence Research Center, Chonbuk National University, Jeonju 54896, South Korea (e-mail: girdharic@jbnu.ac.kr; ycjeong@jbnu.ac.kr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2017.2779515

insertion loss. All-pass GD circuits can be categorized into reflection and transmission types.

Reflection-type all-pass GD circuits can be realized by terminating coupled and through ports of a 3-dB hybrid coupler with one-port GD circuit, and the GD response of resulting two-port network is added up GD responses of the hybrid and one-port terminating circuit [6], [7]. A coupled-resonator network approach was utilized to design the GD equalizers using optimization procedures in [8] and [9]. A narrowband one-port circuits with an arbitrary prescribed GD response was synthesized in [10]. Later, this technique was improved and applied to the design of reflective GD circuits based on shunt stubs and stepped-impedance lines [11], alternating K/Jinverters and  $\lambda/4$  transmission line (TL) resonators [12], [13]. However, these techniques require complex iterative procedures for transformation of the prescribed GD problem from band-pass domain to the low-pass domain using a one-port ladder network, and again, the transformation of the synthesized low-pass network back to the band-pass domain, for implementation in a specific technology.

Transmission-type all-pass GD circuits are realized using multisection coupler-based superconductive delay [14], cascading of all-pass networks [15], [16], and noncommensurate coupled lines by multiconductor TL technique [17]. However, this structure requires genetic optimization technique to implement final structure. Similarly, wideband all-pass GD circuits were synthesized by using uniform and nonuniform commensurate C- and D-sections [18], [19], multilayer broadside coupled lines GD circuit for analog signal processing [20]. However, these works require an iterative design procedure to map arbitrary prescribed GD problem from band-pass domain to low-pass domain and again back to bandpass domain for obtaining the optimum circuit parameters. Similarly, the transmission-type GD lines had been realized by employing a transversal filter structure, were realized with the reverse of a distributed amplifier [21], and required complex iterative procedures to obtain a large number of tap coefficients for specified GD response.

The second approach is to design self-equalized or linear-phase filters which can be achieved by imposing linear-phase requirement in addition to the amplitude requirement [22]–[27]. However, these techniques require crosscoupling among nonadjacent resonators to produce more than one signal path or controlling sign of cross-coupling to place the transmission zeros on the right half plane. In addition, it is also difficult to specify and design arbitrarily prescribed flat GD filters directly in band-pass domain using these techniques.

0018-9480 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

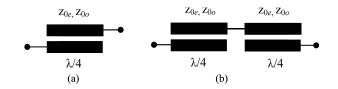

Fig. 1. (a) Coupled line and (b) proposed structure of wideband GD circuit type-I.

In this paper, arbitrarily prescribed wideband flat GD circuits are presented based on coupled lines. This paper shows an alternative way to realize flat GD filters which are very simple and do not require any cross-coupling among nonadjacent resonators or controlling sign of cross-coupling or any kind of transformation to obtain the required circuit parameters. The closed-form analytical design equations are provided to obtain the required circuit parameters for the arbitrarily prescribed wideband flat GD response without any optimization procedure.

# II. MATHEMATICAL ANALYSIS

Fig. 1(a) shows the structure of  $\lambda/4$  coupled lines, where the coupled and through ports are open circuited [28]. The evenand odd-mode impedances of coupled line are normalized with port impedance  $Z_0$  and denoted by  $z_{0e}$  and  $z_{0o}$ , respectively. Assuming  $z_c = \sqrt{z_{0e} z_{0o}}$ , normalized  $z_{0e}$  and  $z_{0o}$  are expressed as follows [28], [29]:

$$z_{0e} = z_c \sqrt{\frac{1 + C_{\text{eff}}}{1 - C_{\text{eff}}}} \qquad z_{0o} = z_c \sqrt{\frac{1 - C_{\text{eff}}}{1 + C_{\text{eff}}}}$$

(2)

$$C_{\rm eff} = \frac{z_{0e} - z_{0o}}{z_{0e} + z_{0o}} \tag{3}$$

where  $C_{\text{eff}}$  is coupling coefficient of the coupled line. The *z*-parameters of the coupled lines shown in Fig. 1(a) can be expressed in terms of  $z_c$  and  $C_{\text{eff}}$  as

$$[z] = \begin{bmatrix} -j \frac{z_c}{\sqrt{1 - C_{\text{eff}}^2}} \cot \frac{\pi f}{2f_0} & -j \frac{z_c C_{\text{eff}}}{\sqrt{1 - C_{\text{eff}}^2}} \csc \frac{\pi f}{2f_0} \\ -j \frac{z_c C_{\text{eff}}}{\sqrt{1 - C_{\text{eff}}^2}} \csc \frac{\pi f}{2f_0} & -j \frac{z_c}{\sqrt{1 - C_{\text{eff}}^2}} \cot \frac{\pi f}{2f_0} \end{bmatrix}$$

(4)

where f and  $f_0$  are the operating and the design center frequency, respectively. Based on *z*-parameters, the input impedance of coupled lines with termination load  $z_L$  can be calculated as

$$z_{\rm in} = z_{11} - \frac{z_{12} z_{21}}{z_{22} + z_L}.$$

(5)

## A. Wideband Flat Group Delay Circuit Type-I

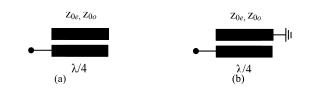

Fig. 1(b) shows the proposed structure of the wideband GD circuit type-I. Since the structure is symmetrical, the evenand odd-mode analyses can be applied to find S-parameters. From the equivalent circuit of the even-mode excitation shown in Fig. 2(a), the even-mode input impedance can be expressed as (6) using (4) and (5), with  $z_L = \infty$

$$z_{\text{ine}}^{\text{Type-I}} = -j \frac{z_c}{\sqrt{1 - C_{\text{eff}}^2}} \cot \frac{\pi f}{2f_0}.$$

(6)

Fig. 2. Equivalent circuits of the proposed GD circuit type-I under (a) evenand (b) odd-mode excitations.

Similarly, Fig. 2(b) shows the equivalent odd-mode excitation circuit. The odd-mode input impedance of the subcircuit shown in Fig. 2(b) can be determined as (7) by using (4) and (5), with  $z_L = 0$

$$z_{\rm ino}^{\rm Type-I} = -j \frac{z_c}{\sqrt{1 - C_{\rm eff}^2}} \left( \cot \frac{\pi f}{2f_0} - 2C_{\rm eff}^2 \csc \frac{\pi f}{f_0} \right).$$

(7)

The S-parameters of the wideband GD circuit type-I shown in Fig. 1(b) can be found as (8) using (6) and (7)

$$S_{11\_Type-I} = S_{22\_Type-I}$$

$$= \frac{z_{ine}^{Type-I} z_{ino}^{Type-I} - 1}{\left(z_{ine}^{Type-I} + 1\right) \left(z_{ino}^{Type-I} + 1\right)}$$

$$= \frac{x_3}{(1 - jx_1) (1 - jx_2)}$$

$$S_{21\_Type-I} = S_{12\_Type-I}$$

(8)

$$= \frac{z_{\text{ine}}^{\text{Type-I}} - z_{\text{ino}}^{\text{Type-I}}}{\left(z_{\text{ine}}^{\text{Type-I}} + 1\right) \left(z_{\text{ino}}^{\text{Type-I}} + 1\right)} = \frac{j2x_4}{(1 - jx_1)(1 - jx_2)}$$

(9)

where

$$x_{1} = \frac{z_{c}}{\sqrt{1 - C_{\text{eff}}^{2}}} \left( \cot \frac{\pi f}{2f_{0}} \sin \frac{\pi f}{f_{0}} - 2C_{\text{eff}}^{2} \right)$$

(10)

$$x_2 = \frac{z_c}{\sqrt{1 - C_{\text{eff}}^2}} \cot \frac{\pi f}{2f_0}$$

(11)

$$x_{3} = \frac{z_{c}^{2}}{1 - C_{\text{eff}}^{2}} \left( \cot^{2} \frac{\pi f}{2f_{0}} \sin \frac{\pi f}{f_{0}} - C_{\text{eff}}^{2} \cot \frac{\pi f}{2f_{0}} \right) - \sin \frac{\pi f}{f_{0}}$$

(12)

$$x_4 = \frac{2z_c}{\sqrt{1 - C_{\text{eff}}^2}} \left( \cot \frac{\pi f}{2f_0} \sin \frac{\pi f}{f_0} - C_{\text{eff}}^2 \right).$$

(13)

Similarly, the GD of the circuit type-I can be calculated as

$$\tau_{\text{Type-I}} = -\frac{1}{2\pi} \frac{d \angle S_{21\_\text{Type-I}}}{df} = \frac{z_c \sqrt{1 - C_{\text{eff}}^2}}{4f_0} \left(\frac{x_5}{x_6} + \frac{1}{x_7}\right)$$

(14)

where

$$x_{5} = \csc^{2} \frac{\pi f}{2f_{0}} \sin^{2} \frac{\pi f}{f_{0}} - 4C_{\text{eff}}^{2} \cos \frac{\pi f}{f_{0}}$$

(15)

$$x_{6} = \left(1 - C_{\text{eff}}^{2}\right) \sin^{2} \frac{\pi f}{f_{0}} + z_{c}^{2} \left(\cot \frac{\pi f}{2f_{0}} \sin \frac{\pi f}{f_{0}} - 2C_{\text{eff}}^{2}\right)^{2}$$

(16)

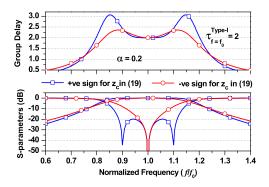

Fig. 3. Calculated results of the wideband flat GD circuit type-I.

$$x_7 = \sin^2 \frac{\pi f}{2f_0} \left( 1 - C_{\text{eff}}^2 \right) + z_c^2 \cos^2 \frac{\pi f}{2f_0}.$$

(17)

As seen from (14)–(17), the GD depends on  $z_c$  and  $C_{\text{eff}}$  of the coupled lines. Further, the GD at  $f_0$  can be simplified as

$$\tau_{f=f_0}^{\text{Type-I}} = \frac{1 - C_{\text{eff}}^2 + z_c^2 C_{\text{eff}}^2}{4 f_0 z_c C_{\text{eff}}^2 \sqrt{1 - C_{\text{eff}}^2}}.$$

(18)

An arbitrarily specified flat GD response can be obtained by selecting appropriate  $z_c$  and  $C_{\text{eff}}$ . For this purpose, we need to solve the value of  $z_c$  using (18). Therefore, the solution of  $z_c$  in terms of specified GD and  $C_{\text{eff}}$  can be found as

$$z_{c} = \sqrt{1 - C_{\text{eff}}^{2}} \left( 2f_{0}\tau_{f=f_{0}}^{\text{Type-I}} \pm \sqrt{\left(2f_{0}\tau_{f=f_{0}}^{\text{Type-I}}\right)^{2} - 1/C_{\text{eff}}^{2}} \right).$$

(19)

As noted from (19),  $z_c$  has two unique solutions, and the values are real and positive if

$$C_{\text{eff}}(\text{dB}) = \alpha - 20 \log \left(2 f_0 \tau_{f=f_0}^{\text{Type-I}}\right)$$

(20)

where  $\alpha$  is a positive factor which provides a degree of freedom to control  $C_{\text{eff}}$  and GD ripples. In this paper, in-band GD ripple ( $\Delta \tau_{\text{ripple}}$ ) is defined as

$$\Delta \tau_{\text{ripple}} = \frac{\tau_{\text{max}} - \tau_{f=f_0}}{\tau_{f=f_0}} \times 100\%.$$

(21)

Here,  $\tau_{\text{max}}$  is the maximum GD at passband-edge frequency. The required value of  $C_{\text{eff}}$  can be obtained using (20) for the specified GD with acceptable  $\Delta \tau_{\text{ripple}}$ .

Based on the above analytical analysis, Fig. 3 shows the calculated magnitudes/GD responses for circuit type-I. Table I gives the calculated circuit parameters. As shown in Fig. 3,  $z_c$  with a positive sign in (19) provides the wideband return loss characteristics with three poles; however, the GD at band edge has a high peak. Similarly, it is observed that GD is flat over the wideband when negative sign assigned in (19) for the solution of  $z_c$ . However, return loss is slightly narrow due to only one pole.

Similarly, Fig. 4 shows the calculated magnitude/GD responses with a variation of  $\alpha$ . In the case of positive sign in (19),  $\Delta \tau_{\text{ripple}}$  at in-band and band-edge frequencies are increased as  $\alpha$  increased; however, impedance matching decreases. On the contrary, when  $\alpha$  increased,  $\Delta \tau_{\text{ripple}}$  is decreased and GD approaches toward flat in the case of the negative sign in (19).

TABLE I Calculated Circuit Parameters of Circuit Type-I With Positive and Negative Signs in (19)

| Group delay specification : $\tau_{f=f_0}^{\text{Type-I}} = 2$ and $\Delta \tau_{\text{ripple}} = \frac{\tau_{\text{max}} - \tau_{f=f_0}}{\tau_{f=f_0}} \times 100\%$ |             |              |                          |          |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--------------------------|----------|--|--|--|--|

| Parameters                                                                                                                                                            | Case 1: +ve | sign in (12) | Case 2: -ve sign in (12) |          |  |  |  |  |

| $\Delta \tau_{ripple}$ (%)                                                                                                                                            | 53.18       | 67.89        | 17.94                    | 1.88     |  |  |  |  |

| ⊿ <sub>Type-I</sub> (%)                                                                                                                                               | 40.25       | 43.5         | 34                       | 21       |  |  |  |  |

| α                                                                                                                                                                     | 0.2         | 0.85         | 0.2                      | 0.80     |  |  |  |  |

| $C_{eff}(dB)$                                                                                                                                                         | -11.8412    | -11.1912     | -11.8412                 | -11.2412 |  |  |  |  |

| $z_c (\Omega)$                                                                                                                                                        | 4.6873      | 5.4661       | 3.0465                   | 2.2690   |  |  |  |  |

| $z_{0e}$ ( $\Omega$ )                                                                                                                                                 | 6.0890      | 7.2542       | 3.9576                   | 3.0061   |  |  |  |  |

| $z_{0o} (\Omega)$                                                                                                                                                     | 3.6082      | 4.1187       | 2.3452                   | 1.7126   |  |  |  |  |

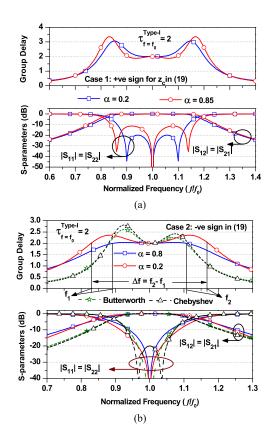

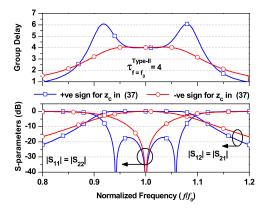

Fig. 4. Calculated GD/magnitude response of the proposed circuit type-I with different  $\alpha$  and according to (a) positive sign (case 1) and (b) negative sign (case 2) in (19) for the solution of  $z_c$ . Here,  $f_1$  and  $f_2$  are lower and upper cutoff frequencies when passband-edge GD approximately equals to GD at  $f_0$ .

Meanwhile, the return loss bandwidth decreases, therefore, a tradeoff occurs between wideband flat GD and return loss. Also, it is concluded from this analysis that for wideband flat GD response and minimum  $\Delta \tau_{ripple}$ , the negative sign in (19) is preferable.

Fig. 4(b) also shows the comparison results of the proposed circuit with conventional Butterworth and Chebyshev filters for the same GD at  $f_0$  and return loss bandwidth specification. As shown in Fig. 4(b), the proposed circuit can provide the flat GD response as compared to conventional filters.

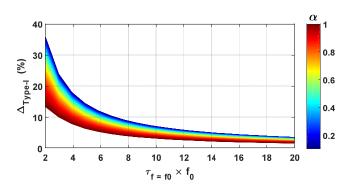

To investigate the effect of selecting  $\alpha$ , Fig. 5(a) shows the calculated  $\Delta \tau_{\text{ripple}}$  from (14) and (21) using MATLAB when

Fig. 5. (a) Calculated in-band GD ripples from (14) and (21) using MATLAB for different  $\alpha$ . (b) Circuit parameters of wideband flat GD of circuit type-I with a negative sign in (19) and  $\alpha = 0.8$ .

negative sign is selected in (19). As observed from Fig. 5(a), the  $\Delta \tau_{\text{ripple}}$  is decreased as  $\alpha$  increased. In general, higher  $\alpha$  is preferable for minimum  $\Delta \tau_{\text{ripple}}$ .

Fig. 5(b) shows design graphs to calculated circuits parameters for specified flat GD. As seen from this graph, the  $z_c$  increases and  $C_{\text{eff}}$  decreases as the GD increases. Therefore, the circuit type-I could have difficulty in practical realization in single-layer PCB technology for higher GD. This problem can be solved by circuit type-II which will be discussed in later section in detail.

Based on the above analysis, the negative sign in (19) is preferable for minimum  $\Delta \tau_{\text{ripple}}$ . Once  $z_c$  and  $C_{\text{eff}}$  are determined for the specified GD at  $f_0$  and minimum  $\Delta \tau_{\text{ripple}}$ , we should find the cutoff frequencies where the GD is approximately equal to GD at  $f_0$ , as shown in Fig. 4(b). Using (14), the GD fractional bandwidth of type-I circuit ( $\Delta_{\text{Type-I}}$ ) can be calculated as

$$\Delta_{\text{Type-I}} = \frac{f_2 - f_1}{f_0} = f(z_c, C_{\text{eff}})$$

(22)

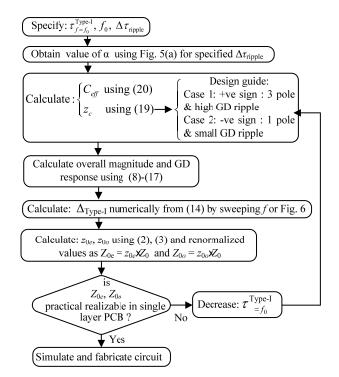

where  $f_1$  and  $f_2$  are lower and upper cutoff frequencies in between which the GD is equal to desired GD at  $f_0$ , as shown in Fig. 4. Since it is complicate to find  $f_1$  and  $f_2$  using (14), analytically, we used numerical method in MATLAB by sweeping frequency to find  $\Delta_{Type-I}$  for mathematical simplicity. Fig. 6 shows the calculated  $\Delta_{Type-I}$  for different  $\alpha$ . As GD is increased,  $\Delta_{Type-I}$  decreased. In addition,  $\Delta_{Type-I}$  is slightly higher when  $\alpha$  is small; however, the small  $\alpha$  increases  $\Delta \tau_{ripple}$ . The design steps to calculate circuit parameters of circuit type-I with specified GD can be described with the flowchart shown in Fig. 7.

Fig. 6. Calculated GDs fractional bandwidth ( $\Delta_{Type-I}$ ) of type-I circuit for different  $\alpha$ . Color bar represents different  $\alpha$  values.

Fig. 7. Design flowchart to calculate circuit parameters of wideband GD circuit type-I.

Fig. 8. Proposed structure of the wideband GD circuit-II.

# B. Wideband Flat Group Delay Circuit Type-II

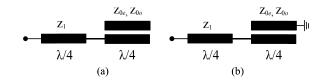

To overcome the limitation of wideband GD circuit type-I,  $\lambda/4$  TLs with a characteristic impedance of  $z_1$  are added at the input and output ports of GD circuit type-I, and Fig. 8 shows the proposed structure. Due to  $\lambda/4$  TLs, the proposed circuit type-II provides the extra degree of freedom, so that realizable circuit parameters can be obtained for high GD. Fig. 9 shows the equivalent circuits of the proposed circuit type-II under even- and odd-mode excitations. Therefore, the even- and odd-mode impedances of circuit type-II can be obtained from Fig. 9

Fig. 9. Equivalent circuits of the proposed GD circuit type-II under (a) evenand (b) odd-mode excitations.

and are expressed as (23) and (24), shown at the bottom of this page.

The S-parameter of circuit type-II can be found as (25) and (26) by using (23) and (24)

$$S_{11\_Type-II} = S_{22\_Type-II}$$

$$= \frac{z_{ine}^{Type-II} z_{ino}^{Type-II} - 1}{(z_{ine}^{Type-II} + 1)(z_{ino}^{Type-II} + 1)}$$

$$= \frac{x_9x_{11} - x_8x_{10}}{(x_8 - jx_9)(x_{10} + jx_{11})}$$

$$S_{21\_Type-II} = S_{12\_Type-II}$$

$$= \frac{z_{ine}^{Type-II} - z_{ino}^{Type-II}}{(z_{ine}^{Type-II} + 1)(z_{ino}^{Type-II} + 1)}$$

$$= \frac{j(x_9x_{10} + x_8x_{11})}{(x_8 - jx_9)(x_{10} + jx_{11})}$$

(25)

where

$$x_8 = \cot \frac{\pi f}{2f_0} \tag{27}$$

$$x_9 = \frac{z_1}{z_1 \sqrt{1 - C_{\text{eff}}^2} + z_c} \left( z_c \cot^2 \frac{\pi f}{2f_0} - z_1 \sqrt{1 - C_{\text{eff}}^2} \right)$$

(28)

$$x_{10} = 2\left(z_1\sqrt{1-C_{\text{eff}}^2} + z_c\right)\cos^2\frac{\pi f}{2f_0} - 2z_c C_{\text{eff}}^2$$

(29)

$$x_{11} = z_1^2 \sqrt{1 - C_{\text{eff}}^2 \sin \frac{\pi f}{f_0} - 2z_c z_1 \cos^2 \frac{\pi f}{2f_0} \cot \frac{\pi f}{2f_0}} + 2z_c z_1 C_{\text{eff}}^2 \cot \frac{\pi f}{2f_0}.$$

(30)

Finally, the GD of circuit type-II can be expressed as (31) by using (26)–(30)

$$\tau_{\text{Type-II}} = -\frac{1}{2\pi} \frac{d\angle S_{21\_\text{Type-II}}}{df} = -\frac{1}{2\pi} \frac{d\angle S_{12\_\text{Type-II}}}{df}$$

$$= \frac{1}{2\pi} \left( \frac{x'_8 x_9 - x_8 x'_9}{x_8^2 + x_9^2} + \frac{x_{10} x'_{11} - x'_{10} x_{11}}{x_{10}^2 + x_{11}^2} \right) \quad (31)$$

where

$$x'_{8} = -\frac{\pi}{2f_{0}}\csc^{2}\frac{\pi f}{2f_{0}}$$

(32)

$$x'_{9} = \frac{\pi}{f_{0}} \frac{z_{1}}{z_{1}\sqrt{1 - C_{\text{eff}}^{2}} + z_{c}} \left( -z_{c} \cot \frac{\pi f}{2f_{0}} \csc^{2} \frac{\pi f}{2f_{0}} \right) \quad (33)$$

$$x'_{10} = -\frac{\pi}{f_0} \left( z_1 \sqrt{1 - C_{\text{eff}}^2} + z_c \right) \sin \frac{\pi f}{f_0}$$

(34)

$$\mathbf{x}_{11}' = \left\{ \frac{\pi z_1^2 \sqrt{1 - C_{\text{eff}}^2}}{f_0} \cos \frac{\pi f}{f_0} - \frac{\pi z_c z_1 C_{\text{eff}}^2}{f_0} \csc^2 \frac{\pi f}{2f_0}}{+ \frac{\pi z_c z_1}{f_0} \cot^2 \frac{\pi f}{2f_0} + \frac{2\pi z_c z_1}{f_0} \cos^2 \frac{\pi f}{2f_0}}{\cos^2 \frac{\pi f}{2f_0}} \right\}.$$

(35)

Furthermore, the GD at  $f_0$  can be simplified in the following equation:

$$\tau_{f=f_0}^{\text{Type-II}} = \frac{1}{4f_0} \left( \frac{z_c^2 C_{\text{eff}}^2 + z_1 z_c \sqrt{1 - C_{\text{eff}}^2 C_{\text{eff}}^2}}{+z_1^3 \sqrt{1 - C_{\text{eff}}^2 C_{\text{eff}}^2 z_c} + z_1^4 \left(1 - C_{\text{eff}}^2\right)}{z_1^2 \sqrt{1 - C_{\text{eff}}^2 C_{\text{eff}}^2 z_c}} \right).$$

(36)

As seen from (31)–(36), the circuit type-II has more degree of freedom in circuit parameters (such as  $z_1$ ) than that of type-I; therefore, the limitation in the practical implementation of type-I for higher GD can be overcome with the proposed structure of type-II. The additional TLs mean that  $z_{0e}$  and  $z_{0o}$ can be reduced to a lower value for higher GD.

The required value of  $z_c$  with specified flat GD can be found by solving (36) in terms of  $C_{\text{eff}}$  and GD at  $f_0$  as

$$z_c = \frac{z_1}{2} \sqrt{1 - C_{\text{eff}}^2} \left( b \pm \sqrt{b^2 - 4z_1^2 / C_{\text{eff}}^2} \right)$$

(37)

where

$$b = 4f_0 \tau_{f=f_0}^{\text{Type-II}} z_1 - z_1^2 - 1.$$

(38)

From (37), the value of  $z_c$  is real and positive only if

$$C_{\rm eff}(\rm dB) = \beta + 20\log\left(\frac{2z_1}{b}\right) \tag{39}$$

where  $\beta$  is a positive factor that controls the  $\Delta \tau_{\text{ripple}}$ . Like the circuit type-I, the  $\beta$  must be positive value which will provide a degree of freedom to control  $\Delta \tau_{\text{ripple}}$ . The required value of  $C_{\text{eff}}$  can be calculated using (39) when a designer specifies GD at  $f_0$  and  $z_1$ . In addition,  $z_c$  has two unique solutions depending on positive and negative sign in (37).

$$z_{\text{ine}}^{\text{Type-II}} = \frac{jz_1}{z_1\sqrt{1 - C_{\text{eff}}^2} + z_c} \left( z_1\sqrt{1 - C_{\text{eff}}^2} \tan\frac{\pi f}{2f_0} - z_c \cot\frac{\pi f}{2f_0} \right)$$

(23)

$$z_{\rm ino}^{\rm Type-II} = j \frac{z_1^2 \sqrt{1 - C_{\rm eff}^2} \sin \frac{\pi f}{f_0} - 2z_c z_1 \cos^2 \frac{\pi f}{2f_0} \cot \frac{\pi f}{2f_0} + 2z_c z_1 C_{\rm eff}^2 \cot \frac{\pi f}{2f_0}}{\left(2z_1 \sqrt{1 - C_{\rm eff}^2} + 2z_c\right) \cos^2 \frac{\pi f}{2f_0} - 2z_c C_{\rm eff}^2}$$

(24)

Fig. 10. Synthesized magnitude/GD response of circuit type-II.

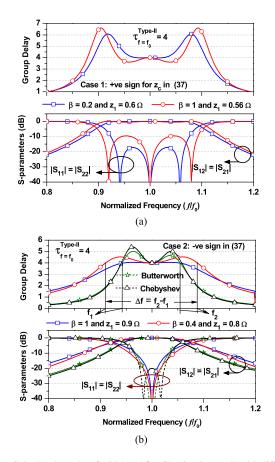

Fig. 10 shows the calculated magnitude/GD responses of circuit type-II. As like the circuit type-I, the solution of  $z_c$  with a positive sign in (37) provides wide return loss characteristics with three poles; however, peaks occur in GD characteristics at band-edge frequencies. These peaks in GD can be minimized by obtaining a solution of  $z_c$  with a negative sign in (37), as shown in Fig. 10. However, only one pole occurs at the center frequency when the GD is flat. In general, the negative sign in (37) is preferable for wideband flat GD with minimum ripple.

Fig. 11(a) shows the synthesized magnitude/GD response of type-II with different  $C_{\text{eff}}$  and positive sign in (37) for the solution of  $z_c$ . As shown in Fig. 11(a), ripples in GD at in-band and band-edge frequencies increase as  $\beta$  increases. However, the return loss bandwidth increases with the decrease of maximum achievable return loss magnitude.

Similarly, Fig. 11(b) shows the calculated magnitude/GD responses of type-II with different  $\beta$  and negative sign in (37) for the solution of  $z_c$ . The responses of the proposed circuit type-II are also compared with conventional Butterworth and Chebyshev filter response for the same GD at  $f_0$  and return loss bandwidth specification. The value of  $\Delta \tau_{ripple}$  is decreased and approached toward flat GD characteristics as  $\beta$  increases in the proposed circuit. However, the return loss bandwidth slightly decreases. Therefore, a tradeoff occurs between wideband flat GD and return loss bandwidth.

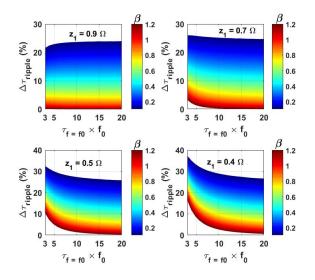

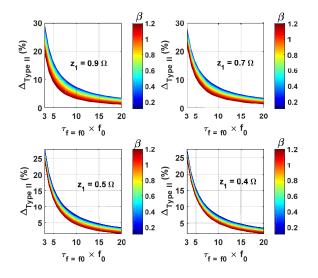

To investigate the effect of selecting  $\beta$ , Fig. 12 shows numerically calculated  $\Delta \tau_{\text{ripple}}$  of circuit type-II with different  $z_1$  and  $\beta$  using (21) and (31) in MATLAB. As shown in Fig. 12,  $\Delta \tau_{\text{ripple}}$  can be minimized by increasing the value of  $\beta$ . In general, higher  $\beta$  is preferable for minimum  $\Delta \tau_{\text{ripple}}$ .

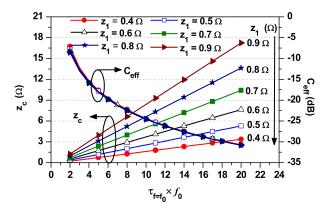

Fig. 13 shows the design graph to calculate the circuit parameters of circuit type-II with specified GD. From this graph, the value of  $z_c$  increases and  $C_{\text{eff}}$  decreases as GD increases. It is also clear from this graph that practical realizable circuit parameters of coupled lines can be obtained by appropriately selecting  $z_1$ . Specifically, the low  $z_1$  is preferable for high GD and practical realizable  $z_c$  and  $C_{\text{eff}}$ .

Like the type-I circuit, once the circuit parameters such as  $z_1$ ,  $z_c$ , and  $C_{\text{eff}}$  are determined based on specifications (GD,  $f_0$ , and  $\Delta \tau_{\text{ripple}}$ ), we sweep frequency in (31) under condition  $\tau_{\text{Type-II}} = \tau_{f=f_0}^{\text{Type-II}}$ , as shown in Fig. 11, for finding

Fig. 11. Calculated results of wideband flat GD circuit type-II with different  $\beta$  and according to (a) positive sign (case 1) and (b) negative sign (case 2) in (37) for the solution of  $z_c$ . Here,  $f_1$  and  $f_2$  are lower and upper cutoff frequencies when passband-edge GD approximately equals to GD at  $f_0$ .

Fig. 12. Calculated in-band group ripples of type-II circuit from (21) and (31) using MATLAB for different  $z_1$  and  $\beta$  with a negative sign in (37). Color bar represents different  $\beta$  values.

lower and upper cutoff frequencies. Finally, the GD fractional bandwidth ( $\Delta_{Type-II}$ ) can be found as

$$\Delta_{\text{Type-II}} = \frac{f_2 - f_1}{f_0} = f(z_1, z_c, C_{\text{eff}})$$

(40)

Fig. 13. Calculated  $z_c$  and  $C_{\text{eff}}$  for flat wideband GD characteristics of circuit type-II with  $\beta = 0.9$  and negative sign in (37).

Fig. 14. Calculated GD fractional bandwidth ( $\Delta_{Type-II}$ ) of type-II circuit for different  $\beta$  and  $z_1$ . Color bar represents different  $\beta$  values.

where  $f_1$  and  $f_2$  are lower and upper cutoff frequencies in between which the GD is within the desired GD at  $f_0$ .

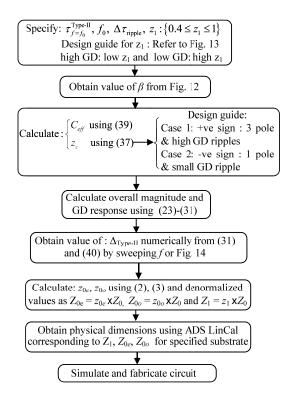

Fig. 14 shows the calculated  $\Delta_{\text{Type-II}}$  for different values of  $z_1$  and  $\beta$ . From these graphs,  $\Delta$  is decreased as GD increases. And  $\Delta$  is slightly higher with small  $\beta$ . As like the type-I, Fig. 15 summarizes the design steps to calculate circuit parameters of circuit type-II with specified GD and the minimum  $\Delta \tau_{\text{ripple}}$ .

#### **III.** IMPLEMENTATION AND RESULTS

For experimental demonstration, prototypes of GD circuit type-I and type-II were designed and fabricated on RT/Duroid 5880 substrate with a dielectric constant ( $\varepsilon_r$ ) of 2.20 and a thickness (*h*) of 0.787 mm. In this paper, we designed prototype circuits for flat (minimum ripples) GD. The simulation was performed using ANSYS HFSS 15.

# A. Results of Wideband Flat Group Delay Circuit Type-I

For experimental validation, we set the design goal of circuit type-I as  $\tau_{f=f_0}^{\text{Type-I}} = 1$  ns at  $f_0 = 2$  GHz with acceptable  $\Delta \tau_{\text{ripple}}$  of less than 1.3%. Using design flowchart shown in Fig. 7,

Fig. 15. Design flowchart to calculate circuit parameters of wideband GD circuit type-II.

Fig. 16. (a) Layout of the wideband flat GD circuit-I with physical dimensions. (b) Photograph of the fabricated circuit. Physical dimensions:  $L_{11} = 28.6$ ,  $L_{12} = 3.9$ ,  $L_{12} = 2.5$ ,  $W_{11} = 0.43$ , and  $g_{11} = 0.48$  (unit: mm).

the calculated circuit parameters for given specification are determined as  $\alpha = 0.85$ ,  $z_c = 2.2239 \Omega$ ,  $C_{\text{eff}} = -11.1912 \text{ dB}$ ,  $z_{0e} = 2.9514 \Omega$ , and  $z_{0o} = 1.6757 \Omega$ . Using these circuit parameters, the calculated  $\Delta_{\text{Type-I}}$  of the designed circuit is given as 19.1%. The renormalized circuit parameters of coupled lines with respect to 50- $\Omega$  port impedances are  $Z_{0e} =$ 147.5699  $\Omega$  and  $Z_{0o} = 83.7849 \Omega$ . Fig. 16(a) shows the layout and physical dimensions while Fig. 16(b) shows a photograph of fabricated circuit. In this layout, small length  $L_{12}$  is added for connecting port. For minimizing the effect of  $L_{12}$ , the same length is also added in another side of coupled lines [30].

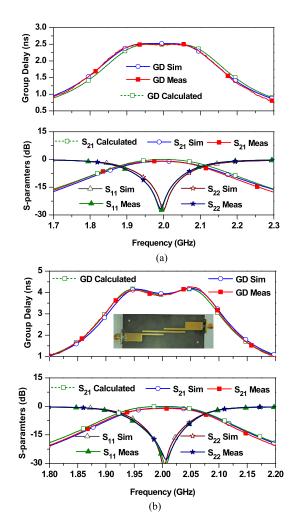

Fig. 17 shows the simulated and measured GDs and S-parameter magnitudes. The measurement results agree well with simulation and theoretical predicated results. From the measurement, the GD and magnitude of transmission coefficient at  $f_0 = 2$  GHz are determined as  $\tau_{f=f_0}^{\text{Type-I}} = 0.998$  ns and  $|S_{21}| = -0.42$  dB, respectively. In addition, the GD is flat in frequency extending from 1.78 to 2.15 GHz, with flat GD fractional bandwidth of 18.5%. Similarly, the input and output return losses at  $f_0$  are measured as  $|S_{11}| = -26.87$  dB and  $|S_{22}| = -32.32$  dB, respectively.

Fig. 17. Simulation and measured results of GD circuit type-I.

Fig. 18. (a) Layout of the wideband flat GD circuit type-II with physical dimensions. (b) Photograph of the fabricated circuit.

### B. Results of Wideband Flat Group Delay Circuit Type-II

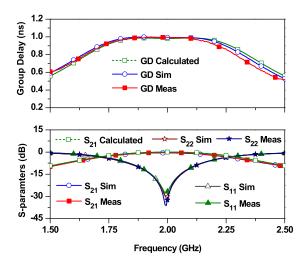

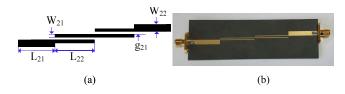

For experimental validation of circuit type-II, the prototype circuit was designed and fabricated at  $f_0 = 2$  GHz with  $\tau_{f=f_0}^{\text{Type-II}} = 2.5$  ns and  $\Delta \tau_{\text{ripple}} \leq 2\%$ . Assuming  $z_1 = 0.72 \Omega$ , the calculated circuit parameters for the given specification are obtained as  $\beta = 1.1$ ,  $z_c = 2.4240 \Omega$ , and  $C_{\text{eff}} = -17.9321 \text{ dB}$  using the proposed design method described previously. The calculated  $\Delta_{\text{Type-II}}$  of the design circuit is given as 10.1% using above circuit parameters of designed prototype are  $Z_1 = 36 \Omega$ ,  $Z_{0e} = 137.6923 \Omega$ , and  $Z_{0o} = 106.6857 \Omega$ . Fig. 18 shows the layout and photograph of the fabricated circuit type-II. The physical dimensions of fabricated circuit are given as  $L_{21} = 24.90$ ,  $L_{22} = 28.2$ ,  $W_{21} = 0.38$ ,  $W_{22} = 3.80$ , and  $g_{21} = 1.17$  (unit: mm).

Fig. 19(a) shows the measured and simulated S-parameters and GDs. These results show that the measurement results are in good agreement with the simulation and theoretical predicated values. From experiment, the GD is 2.498 ns at  $f_0$  and flat GD extends from 1.90 to 2.10 GHz. Therefore, the flat GD fractional bandwidth of the fabricated circuit type-II is 10%, which is slightly narrower than that of circuit type-I because of higher GD than circuit type-I. Similarly, the measured S-parameters at  $f_0 = 2$  GHz are determined as  $|S_{21}| = -0.89$  dB,  $|S_{11}| = -28.18$  dB, and  $|S_{22}| = -26.28$  dB.

To demonstrate the prototype for higher GD, an extra circuit was designed for GD of 4 ns at  $f_0 = 2$  GHz with  $\Delta \tau_{\text{ripple}} \leq 8\%$ . Assuming  $z_1 = 0.4 \Omega$ , the calculated parameters are given as  $\beta = 0.9$ ,  $z_{0e} = 1.4215 \Omega$ , and  $z_{0o} = 1.2201 \Omega$ . Once circuit parameters are obtained,

Fig. 19. Simulation and measured results of type-II circuit with GD of (a) 2.5 and (b) 4 ns.

TABLE II CALCULATED CIRCUIT PARAMETERS OF CIRCUIT TYPE-I WITH POSITIVE AND NEGATIVE SIGNS IN (37)

| Group delay specification : $\tau_{f=f_0}^{\text{Type-II}} = 4$ and $\Delta \tau_{\text{rippple}} = \frac{\tau_{\text{max}} - \tau_{f=f_0}}{\tau_{f=f_0}} \times 100\%$ |             |                |                          |          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------------------------|----------|--|--|--|--|

| Parameters                                                                                                                                                              | Case 1: +ve | e sign in (22) | Case 2: -ve sign in (22) |          |  |  |  |  |

| $\Delta \tau_{ripple}$ (%)                                                                                                                                              | 52.07       | 65.81          | 1.22                     | 13.12    |  |  |  |  |

| $\Delta_{\text{Type-II}}$ (%)                                                                                                                                           | 21.81       | 23.98          | 10.59                    | 17.73    |  |  |  |  |

| β                                                                                                                                                                       | 0.2         | 1              | 1                        | 0.4      |  |  |  |  |

| $C_{eff}(dB)$                                                                                                                                                           | -16.5349    | -15.6848       | -15.8951                 | -16.4709 |  |  |  |  |

| $z_c (\Omega)$                                                                                                                                                          | 2.9630      | 3.0696         | 3.0560                   | 3.1043   |  |  |  |  |

| $z_{0e}$ ( $\Omega$ )                                                                                                                                                   | 3.4430      | 3.6234         | 3.5928                   | 3.6112   |  |  |  |  |

| $z_{0o} (\Omega)$                                                                                                                                                       | 2.5499      | 2.6005         | 2.5995                   | 2.6685   |  |  |  |  |

| $z_1 (\Omega)$                                                                                                                                                          | 0.60        | 0.56           | 0.90                     | 0.80     |  |  |  |  |

$\Delta_{\text{Type-II}}$  of circuit is estimated as 7.3% using (31) and (40). Fig. 19(b) shows the measured and simulation results of prototype. The measured GD is 3.96 ns which extends from 1.93 to 2.074 GHz with  $\Delta = 7.20\%$ . Similarly, the measured  $|S_{21}|$ ,  $|S_{11}|$ , and  $|S_{22}|$  at  $f_0$  are determined as -1.10, -27.2, and -24.94 dB, respectively.

Table III shows performance comparison of the proposed work with state of the arts. As seen from Table III, the proposed work provides wide flat GD. In addition, the proposed

TABLE III Performance Comparison

|           | <i>f</i> <sub>0</sub> (GHz) | S <sub>21max</sub> (dB) | $\tau_{max}\left(ns\right)$ | Δ (%)    | Method       | Cross-Coupling/<br>No. of Resonators |

|-----------|-----------------------------|-------------------------|-----------------------------|----------|--------------|--------------------------------------|

| [6]       | 1.0                         | <-30                    | 10.0                        | 2        | Analytical   | х                                    |

| [7]       | 2.14                        | <-5.9                   | 4.0                         | 2.803    | Analtytical  | х                                    |

| [11]      | 0.50                        | <-1.5                   | 2.30                        | 40*      | Analytical   | x                                    |

| [13]      | 2.10                        | <-6.5                   | 6.0                         | 9.52     | Iterative    | х                                    |

| [21]      | 1.93                        | <-2.5                   | 16**                        | 0.25     | Iterative    | Yes/6                                |

| [23]      | 0.947                       | <-1.5                   | 15**                        | 4.20     | Iterative    | Yes/6                                |

| [24]      | 5.0                         | <-1.5                   | 4.0***                      | 4.0      | CM/iterative | Yes/4                                |

| [25]      | 10                          | <-1.5                   | 7.0***                      | 0.8      | CM/iterative | Yes/4                                |

| This work | 2.0/2.0/                    | <-0.42/-0.89/           |                             | 18.5/10/ |              | No/2                                 |

|           | 2.0                         | <-1.10                  | 4.0                         | 7.20     | /Iterative   |                                      |

$\Delta$ = Fractional bandwidth of flat group delay, \* = Ideal simulated result

\*\* = Waveguide linear phase filter, \*\*\* = SIW filters,

CM = Coupling matrix synthesis, [6]-[21]: All-pass group delay circuits,

[23]-[25]: linear phase filters

structure is very simple and does not require cross-coupling or controlling sign of cross-coupling.

## IV. CONCLUSION

In this paper, we present transmission-type wideband flat GD circuits using coupled lines. The analytical design equations are obtained using symmetrical even- and odd-mode analyses. The circuit parameters for arbitrarily specified flat GD are obtained analytically and do not require any optimization procedures. In addition, the proposed circuits are very simple to design and provide a wideband flat GD without any cross-coupling or controlling sign of cross-coupling. For experimental validation of the proposed structures, the prototypes of wideband GD circuits are fabricated at the center frequency of 2 GHz. The experimental results indicate that the proposed structures provide a wideband flat GD response and are applicable to various RF/microwaves circuits such as wideband analog RF self-interference cancellation, RF amplifier linearization, and real-time analog radio-signal processing.

#### REFERENCES

- C. Caloz, S. Gupta, Q. Zhang, and B. Nikfal, "Analog signal processing: A possible alternative or complement to dominantly digital radio schemes," *IEEE Microw. Mag.*, vol. 14, no. 6, pp. 87–103, Sep./Oct. 2013.

- [2] S. Gupta, S. Abielmona, and C. Caloz, "Microwave analog real-time spectrum analyzer (RTSA) based on the spectral–spatial decomposition property of leaky-wave structures," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 12, pp. 2989–2999, Dec. 2009.

- [3] S. Abielmona, S. Gupta, and C. Caloz, "Compressive receiver using a CRLH-based dispersive delay line for analog signal processing," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 11, pp. 2617–2626, Nov. 2009.

- [4] K. E. Kolodziej, B. T. Perry, and J. G. McMichael, "Multitap RF canceller for in-band full-duplex wireless communications," *IEEE Trans. Wireless Commun.*, vol. 15, no. 6, pp. 4321–4334, Jun. 2016.

- [5] Y.-C. Jeong, D. Ahn, C.-D. Kim, and I.-S. Chang, "A feed-forward amplifier using an equal group-delay signal cancellation technique," *Microw. J.*, vol. 50, no. 4, pp. 126–134, Apr. 2007.

- [6] S. Lucyszyn and I. D. Robertson, "Analog reflection topology building blocks for adaptive microwave signal processing applications," *IEEE Trans. Microw. Theory Techn.*, vol. 43, no. 3, pp. 601–611, Mar. 1995.

- [7] G. Chaudhary, H. Choi, Y. Joeng, J. Lim, and C. D. Kim, "Design of group delay time controller based on a reflective parallel resonator," *ETRI J.*, vol. 34, no. 2, pp. 210–215, Apr. 2012.

- [8] M. H. Chen, "The design of a multiple cavity equalizer," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-30, no. 9, pp. 1380–1383, Sep. 1982.

- [9] H.-T. Hsu, H.-W. Yao, K. A. Zaki, and A. E. Atia, "Synthesis of coupledresonators group-delay equalizers," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 8, pp. 1960–1968, Aug. 2002.

- [10] Q. Zhang, S. Gupta, and C. Caloz, "Synthesis of narrowband reflectiontype phasers with arbitrary prescribed group delay," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 8, pp. 2394–2402, Aug. 2012.

- [11] T. Guo, Q. Zhang, Y. Chen, R. Wang, and C. Caloz, "Shunt-stub and stepped-impedance broadband reflective phasers," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 10, pp. 807–809, Oct. 2016.

- [12] W. Liao, Q. Zhang, Y. Chen, S. Wong, and C. Caloz, "Compact reflection-type phaser using quarter-wavelength transmission line resonators," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 6, pp. 391–393, Jun. 2015.

- [13] T. Guo, Q. Zhang, Y. Chen, R. Wang, and C. Caloz, "Single-step tunable group delay phaser for spectrum sniffing," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 12, pp. 808–810, Dec. 2015.

- [14] R. Withers, A. Anderson, P. Wright, and S. Reible, "Superconductive tapped delay lines for microwave analog signal processing," *IEEE Trans. Magn.*, vol. MAG-19, no. 3, pp. 480–484, May 1983.

- [15] W. J. D. Steenaart, "The synthesis of coupled transmission line all-pass networks in cascades of 1 to n," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-11, no. 1, pp. 23–29, Jan. 1963.

- [16] K. Keerthan and K. J. Vinoy, "Design of cascaded all pass network with monotonous group delay response for broadband radio frequency applications," *IET Microw., Antenna Propag.*, vol. 10, no. 7, pp. 808–815, May 2016.

- [17] S. Gupta, A. Parsa, E. Perret, R. V. Snyder, R. J. Wenzel, and C. Caloz, "Group-delay engineered noncommensurate transmission line all-pass network for analog signal processing," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 9, pp. 2392–2407, Sep. 2010.

- [18] Q. Zhang, S. Gupta, and C. Caloz, "Synthesis of broadband dispersive delay structures formed by commensurate C- and D-sections," *Int. J. RF Microw. Comput.-Added Eng.*, vol. 24, no. 3, pp. 322–331, May 2014.

- [19] S. Taravati, S. Gupta, Q. Zhang, and C. Caloz, "Enhanced bandwidth and diversity in real-time analog signal processing (R-ASP) using nonuniform C-section phasers," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 9, pp. 663–665, Sep. 2016.

- [20] Y. Horii, S. Gupta, B. Nikfal, and C. Caloz, "Multilayer broadsidecoupled dispersive delay structures for analog signal processing," *IEEE Microw. Wireless Compon. Lett.*, vol. 22, no. 1, pp. 1–3, Jan. 2012.

- [21] B. Xiang, X. Wang, and A. B. Apsel, "A reconfigurable integrated dispersive delay line (RI-DDL) in 0.13-μm CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 7, pp. 2610–2619, Jul. 2013.

- [22] J. D. Rhodes, "The design and synthesis of a class of microwave bandpass linear phase filters," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-17, no. 4, pp. 189–204, Apr. 1969.

- [23] H. C. H. Cheung, F. Huang, M. J. Lancaster, R. G. Humphreys, and N. G. Chew, "Improvements in superconducting linear phase microwave delay line bandpass filters," *IEEE Trans. Appl. Supercond.*, vol. 5, no. 2, pp. 2675–2677, Jun. 1995.

- [24] J.-S. Hong and M. J. Lancaster, *Microstrip Filters for RF/Microwave Applications*. New York, NY, USA: Wiley, 2001, pp. 350–360.

- [25] L. Szydlowski, N. Leszczynska, and M. Mrozowski, "A linear phase filter in quadruplet topology with frequency-dependent couplings," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 1, pp. 32–34, Jan. 2014.

- [26] X. Chen, W. Hong, T. Cui, J. Chen, and K. Wu, "Substrate integrated waveguide (SIW) linear phase filter," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 11, pp. 787–789, Nov. 2005.

- [27] G. Pfitzenmaier, "Synthesis and realization of narrow-band canonical microwave bandpass filters exhibiting linear phase and transmission zeros," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-30, no. 9, pp. 1300–1311, Sep. 1982.

- [28] H.-R. Ahn, Asymmetric Passive Components in Microwave Integrated Circuits. New York, NY, USA: Wiley, 2006.

- [29] G. Chaudhary and Y. Jeong, "Transmission-type negative group delay networks using coupled line doublet structure," *IET Microw., Antennas Propag.*, vol. 9, no. 8, pp. 748–754, Jun. 2015.

- [30] H.-R. Ahn and M. M. Tentzeris, "Novel generic asymmetric and symmetric equivalent circuits of 90° coupled transmission-line sections applicable to marchand baluns," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 3, pp. 746–759, Mar. 2017.

**Girdhari Chaudhary** (S'10–M'13) received the B.E. degree in electronics and communication engineering from Nepal Engineering College, Kathmandu, Nepal, in 2004, the M.Tech. degree from MNIT, Jaipur, India, in 2007, and the Ph.D. degree in electronics engineering from Chonbuk National University, Jeonju, South Korea, in 2013.

He is currently an Assistant Research Professor with the Division of Electronics Engineering, Chonbuk National University. His current research interests include multiband tunable passive circuits, systems and high-efficiency power amplifiers, and negative

in-band full-duplex systems and high-efficiency power amplifiers, and negative group delay circuits and its applications.

Dr. Chaudhary was a recipient of the BK21 PLUS Research Excellence Award 2015 from the Ministry of Education, South Korea. He worked as a Principal Investigator of the independent Project through the Basic Science Research Program of the National Research Foundation (NRF), funded by the Ministry of Education Korea. He received the Korean Research Fellowship through the NRF of Korea, funded by the Ministry of Science and ICT. He has served as a Reviewer for the IEEE TRANSACTION ON MICROWAVE THEORY AND TECHNIQUES, IEEE MICROWAVE AND WIRELESS COMPONENT LET-TERS, the IEEE TRANSACTION ON CIRCUIT AND SYSTEMS—I: REGULAR PAPERS, and the IEEE TRANSACTION ON INDUSTRIAL ELECTRONICS.

**Yongchae Jeong** (M'99–SM'10) received the B.S.E.E., M.S.E.E., and Ph.D. degrees in electronics engineering from Sogang University, Seoul, South Korea, in 1989, 1991, and 1996, respectively.

From 1991 to 1998, he was a Senior Engineer with Samsung Electronics. In 1998, he joined the Division of Electronics Engineering, Chonbuk National University, Jeonju, South Korea, where he is currently a Professor, director of IT Convergence Research Center and the HOPE-IT Human Resource Development Center of BK21 PLUS. From 2006 to 2007,

he was a Visiting Professor with the Georgia Institute of Technology, Atlanta, GA, USA. He is currently teaching and conducting research in the area of microwave passive and active circuits, mobile and satellite base-station RF system, design of periodic defected transmission line, negative group delay circuits and its applications, in-band full-duplex radio, and RFIC design. He has authored or co-authored over 210 papers in international journals and conference proceedings.

Prof. Jeong is a member of the Korea Institute of Electromagnetic Engineering and Science.