# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl. *H03F 1/32* (2006.01)

(45) 공고일자 2007년07월02일 (11) 등록번호 10-0733761

(24) 등록일자 2007년06월25일

(21) 출원번호

10-2004-0103080

(65) 공개번호

10-2006-0064284

(22) 출원일자심사청구일자

2004년12월08일 2004년12월08일 (43) 공개일자

2006년06월13일

(73) 특허권자

세원텔레텍 주식회사

경기 안양시 동안구 관양2동 881번지

(72) 발명자

정용채

전라북도 전주시 덕진구 덕진1가 664-14 전북대학교

김철동

경기도 과천시 중앙동 67 주공아파트 1007-402

김홍기

경기도 군포시 산본동 1092 장미아파트 1139-903호

장익수

서울특별시 강남구 역삼동 614-20

아달

충남 천안시 쌍용2동 용암동아벽산아파트 107동 303호

(74) 대리인

김석현

(56) 선행기술조사문헌

동일 군속도 지연 신호 상쇄기를 이용한 광대역 feedforward KR100266817 B1 증폭기 설계(논문, 2005.8)

심사관: 선동국

전체 청구항 수 : 총 6 항

## (54) 동일 군속도 지연 신호상쇄기 및 이를 적용한 광대역피드포워드 전력증폭기

## (57) 요약

본 발명은 피드포워드 전력증폭기에 관한 것으로서, 종전의 신호상쇄기가 동작 주파수 전 대역에서 위상과 군속도 지연 정합을 동시에 만족시킬 수 없었던 문제점을 해결하여 위상과 군속도 지연 정합을 동시에 만족시킴으로써, 인가되는 두 입력 단자의 신호들을 동일 군속도를 가지면서 광대역 신호 상쇄를 가능하게 하는 새로운 구조의 동일 군속도 지연 신호상쇄기 및 이를 적용한 광대역 피드포워드 전력증폭기를 제공한다.

#### 대표도

도 5

## 특허청구의 범위

## 청구항 1.

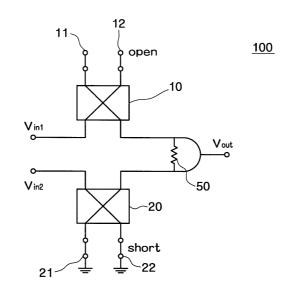

결합단(11)과 전송단(12)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호(Vin1)를 인가받아서 격리단을 통하여 출력하는 제1 3dB-하이브리드 회로(10)와;

결합단(21)과 전송단(22)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 3dB-하이브리드 회로(20)와;

상기 제1 3dB-하이브리드 회로(10) 및 상기 제2 3dB-하이브리드 회로(20)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기.

## 청구항 2.

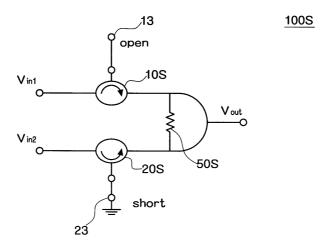

출력단(13)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호( $V_{in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 서큐 레이터(10S)와;

출력단(23)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 서큐레이터(20S)와;

상기 제1 서큐레이터(10S) 및 상기 제2 서큐레이터(20S)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기 (50S);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기.

#### 청구항 3.

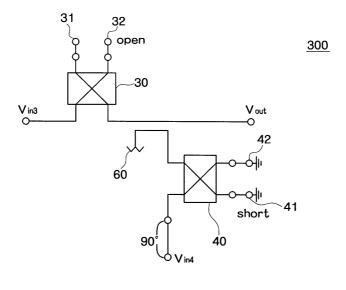

결합단(31)과 전송단(32)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 3dB-하이브리드 회로(30)와;

결합단(41)과 전송단(42)이 단락되며, 결합기의 결합계수와 삽입손실의 차만큼 상기 제3 입력신호( $V_{in3}$ )에 대해 진폭차와  $90^\circ$ 위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 3dB-하이브리드 회로(40)와;

상기 제3 3dB-하이브리드 회로(30) 및 상기 제4 3dB-하이브리드 회로(40)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기.

## 청구항 4.

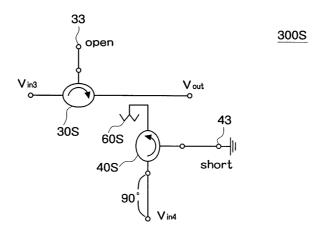

출력단(33)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 서큐 레이터(30S)와;

출력단(43)이 단락되며, 상기 제3 입력신호( $V_{in3}$ )와 결합기의 결합계수와 삽입손실의 차만큼 진폭차를 갖고  $90^\circ$ 위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 서큐레이터(40S)와;

상기 제3 서큐레이터(30S) 및 상기 제4 서큐레이터(40S)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60S);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기.

## 청구항 5.

주 신호상쇄기 회로를 구비하는 피드포워드 전력증폭기에 있어서,

결합단(11)과 전송단(12)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호( $V_{in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 3dB-하이브리드 회로(10), 결합단(21)과 전송단(22)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 3dB-하이브리드 회로(20), 상기 제1 3dB-하이브리드 회로(10) 및 상기 제2 3dB-하이브리드 회로(20)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50)로 구성되는 주 신호상쇄기 회로(100)와;

출력단(13)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호( $V_{\rm in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 서큐 레이터(10S), 출력단(23)이 단락되며, 상기 제1 입력신호( $V_{\rm in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{\rm in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 서큐레이터(20S), 상기 제1 서큐레이터(10S) 및 상기 제2 서큐레이터(20S)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50S)로 구성되는 주 신호상쇄기 회로(100S);

중 어느 하나를 주 신호감쇄기 회로로 구비함을 특징으로 하는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포워드 전력증폭기.

## 청구항 6.

혼변조 신호상쇄기 회로를 구비하는 피드포워드 전력증폭기에 있어서,

결합단(31)과 전송단(32)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 3dB-하이브리드 회로(30), 결합단(41)과 전송단(42이 단락되며, 결합기(60)의 결합계수와 삽입손실의 차만큼상기 제3 입력신호( $V_{in3}$ )에 대해 진폭차와  $90^\circ$ 위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 3dB-하이브리드 회로(40), 상기 제3 3dB-하이브리드 회로(30) 및 상기 제4 3dB-하이브리드 회로(40)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60)로 구성되는 혼변조 왜곡 신호상쇄기 회로(300);

출력단(33)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 서큐 레이터(30S), 출력단(43)이 단락되며, 결합기(60S)의 결합계수와 삽입손실의 차만큼 상기 제3 입력신호( $V_{in3}$ )에 대해 진 폭차와 90°위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 서큐레이터(40S), 상기 제3 서큐레이터(30S) 및 상기 제4 서큐레이터(40S)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60S)로 구성되는 혼변조 왜곡 신호상쇄기 회로(300S);

중 어느 하나를 혼변조 신호상쇄기 회로로 구비함을 특징으로 하는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포 워드 전력증폭기.

## 명세서

## 발명의 상세한 설명

#### 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 피드포워드 전력증폭기에 관한 것으로서, 종전의 신호상쇄기가 동작 주파수 전 대역에서 위상과 군속도 지연 정합을 동시에 만족시킬 수 없었던 문제점을 해결하여 위상과 군속도 지연 정합을 동시에 만족시킴으로써, 인가되는 두 입력단자의 신호들을 동일 군속도를 가지면서 광대역 신호 상쇄를 가능하게 하는 새로운 구조의 동일 군속도 지연 신호상쇄기 및 이를 적용한 광대역 피드포워드 전력증폭기에 관한 것이다.

언제, 어디서나, 누구든지 원하는 정보를 주고 받기를 원하는 통신의 진화는 이전보다 광대역 채널 대역폭과 선형화된 변복조 방식을 요구하게 되었다. 특히 최근 사용되고 있는 이동 통신 시스템은 한정된 주파수 자원의 효율적 사용을 위해 QPSK, QAM과 같은 선형 변조 방식 등을 사용한다. 이런 변조 방식들은 RF 신호의 최대 전력 대 평균 전력비가 크고, 포락선 변동이 심한 특성을 가지고 있어서 선형성이 좋은 전력증폭기를 필요로 한다.

그러나, 전력증폭기를 설계할 때에는 높은 효율과 높은 출력 전력을 얻기 위해 증폭기의 비선형 특성이 강한 포화 영역 근처에서 동작시키는 것이 일반적인데, 이로 말미암아 전력증폭기의 선형성이 나빠지게 된다. 이는 매우 좋은 선형성을 요구하는 통신 규격의 진화와 배치되는 것으로 매우 좋은 전력 효율과 선형성을 갖는 전력증폭기 설계 기술을 요구하게 된다.

고효율, 선형 전력증폭기(Linear Power Amplifier: LPA)를 구현하기 위해서는 고효율 전력증폭기에 선형화기를 부착하는 것으로 그 해결책이 될 것이다. 현재 여러 가지의 선형화 방법이 소개되고 있지만 개선 효과나 동작 대역폭등의 관점에서 볼 때에 실제로 적용 가능한 선형화 기법은 피크 전력 감쇄, 전치 왜곡 기법, 피드포워드 기법, 부궤환 기법, 디지털 전치 왜곡, EER(Envelope Elimination and Restoration) 등과 같은 방법들이 있다.

RF 전치왜곡 기법은 소형 및 경량으로 구현 가능하다는 측면에서 많이 사용되고 있지만, 비선형성 개선 효과는 피드포워드 기법에 미치지 못하며, 넓은 주파수 대역과 넓은 동작영역(Dynamic Range)에서 선형성 개선 효과를 갖게 하는 것이 쉽지 않다.

부궤환 기법은 동작 대역폭의 한계와 발진의 가능성으로 그 적용 범위에 한계가 있다.

디지털 전치왜곡기법은 기저대역의 신호에 전치왜곡을 함으로 RF 회로에서의 비선형성을 보상하는 것으로 부궤환 지연 시간과 RF 전력증폭기의 기억 효과(Memory Effect) 때문에 비교적 협대역에서만 양호한 선형화 효과를 얻고 있다.

여러 운용 채널 신호들을 동시에 증폭해야 하는 기지국 전력증폭기의 선형화 방법은 하나의 채널 신호를 증폭하는 단말기용 전력증폭기와 1~2개의 채널 신호를 증폭하는 기지국 전력증폭기의 선형화 방법보다 훨씬 어렵다. 그러나 통신망 운용자나 전력증폭기 제작자 입장에서는 광대역 선형성을 갖는 전력증폭기가 운용적인 측면이나 생산 수율적인 측면에서 훨씬 유리하다.

종전에도 피드포워드 전력증폭기의 동작 주파수 대역폭을 넓히기 위해 군속도 지연(Group Delay) 선로에 위상 왜곡이 있게 하는 방법을 시도하였다. 그러나 동작 대역폭이 넓지 않았고, 구현 자체도 쉽지 않았으며, 전력증폭기의 위상 왜곡 특성이 동작 조건에서 일정하지 않으므로 항상 일정한 선형화 개선 효과를 기대하기 힘든 단점이 있다.

이에 따라, 기지국 전력증폭기는 단말기에 비해 그 혼변조 왜곡 규격이 엄격하여 피드포워드 방식을 선호하여 사용하고 있다.

그러나 기지국에서는 특정 출력 레벨에서의 혼변조 왜곡 규격 뿐 만 아니라 출력 레벨 변화와 구동 전압 변화, 외부 온도 변화와 같은 환경 변화 조건에서도 항상 혼변조 왜곡 규격을 만족하는 자동적응 선형전력증폭기를 필요로 한다.

이러한 자동적응 선형전력증폭기를 구현하기 위해서 기존에는 피드포워드 방식의 선형화기를 설계할 때 파일럿 톤(Pilot Tone)들을 사용하거나 아날로그 제어 기법을 사용함으로써 성능 구현을 하였다.

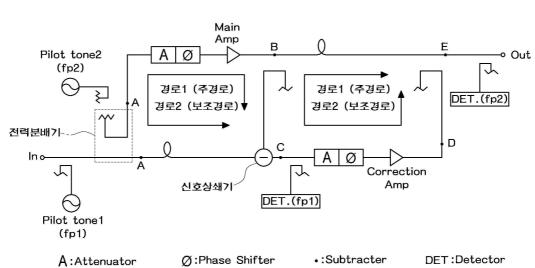

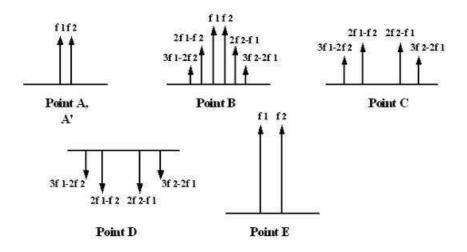

도 1a는 파일럿 톤들을 사용한 대표적인 피드포워드 방식 선형전력증폭기의 기본 회로도 이며, 도 1b는 피드포워드 선형 전력증폭기의 각 지점( $A\sim E$ )에서 얻어지는 신호 특성들을 보인 것이다.

그 동작 원리를 살펴보면 입력으로 인가된 2개의 반송파(f1)(f2)는 주 경로(또는 경로1)와 보조 경로(또는 경로2)로 전력 분배기에 의해 나누어진다. 주 경로에서는 전력증폭기(Main Amp)에 의해 입력반송파 신호들이 원하는 출력 레벨까지 증폭되며 이때 혼변조 왜곡 신호들도 함께 발생된다.

이러한 전력증폭기 출력 신호들의 일부를 추출하여 주 신호상쇄기 회로에 인가해 주고 보조 경로에서는 순수한 반송파만을 주 신호상쇄기 회로에 인가한다. 주 신호상쇄기 회로에서는 주 경로에서 인가된 반송파와 혼변조 왜곡 신호들 중에서 혼변조 왜곡 신호들만을 출력하게 된다.

주 신호상쇄기 회로에서 얻어진 혼변조 왜곡 신호 성분들은 진폭과 위상이 조정되어 혼변조 왜곡 신호상쇄기 회로에서 다시 주경로와 결합되어지는데 이때 가변 감쇠기(A)는 주 경로의 혼변조 왜곡 신호와 레벨을 맞추어 주기 위한 것이고, 가변 위상 변환기(Φ)는 주 경로에 다시 결합될 때 역(180°)의 위상을 맞추어 주기 위해 위상 조정을 하는 것이다.

결국 혼변조 왜곡 신호상쇄기 회로에 의해 주 경로에 다시 결합되기 직전의 혼변조 신호들(Point D의 신호들)은 주 경로에 있는 혼변조 왜곡 신호들과 크기는 같고 역위상이 되게 해 줌으로써 최종 출력은 혼변조 신호 성분들은 제거되고 증폭된 반송파(Point E의 신호)만이 남게 된다.

따라서 피드포워드 선형전력 증폭기는 신호 상쇄기를 중심으로 주 신호를 상쇄하는 루프와 혼변조 왜곡 신호를 상쇄하는 루프로 이루어졌으며, 각 루프는 동일한 입력 신호가 분기되어 각각 다른 경로(또는 경로1, 2)를 거친 후에 신호 상쇄기에서 합성되어 상쇄되는 전기적 합성 특성을 갖는다.

한편 도 1a에서 제1 파일럿 톤(Pilot tone 1)은 주 신호상쇄기 회로 출력 단에서 주 신호의 상쇄 정도를 감지할 목적으로 인가되고, 제2 파일럿 톤(Pilot tone 2)은 최종 출력 단에서 혼변조 왜곡 신호의 상쇄 정도를 감지할 목적으로 인가된다.

신호 검출기(DET)에 감지된 파일럿 톤들의 신호 레벨을 처리하여 감쇠기(A)와 위상변환기( $\Phi$ )를 조정함으로써 전력증폭기의 선형화 특성을 얻을 수 있다.

기본적으로 피드포워드 방식 선형화기는 동일한 동작원리를 갖는 두 개의 루프로 구성되어 있으며, 동일한 주파수 성분을 갖는 신호 성분들을 제거하는 것으로 성격을 정의할 수 있다.

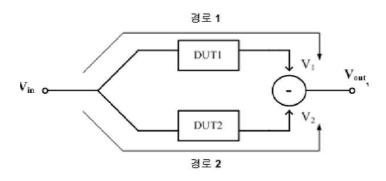

주 신호 상쇄 루프와 혼변조 신호 상쇄 루프로 이루어진 피드포워드 전력증폭기를 효과적으로 분석하기 위해 도 2와 같은 등가 루프를 제안할 수 있다.

도 2는 도 1a의 피드포워드 선형전력증폭기의 등가 루프를 나타낸 도면으로서, 입력단(In)으로 인가되는 입력 신호들  $(V_{\rm in}, j=1, 2, 3)$ 이 다음과 같다고 가정한다. 이때 각 입력 신호들의 중심주파수, 주파수 간격, 진폭은 각각  $\omega_{\rm o}$ ,  $\Delta\omega/2$ ,  $V_i$ 라고 설정한다.

수학식 1  $V_{in1} = V_{cos}(\omega_{o} - \Delta\omega/2)t$

$V_{in2} = V_i \cos \omega_0 t$

$V_{in3} = V_i \cos(\omega_0 + \Delta\omega/2)t$

경로1을 거쳐 거쳐 신호 상쇄기( $\Theta$ )에 인가되는 신호들이 중심주파수에서  $\phi$  만큼 위상 지연이 되고,  $au_1$  만큼 군속도 지연되었다면 신호상쇄기 입력 신호들( $V_{\mathrm{i}j}$ ,  $\not=1$ , 2, 3)은 다음과 같이 표현할 수 있다. 이때 경로1을 거친 입력 신호들의 진폭들은  $V_{\mathrm{1m}}$  이라 설정한다.

수학식 2  $V_{1,1} = V_{1,m} \cos[(\omega_0 - \Delta\omega/2)t - (\phi - \tau_1 \Delta\omega/2)]$

$V_{1.2} = V_{1m} \cos(\omega_0 t - \phi)$

$$V_{1,3} = V_{1,m} \cos[(\omega_0 + \Delta \omega/2)t - (\phi + \tau_1 \Delta \omega/2)]$$

여기에서  $\phi=\omega_{_0}\tau_{_1}$  이다. 한편, 경로2를 거쳐 신호 상쇄기 $(\Theta)$ 에 인가되는 신호들이 중심주파수에서  $\Theta$ 만큼 위상 지연이 되고,  $\tau_{_2}$ 만큼 군속도 지연되었다면 신호상쇄기 입력 신호들 $(V_{2,j},j=1,2,3)$ 은 다음과 같이 표현할 수 있다. 이때 경로2를 거친 입력신호들의 진폭들은  $V_{2m}$ 이라 설정한다.

수학식 3

$$V_{2,1}$$

= $V_{2m}$ cos[ $(\omega_{0}-\Delta\omega/2)t$ - $(\Theta$ - $\tau_{1}\Delta\omega/2)$ ]

$V_{2,2} = V_{2m} \cos(\omega_0 t - \theta)$

$V_{2.3} = V_{2m} \cos[(\omega_0 + \Delta\omega/2)t - (\Theta + \tau_1\Delta\omega/2)]$

여기에서  $\theta=\omega_0\tau_2=\phi+\pi+\Delta\theta$ 이며 경로1을 거쳐 신호상쇄기에 인가되는 신호들과 신호상쇄를 위한 역위상 조건을 가진다. 이때  $\Delta\theta$ 는 역위상 이탈 정도를 나타낸다. 경로 1과 2 사이에는 군속도 지연 시간의 차이( $\Delta\tau$ )가 존재한다고 가정하면다음과 같은 관계식을 가정할 수 있다.

수학식 4

$$\tau_2 = \tau_1 + \Delta \tau$$

최종 출력 단에서 중심 주파수의 신호가 완전히 상쇄되기 위해서는 동일 진폭 및 역위상 조건이 충족되어야 한다.

수학식 5

$$V_{1 m} = V_{2 m}$$

.

$\Theta - \phi |_{\Delta \Theta = 0} = \pi = \omega_{o} (\tau_{2} - \tau_{1}) = \omega_{o} \Delta \tau$

중심주파수에서 완전 신호 감쇄를 위한 두 경로간의 군속도 시간차는 다음과 주어진다.

수학식 6

$$\Delta \tau = \pi/\omega_0 = 1/2f_0$$

따라서, 완전 신호 감쇄를 위한 두 경로간의 군속도 시간차는 동작 주파수에 따라 달라짐을 알 수 있다. 이는 주파수 대역 폭을 갖는 신호에 대해서는 고정된 군속도 시간차로는 대역내 모든 주파수에서 역위상과 군속도 지연을 동시에 만족시킬 수 없음을 보이는 것이다.

중심주파수에서의 신호 상쇄기 출력단 신호 $(V_{out})$ 의 레벨은 다음과 같이 표현할 수 있다.

수학식 7

$$V_{out}^{2}=(V_{1.2}+V_{2.2})^{2}$$

$= [ \ V_{1\ m} \cos(\omega_{\ o}\ t - \phi) + \ V_{2\ m} \cos(\omega_{\ o}\ t - \theta) ]^2$

출력단 평균전력을 신호 벡터적으로 해석하여 표현하면,

수학식 8

$$P_{(V1,2+V2,2),avg} = V_{1m}^{2}/2 + V_{2m}^{2}/2 - V_{1m}V_{2m}\cos\Delta\theta$$

도 2에서 신호 제거기의 성능을 판별하기 위해 신호 제거기의 입력 신호 레벨에 대한 출력단 신호 레벨을 비교하면 다음과 같다.

## 수학식 9

P<sub>(V1,2+V2,2),avg</sub>/P<sub>V1,2,avg</sub>

$$= 1 + (V_{2\ m}/V_{1\ m})^2 - 2(V_{2\ m}/V_{1\ m})\cos\Delta\theta$$

$=1+a^2-2a\cos\Delta\theta$

여기서  $a=V_{2m}/V_{1m}=(V_{1m}+\Delta V_m)/V_{1m}$ 으로서 경로1 과 2를 거쳐 신호 상쇄기에 인가되는 신호들 간의 신호 레벨 불일치를 표현한다. 따라서 진폭과 위상의 불일치에 따른 상쇄정도(Cancellation performance: CP)를 표현하면 다음과 같다.

### 수학식 10

$C.P[dB]=10log(1+a^2-2acos\Delta\theta)$

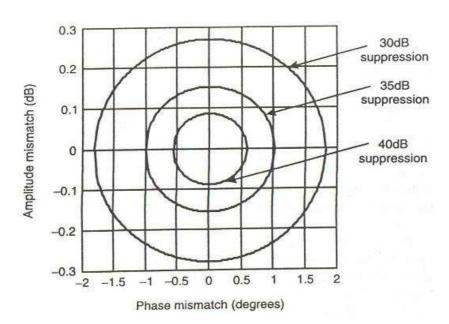

도 3은 진폭과 위상의 불일치에 따른 상쇄정도를 나타낸 것이다. 이제  $\omega_0 \pm (\Delta \omega/2)$ 에서의 최종 출력단 평균 전력을 다음과 같이 표현할 수 있다.

#### 수학식 11

$$P_{(V1,1+V2,1),avg} = V_{1m}^2/2 + V_{2m}^2/2 - V_{1m}V_{2m} [\sin\Delta\theta]$$

$\sin(\Delta \tau \Delta \omega/2) - \cos \Delta \theta \cos(\Delta \tau \Delta \omega/2)$

만약 중심 주파수에서 역위상으로 완전한 위상 정합이 되었다고 가정한다면, 중심 주파수가 아닌 다른 주파수에서 신호 제거기의 입력 신호 레벨에 대한 최종 출력 단 신호레벨을 비교하면 다음과 같다.

#### 수학식 12

=1+  $a^2$ -2 $a[\sin\Delta\theta\sin(\Delta\tau\Delta\omega/2)-\cos\Delta\theta\cos(\Delta\tau\Delta\omega/2)]$

만약 신호 제거기의 두 경로 입력신호 진폭이 정합(a=1)되고 중심 주파수에서 역위상 정합( $\Delta \theta$ =0)이 되었다고 추가로 가정하면 출력 단의 상쇄정도는 다음과 같이 나타낼 수 있다.

#### 수학식 13

C.P[dB]=10log{1-cos( $\Delta \tau \Delta \omega/2$ )]}+3

즉, 중심 주파수에서 완전하게 진폭과 역위상 정합이 만족되어도 동작주파수 대역 끝에서는 주파수 간격과 군속도 지연차로 인해 완전한 신호 상쇄가 일어나지 않음을 보이고 있다.

#### 발명이 이루고자 하는 기술적 과제

따라서, 상기한 문제점을 해결하기 위한 본 발명의 목적은 피드포워드 선형전력증폭기를 구현할 때 간과하고 있는 두 경로 사이의 군속도 지연 불일치에 의한 동작 대역폭의 한계점을 제시하고, 이를 해결할 수 있는 새로운 신호상쇄기를 제공하는 데 있다.

또한, 상기한 문제점을 해결하기 위한 본 발명의 다른 목적은 기존보다 동작대역을 확장시킬 수 있는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포워드 전력증폭기를 제공하는데 있다.

또한, 상기한 문제점을 해결하기 위한 본 발명의 또 다른 목적은 군속도 지연 정합과 함께 전력 및 역위상 정합을 동시에 만족시킴으로써 광대역 피드포워드 전력증폭기를 구현할 수 있는 새로운 형태의 신호상쇄기를 제공하는데 있다.

### 발명의 구성

상기와 같은 목적을 달성하기 위하여 본 발명은 결합단(11)과 전송단(12)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력 신호( $V_{in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 3dB-하이브리드 회로(10)와;

결합단(21)과 전송단(22)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가 받아서 격리단을 통하여 출력하는 제2 3dB-하이브리드 회로(20)와;

상기 제1 3dB-하이브리드 회로(10) 및 상기 제2 3dB-하이브리드 회로(20)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기를 주 신호상쇄기 회로(100)로 제공한다.

또한, 상기와 같은 목적을 달성하기 위하여 본 발명은 출력단(13)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호  $(V_{\rm in1})$ 를 인가받아서 격리단을 통하여 출력하는 제1 서큐레이터(10S)와;

출력단(23)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 서큐레이터(20S)와;

상기 제1 서큐레이터(10S) 및 상기 제2 서큐레이터(20S)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기 (50S);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기를 주 신호상쇄기 회로(100S)로 제공한다.

또한, 상기와 같은 목적을 달성하기 위하여 본 발명은 결합단(31)과 전송단(32)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 3dB-하이브리드 회로(30)와;

결합단(41)과 전송단(42)이 단락되며, 결합기(60)의 결합계수와 삽입손실의 차만큼 상기 제3 입력신호( $V_{in3}$ )에 대한 진폭 차와  $90^\circ$ 위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 3dB-하이브리드 회로(40)와;

상기 제3 3dB-하이브리드 회로(30) 및 상기 제4 3dB-하이브리드 회로(40)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기를 혼변조 왜곡 신호상쇄기 회로 (300)로 제공한다.

또한, 상기와 같은 목적을 달성하기 위하여 본 발명은 출력단(33)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호  $(V_{in3})$ 를 인가받아서 격리단을 통하여 출력하는 제3 서큐레이터(30S)와;

출력단(43)이 단락되며, 결합기(60S)의 결합계수와 삽입손실의 차만큼 상기 제3 입력신호( $V_{in3}$ )에 대해 진폭차와 90°위상 차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 서큐레이터(40S)와;

상기 제3 서큐레이터(30S) 및 상기 제4 서큐레이터(40S)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60S);로 구성됨을 특징으로 하는 동일 군속도 지연 신호상쇄기를 혼변조 왜곡 신호상쇄기 회로(300S)로 제공한다.

또한, 상기와 같은 목적을 달성하기 위하여 본 발명은 주 신호상쇄기 회로를 구비하는 피드포워드 전력증폭기에 있어서,

결합단(11)과 전송단(12)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호( $V_{in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 3dB-하이브리드 회로(10), 결합단(21)과 전송단(22)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 3dB-하이브리드 회로(20), 상기 제1 3dB-하이브리드 회로(10) 및 상기 제2 3dB-하이브리드 회로(20)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50)로 구성되는 주 신호상쇄기 회로(100)와;

결합단(31)과 전송단(32)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 3dB-하이브리드 회로(30), 결합단(41)과 전송단(42)이 단락되며, 결합기(60)의 결합계수와 삽입손실의 차만큼상기 제3 입력신호( $V_{in3}$ )에 대해 진폭차와 90°위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 3dB-하이브리드 회로(40), 상기 제3 3dB-하이브리드 회로(30) 및 상기 제4 3dB-하이브리드 회로(40)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60)로 구성되는 혼변조 왜곡 신호상쇄기 회로(300); 중 어느 하나를 주 신호상쇄기 회로로 구비함을 특징으로 하는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포워드 전력증폭기를 제공한다.

또한, 상기와 같은 목적을 달성하기 위하여 본 발명은 주 신호상쇄기 회로를 구비하는 피드포워드 전력증폭기에 있어서,

출력단(13)이 개방되며, 소정 진폭과 위상을 갖는 제1 입력신호( $V_{in1}$ )를 인가받아서 격리단을 통하여 출력하는 제1 서큐 레이터(10S), 출력단(23)이 단락되며, 상기 제1 입력신호( $V_{in1}$ )와 동일한 진폭과 위상을 갖는 제2 입력신호( $V_{in2}$ )를 인가받아서 격리단을 통하여 출력하는 제2 서큐레이터(20S), 상기 제1 서큐레이터(10S) 및 상기 제2 서큐레이터(20S)로부터 출력되는 신호들을 인가받아 출력하는 동위상 결합기(50S)로 구성되는 주 신호상쇄기 회로(100S)와;

출력단(33)이 개방되며, 소정 진폭과 위상을 갖는 제3 입력신호( $V_{in3}$ )를 인가받아서 격리단을 통하여 출력하는 제3 서큐 레이터(30S), 출력단(43)이 단락되며, 결합기의 결합계수와 삽입손실의 차만큼 상기 제3 입력신호( $V_{in3}$ )에 대해 진폭차와  $90^{\circ}$ 위상차를 갖는 제4 입력신호( $V_{in4}$ )를 인가받아서 격리단을 통하여 출력하는 제4 서큐레이터(40S), 상기 제3 서큐레이터(30S) 및 상기 제4 서큐레이터(40S)로부터 출력되는 신호들을 상호 격리단에 인가받아 출력하는 결합기(60S)로 구성되는 혼변조 왜곡 신호상쇄기 회로(300S); 중 어느 하나를 주 신호상쇄기 회로로 구비함을 특징으로 하는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포워드 전력증폭기를 제공한다.

이하 본 발명의 바람직한 실시 예를 첨부한 도면을 참조하여 상세히 설명한다. 우선 각 도면의 구성 요소들에 참조부호를 부가함에 있어서, 동일한 구성 요소들에 한해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 부호를 가지도록 하고 있음에 유의해야 한다. 그리고 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 공지 기능 및 구성에 대한 상세한 설명은 생략한다.

하나의 주파수 성분을 갖는 신호 성분을 피드포워드 등가 루프에 인가할 때 출력 단에서 완전한 신호 상쇄를 얻으려면 신호상쇄기의 두 입력 신호가 진폭과 역위상이 정합되어야 한다. 그러나 일정 주파수 대역을 갖는 입력 신호일 때에는 대역전체의 신호의 고른 신호 상쇄를 위해 진폭, 역위상, 군속도 지연이 동시에 정합이 이루어져야 하는데 상술한 종래 기술의문제점에서 살펴본 바와 같이 역위상과 군속도 정합이 동시에 이루어질 수 없음을 보이고 있다.

이것은 피드포워드 선형화 방식의 한계로, 비록 여타 선형화 방식보다 피드포워드 선형화 방식이 선형화 효과와 동작 대역 폭에서 우수하지만 광대역 피드포워드 전력증폭기 설계에도 한계가 있음을 나타낸다.

일반적으로 피드포워드 전력증폭기는 중심 주파수에서 <수학식 6>에 나타낸 정도의 군속도 지연을 만족하게 하고, 전체 주파수 대역에서 고른 진폭과 역위상 정합이 만족되게끔 조정하고 있다. 그러나, 신호상쇄기가 전력, 역위상, 군속도 지연 정합을 모두 만족시키면서 신호상쇄를 한다면 광대역 피드포워드 전력증폭기를 구현할 수 있을 것이다.

종전에는 두 입력 경로 중에 한 경로를 기준으로 하여 다른 경로의 신호에 대한 동작 조건 변화로 전력, 역위상, 군속도 지연의 동시 정합을 이루려 했기 때문에 전력, 역위상, 군속도 지연 정합을 모두 만족시키지 못하여 광대역 피드포워드 전력 증폭기를 구현할 수 없었다. 만약 두 경로의 동작 조건을 동시에 변화시킨다면 전력, 역위상, 군속도 지연의 동시 정합이가능할 것이다.

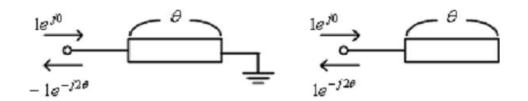

도 4는 종단이 단락 및 개방된 전송선로를 보인 것으로 이때 입력 단의 반사 신호들을 살펴보면 각각  $-1e^{-j2\theta}$ (또는  $1e^{-j}$   $(2\theta\pm\pi)$ ),  $1e^{-j2\theta}$ 이 된다. 따라서 입력 신호의 조건과 전송선로의 전기각에 관계없이 항상 역위상을 얻을 수 있다.

도 5는 본 발명에 따른 주 신호상쇄기 회로(100)를 보이고 있다. 동일 진폭과 위상을 갖는 두 입력 신호( $V_{in1}$ ,  $V_{in2}$ )는 결합 단(Coupling Port)(11)(21)과 전송단(Through Port)(12)(22)이 각각 개방 및 단락된 제1 3dB 하이브리드 회로(10) 및 제 2 3dB 하이브리드 회로(20)에 각각 인가된다. 인가된 신호는 상기 결합단(11)(21)과 전송단(12)(22)에서 각각 반사되어

격리단(Isolation Port)으로 전달되는데 이때 출력된 신호들은 상기 결합단(11)(21)과 전송단(12)(22)에서 각각 반사될 때에 전력, 역위상, 군속도 지연의 동시 정합 조건들을 만족하게 된다. 출력된 신호들을 동위상 결합기(50)에 인가하면 그 출력 단에서는 입력 신호가 완전히 상쇄된다.

이때, 3dB 하이브리드 회로를 사용한 것은 본 발명에 따른 주 신호상쇄기 회로와 입력 단에 존재하는 다른 회로와의 임피 던스 정합을 위한 것이다.

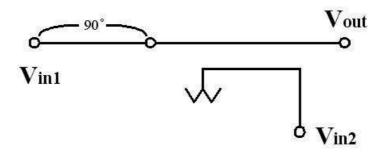

도 6은 본 발명의 다른 실시 예에 따른 다른 형태의 주 신호상쇄기의 회로(100S)를 보인 것으로 동작원리는 도 5와 거의 동일하다. 즉 동일 진폭과 위상을 갖는 두 입력 신호( $V_{\rm in1}$ )( $V_{\rm in2}$ )는 출력단(13)(23)이 각각 개방 및 단락된 제1 서큐레이터 (10S) 및 제2 서큐레이터(20S)에 인가되면 인가된 신호는 출력단(13)(23) 전송선로 종단에서 각각 반사되어 격리단으로 전달되는데 이때 격리단의 출력 신호들은 역위상, 군속도 지연의 동시 정합 조건들을 만족하게 된다. 출력된 신호들은 동위상 결합기(50S)에 인가하면 그 출력단에서는 입력 신호가 완전히 상쇄된다.

도 7은 본 발명에 따른 혼변조 왜곡 신호상쇄기 회로(300)를 보이고 있다. 결합기의 결합 계수와 삽입 손실의 차만큼 진폭차이가 나면서  $90^\circ$ 만큼 위상차를 갖는 두 입력 신호( $V_{in3}$ )( $V_{in4}$ )들은 결합단(31)(41)과 전송단(32)(42)이 각각 개방 및 단락된 제3 3dB 하이브리드 회로(30) 및 제4 3dB 하이브리드 회로(40)에 인가된다. 인가된 신호는 결합단(31)(41)과 전송단(32)(42)에서 각각 반사되어 격리단으로 전달되는데 이때 제3 3dB 하이브리드 회로(30) 및 제4 3dB 하이브리드 회로 (40)의 출력 신호들은 상기 결합단(31)(41)과 전송단(32)(42)에서 각각 반사될 때에 역위상, 군속도 지연의 동시 정합 조건들을 만족하게 된다. 따라서 결합기(60)의 출력 신호들은 전력, 역위상, 군속도 지연의 동시 정합 조건들을 만족하게 되어 출력 단에서는 입력 신호가 완전히 상쇄된다.

#### 삭제

도 8은 본 발명의 다른 실시 예에 따른 다른 형태의 혼변조 왜곡 신호상쇄기의 회로(300S)를 보인 것으로 동작원리는 도 7과 동일하며 3dB 하이브리드 대신에 서큐레이터로 대체한 것이다.

이하, 본 발명에 따른 동일 군속도 지연 신호상쇄기들을 이용한 피드포워드 전력증폭기의 실험과 그에 따른 결과를 설명한다.

본 발명에 따른 동일 군속도 지연 신호상쇄기들을 이용한 피드포워드 전력증폭기의 타당성을 보이기 위해 중심 주파수를 2.14GHz로 하는 주 증폭기, 에러 증폭기, 가변 감쇠기, 가변 위상변환기, 본 발명에 따른 주 신호상쇄기, 그리고 혼변조 왜 곡 신호상쇄기를 제작하였다.

또한, 종래 기술에 따른 피드포워드 전력증폭기와 특성 비교를 위해 주 신호 상쇄를 위한 Wilkinson 결합기와 혼변조 왜곡 신호 상쇄를 위한 10dB 결합기를 아울러 제작하였다. 비교의 편의성을 위해 대역폭은 ±100 MHz로 하여 특성 비교를 하였다.

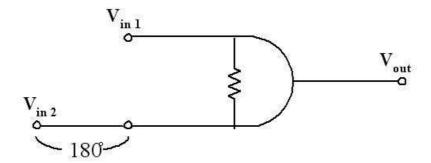

도 9는 일반적으로 많이 쓰이는 주 신호상쇄기 회로를 보인 것으로서, 한 입력 신호는 동위상 결합기인 Wilkinson 결합기의 한 입력 단에 연결되고, 다른 한 입력 신호는 중심 주파수에서 전기각이 180°인 전송선로를 거친 후에 Wilkinson 결합기의 다른 입력 단에 연결되어 출력되게 하였다.

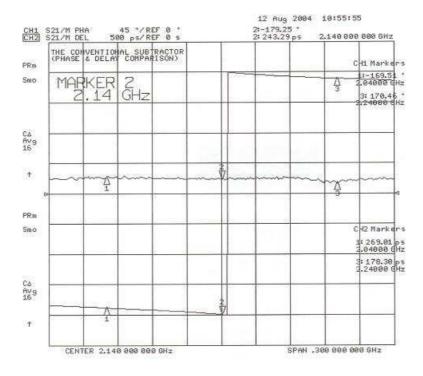

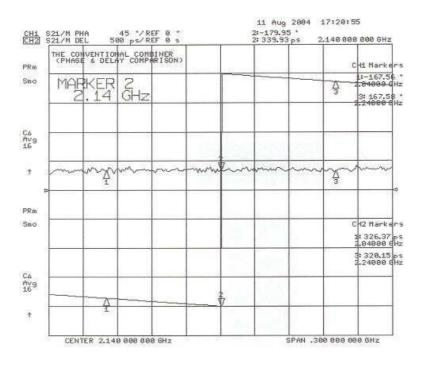

출력되는 신호간의 군속도 지연과 상호위상차를 비교한 것을 도 10에 나타내었다. 출력 결과를 비교해보면 전 주파수 대역에서 두 경로 간의 군속도 지연차는 약 0.24nsec 만큼 차이가 나고, 위상차는 -179.5°±10°이었다. 이는 두 입력 진호의 진폭이 정합되었다고 가정할 때, 동작 주파수 대역 끝에서는 약 -15.2dB의 신호 상쇄밖에 얻을 수 없음을 보인다.

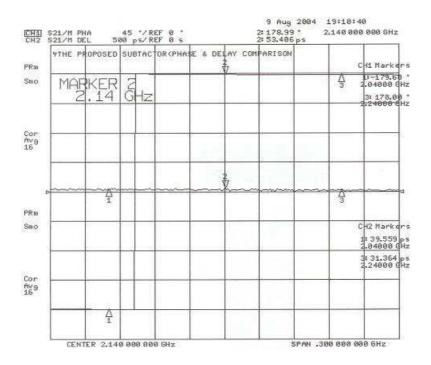

비교를 위해 도 5와 같은 주 신호상쇄기를 제작하고 그 특성을 도 11에 나타내었다. 사용된 3dB 하이브리드는 Anaren사의 S03A2500N1이다.

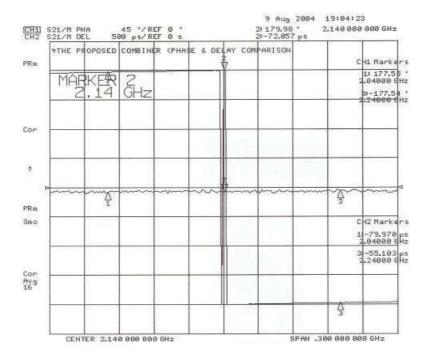

출력 결과를 비교해보면 전 주파수 대역에서 두 경로 간의 군속도 지연차는 거의 없고, 위상차는 -179.5°±1.2°이었다. 이는 두 입력 진호의 진폭이 정합되었다고 가정할 때, 동작 주파수 대역 끝에서는 약 -33.6dB의 신호 상쇄를 얻을 수 있으며 기존의 주 신호 감쇄기 보다 탁월한 신호 상쇄 효과를 얻을 수 있음을 보인다.

도 12는 일반적으로 많이 쓰이는 혼변조 왜곡 신호상쇄기 회로를 보인 것으로서, 10dB 결합기의 상호 격리 단에 두 입력 신호를 입력하되 역위상을 보장하기 위해 한 입력 단에 중심 주파수에서 90°인 전송선로를 부착하였다.

도 13에 나타낸 출력 결과를 비교해보면 전 주파수 대역에서 두 경로 간의 군속도 지연차는 약 0.34nsec 만큼 차이가 나고, 위상차는 -179.5°±12.5°이었다. 이는 두 입력 진호의 진폭이 정합되었다고 가정할 때, 동작 주파수 대역 끝에서는 약-13.3dB의 신호 상쇄밖에 얻을 수 없음을 보인다.

비교를 위해 도 7과 같은 혼변조 왜곡 신호상쇄기를 제작하고 그 특성을 도 14에 나타내었다. 도 12와 동일하게 10dB 결합기의 상호 격리 단에 3dB 하이브리드를 연결하였는데 사용된 3dB 하이브리드는 Anaren사의 S03A2500N1이다.

출력 결과를 비교해보면 전 주파수 대역에서 두 경로 간의 군속도 지연차는 거의 없고, 위상차는 180°±2.5°이었다. 이는 두 입력 진호의 진폭이 정합되었다고 가정할 때, 동작 주파수 대역 끝에서는 약 -27.2dB의 신호 상쇄를 얻을 수 있으며 기존의 혼변조 왜곡 신호 감쇄기 보다 탁월한 신호 상쇄 효과를 얻을 수 있음을 보인다.

제작된 주 증폭기와 에러 증폭기는 4단으로 구성되었으며, 동작 대역에서 44.7±0.3dB 의 이득과 -14dB 이하의 반사계수를 얻었다. 1dB 압축점은 28.7dBm 이었다.

또한, 가변 감쇠기와 가변 위상 변환기를 제작하였는데 3dB 하이브리드를 사용하여 반사형으로 구현하였는데 이는 광대역에서 좋은 반사특성을 얻기 위한 것이다. 가변 감쇄기는 15dB의 감쇠 범위를 가지며, 가변 위상변환기는 120°의 위상변환 범위를 가진다.

피드포워드 전력증폭기의 성능을 비교하기 위해 종래 기술에 따른 신호상쇄기를 적용한 경우와 본 발명에 따른 신호상쇄기를 적용한 피드포워드 전력증폭기를 제작하였다. 주 증폭기, 에러 증폭기, 가변감쇠기, 가변위상변환기 및 기타 회로들은 동일한 것을 사용하였다.

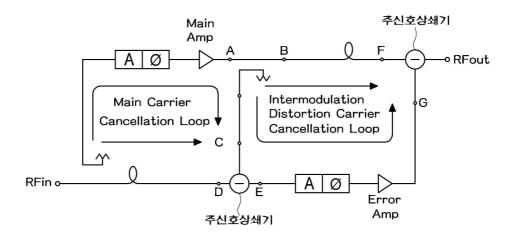

도 15는 측정에 사용된 피드포워드 전력증폭기의 블록도를 보이고 있다.

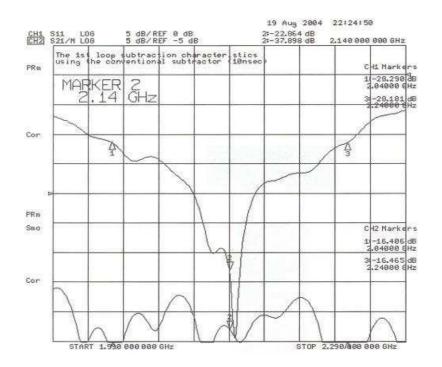

도 16은 종래 기술에 따른 주 신호상쇄기를 사용하여 주 신호 제거 루프의 신호 제거 특성을 회로망분석기(Network Analyzer)로 측정한 것으로 이때 도 15의 입력 단에 신호를 가하고, 점 B는 종단 저항으로 단락하였으며 점 E에서 측정하였다. 이때 점 C와 D는 주 신호 상쇄기의 두 입력 단자에 해당되며, 점 E는 주 신호상쇄기의 출력 단자에 해당된다.

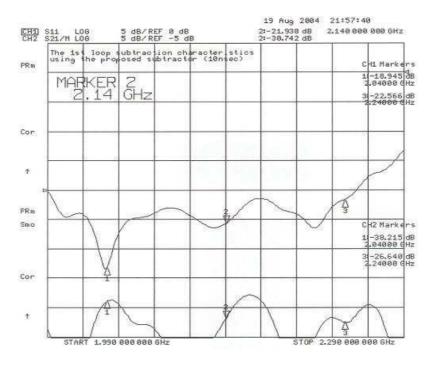

측정 결과  $\pm 100$ MHz 대역에서 16.4dB 이상의 신호 상쇄를 얻었다. 도 17은 본 발명에 따른 주 신호상쇄기를 사용한 주 신호 제거 투즈의 신호 제거 특성을 측정한 것으로  $\pm 100$ MHz 대역에서 26.3dB 이상의 신호 상쇄 효과를 얻었다. 특히 20dB 이상의 신호 상쇄를 얻는 대역폭이 300MHz 이상이 되었다.

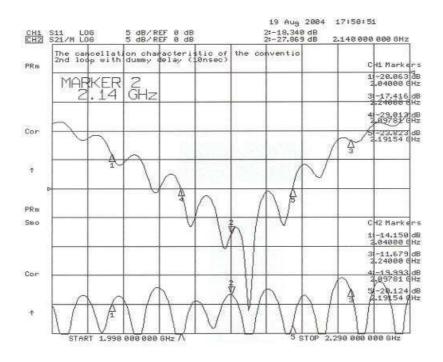

도 18은 종래 기술에 따른 혼변조 왜곡 신호상쇄기를 사용하여 혼변조 왜곡 신호 제거 루프의 신호 제거 특성을 회로망 분석기로 측정한 것으로 이때 도 15의 점 A에 신호를 가하고 점 D는 종단 저항으로 단락하였으며, 최종 출력 단에서 측정하였다. 이때 점 F와 G는 주 신호 상쇄기의 두 입력 단자에 해당된다. 측정 결과  $\pm 100~\mathrm{MHz}$  대역에서  $11.7\mathrm{dB}$  이상의 신호 상쇄를 얻었다.

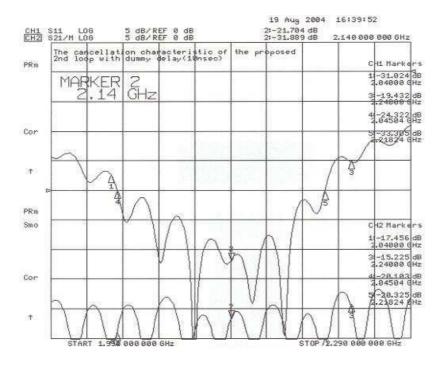

도 19는 본 발명에 따른 혼변조 왜곡 신호상쇄기를 사용한 혼변조 왜곡 신호 제거 루프의 신호 제거 특성을 측정한 것으로  $\pm 100 \mathrm{MHz}$  대역에서 15.2dB 이상의 신호 상쇄를 얻었다. 특히 20dB 이상의 신호 상쇄를 얻는 대역폭은 종래의  $94 \mathrm{MHz}$ 에서  $173 \mathrm{MHz}$ 로 확대되었다.

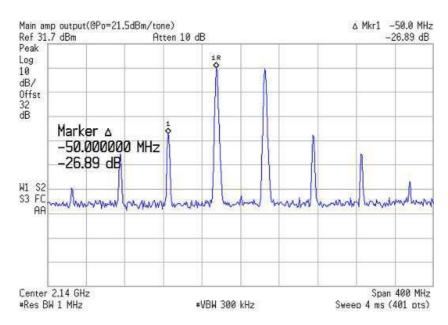

실제적인 혼변조 왜곡 신호의 제거 특성을 비교하기 위하여 제작된 피드포워드 전력증폭기의 입력에 2-tone 신호를 인가하였다. 입력 신호의 주파수는 각각 2115MHz와 2165MHz이며, 주파수 간격은 50MHz이다. 출력 레벨은 최종 단에서 17.52dBm/tone으로 (C/I)<sub>3rd</sub>=26.84dBc를 얻었다. 도 20은 선형화 회로를 가동하지 않았을 때의 출력 파형을 보인 것이다.

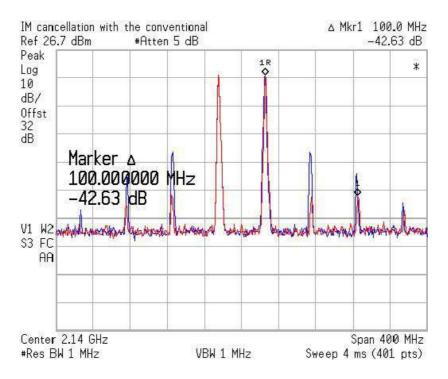

도 21은 종래 기술에 따른 신호감쇄기를 사용한 피드포워드 전력증폭기의 출력 특성으로  $(C/I)_{5th}$ =42.63dBc를 보이고 있다.

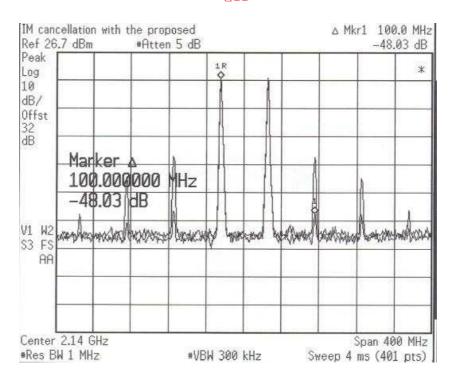

도 22는 본 발명에 따른 신호감쇄기를 사용한 피드포워드 전력증폭기의 출력 특성으로 (C/I)<sub>3rd</sub>=48.03dBc를 보이고 있다. 비록 (C/I)은 5.4dB 더 개선되었지만 더 넓은 대역에서 혼변조 왜곡 신호의 개선 특성을 보이고 있음을 확인할 수 있다.

상술한 바와 같이, 통신 방식의 진화는 선형화 변조 방식과 더 넓은 채널 대역폭을 요구하고 있다. 이는 기지국 전력증폭기로 하여금 더 높은 선형화 개선도와 더 넓은 대역의 비선형 신호 성분들의 효과적 제거 능력을 요구하게 된다.

본 발명은 기존의 피드포워드 방식 선형화기를 구현할 때 필요한 두 경로 사이의 군속도 지연시간차를 유도하였으며 이는 동작 주파수에 따라 달라짐을 확인하였다.

따라서 종래 기술에 따른 신호상쇄방법으로는 전력, 역위상, 그리고 군속도 지연 정합을 동시에 만족시키는 것이 불가능하게 되고, 광대역 피드포워드 전력증폭기를 구현할 때는 그 선형화 능력이 감소됨을 수식으로 확인하였다.

본 발명에 따른 새로운 형태의 신호상쇄회로는 원천적으로 전력, 역위상, 그리고 군속도 지연 정합을 동시에 만족시키는 것이 가능하며 따라서 광대역 피드포워드 전력증폭기의 구현에 적합하다.

현재 통신 서비스가 임박한 IMT-2000, 휴대 인터넷, OFDM을 이용한 무선랜(Wireless LAN) 등은 종전의 이동전화 서비스 보다 훨씬 넓은 서비스 주파수 대역을 가지므로 종전의 신호상쇄 기법을 이용한 피드포워드 선형화 방식으로는 선형화에 한계가 있으나 본 발명에 따른 신호상쇄기법을 적용한 피드포워드 전력증폭기는 충분히 선형화 효과를 얻을 수 있을 것으로 기대된다.

한편, 본 발명의 상세한 설명에서는 구체적인 실시 예를 들어 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능함은 물론이다. 그러므로 본 발명의 범위는 설명된 실시 예에 국한되어 정해져서는 안되며 후술하는 특허청구의 범위뿐 아니라 이 특허청구의 범위와 균등한 것들에 의해 정해져야 한다.

#### 발명의 효과

상술한 바와 같이 본 발명은 피드포워드 선형전력증폭기를 구현할 때 간과하고 있는 두 경로 사이의 군속도 지연 불일치에 의한 동작 대역폭의 한계를 극복할 수 있는 새로운 신호상쇄기를 제공하는 효과가 있다.

이에 따라, 본 발명은 기존보다 동작대역을 확장시킬 수 있는 동일 군속도 지연 신호상쇄기를 적용한 광대역 피드포워드 전력증폭기를 제공할 수 있는 효과가 있다.

또한, 본 발명은 군속도 지연 정합과 함께 전력 및 역위상 정합을 동시에 만족시킬 수 있는 새로운 형태의 신호상쇄기를 제공함으로써 광대역 피드포워드 전력증폭기를 구현할 수 있는 효과가 있다.

#### 도면의 간단한 설명

도 1a는 종래 기술에 따른 파일럿 톤들을 사용한 피드포워드 방식 선형 전력증폭기의 블록구성도,

도 1b는 종래 기술에 따른 피드포워드 방식 선형 전력증폭기의 동작원리를 나타낸 신호특성도,

도 2는 도 1a의 피드포워드 선형전력증폭기의 등가 루프를 나타낸 도면,

도 3은 도 2의 등가 루프의 경로간 진폭/위상 불일치에 따른 신호 상쇄도.

도 4는 단락 및 개방 전송선로의 반사 신호 비교,

도 5는 본 발명에 따른 주 신호상쇄기(Type 1)의 회로도,

도 6은 본 발명의 다른 실시 예에 따른 주 신호상쇄기(Type 2)의 회로도.

도 7은 본 발명에 따른 혼변조 신호상쇄기(Type 1)의 회로도,

도 8은 본 발명의 다른 실시 예에 따른 혼변조 신호상쇄기(Type 2)의 회로도,

도 9는 종래 기술에 따른 일반적인 주 신호상쇄기의 회로도,

도 10은 도 9의 종래 기술에 따른 주 신호상쇄기의 군속도 및 위상차 비교도,

도 11은 도 5의 본 발명에 따른 주 신호상쇄기의 군속도 및 위상차 비교도,

도 12는 종래 기술에 따른 일반적인 혼변조 왜곡 신호상쇄기 회로도,

도 13은 도 12의 일반적인 혼변조 왜곡 신호상쇄기의 군속도 및 위상차 비교도,

도 14는 도 7의 본 발명에 따른 혼변조 왜곡 신호상쇄기의 군속도 및 위상차 비교도,

도 15는 본 발명에 따른 주 신호상쇄기 및 혼변조 신호상쇄기를 적용한 피드포워드 증폭기의 블럭도,

도 16은 종래 기술에 따른 주 신호상쇄기를 사용한 주 신호 제거 루프의 출력 특성도,

도 17은 본 발명에 따른 주 신호상쇄기를 사용한 주 신호 제거 루프의 출력 특성도,

도 18은 종래 기술에 따른 혼변조 왜곡 신호상쇄기를 사용한 혼변조 왜곡 신호 제거 루프의 출력 특성도,

도 19는 본 발명에 따른 혼변조 왜곡 신호상쇄기를 사용한 혼변조 왜곡 신호 제거 루프의 출력특성도,

도 20은 피드포워드 선형화기가 동작하지 않을 때의 전력증폭기의 비선형 특성도,(@ $P_0$ =17.52dBm/tone)

도 21은 종래 기술에 따른 신호상쇄기를 사용한 피드포워드 전력증폭기의 출력 특성도, (@Po=17.52dBm/tone)

도 22는 본 발명에 따른 신호상쇄기를 사용한 피드포워드 전력증폭기의 출력 특성도. $(@P_o=17.52 dBm/tone)$

## 도면

## 도면1a

## 도면1b

## 도면2

## 도면5

도면9

도면11

도면13

도면14

도면15

A:Attenuator Ø:Phase Shifter ⊝:Signal Canceller

도면16